公共资源访问方法、装置、CPU、交换机及存储介质与流程

本发明涉及数据通信领域,具体而言,涉及一种公共资源访问方法、装置、cpu、交换机及存储介质。

背景技术:

1、“原子”是不可分割的意思,即执行期间不会被任何事件打断。比如cpu执行单条指令,一旦某条指令开始执行,到该指令结束之前,cpu都不会执行其他操作,相应地,原子操作也泛指一系列不会被打断的操作。

2、通过cpu的原子指令来实现原子操作依赖于cpu本身的指令集架构,目前大多数指令集架构都实现了load-reserved和store-conditional(以下简称lr/sc)的一对特殊指令来支持原子修改、原子交换、原子与和原子或等。

3、但不同指令集架构的cpu之间无法通过原子指令来实现原子操作的,例如,在以太网交换机中存在交换芯片内嵌cpu与芯片外部cpu同时访问公共资源的场景,由于芯片内嵌cpu一般是risc-v架构,芯片外部cpu可能是arm架构,此时,芯片内嵌cpu和芯片外部cpu无法在访问公共资源时实现原子操作。

技术实现思路

1、本发明提供了一种公共资源访问方法、装置、cpu、交换机和存储介质,其能够使不同指令集架构的cpu在访问公共资源时实现原子操作。

2、本发明的技术方案可以这样实现:

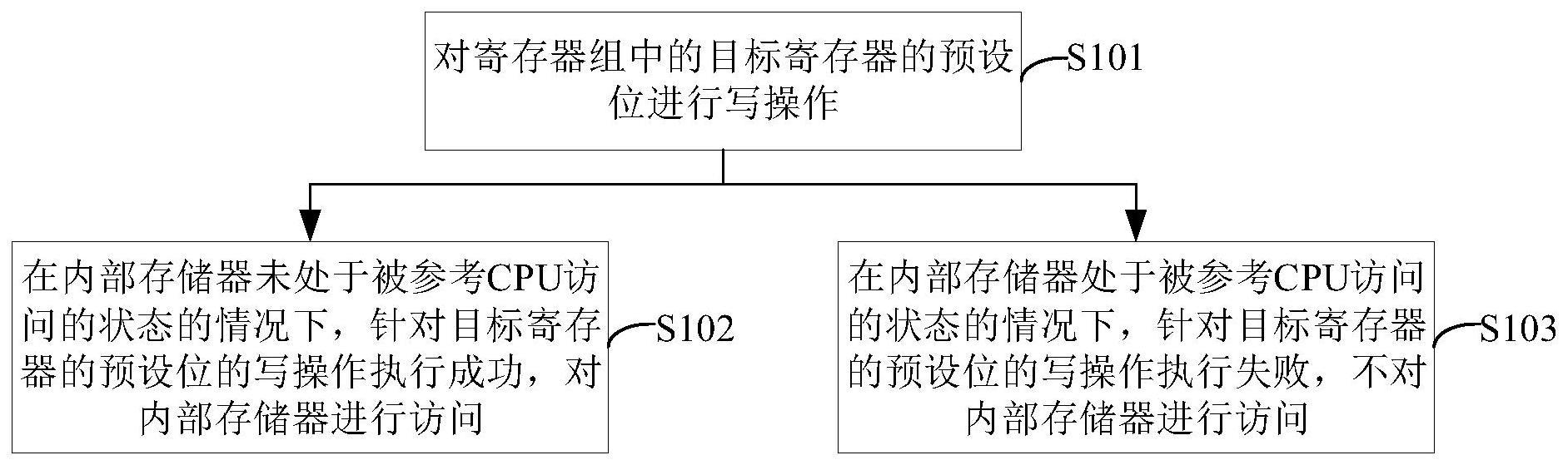

3、第一方面,本发明提供一种公共资源访问方法,应用于交换机中的目标cpu,所述交换机还包括参考cpu和交换芯片,所述交换芯片包括内部存储器和寄存器组,所述目标cpu和所述参考cpu均通过寄存器读写接口访问所述寄存器组,所述方法包括:

4、对所述寄存器组中的目标寄存器的预设位进行写操作;

5、在所述内部存储器未处于被所述参考cpu访问的状态的情况下,针对所述目标寄存器的预设位的写操作执行成功,对所述内部存储器进行访问;

6、在所述内部存储器处于被所述参考cpu访问的状态的情况下,针对所述目标寄存器的预设位的写操作执行失败,不对所述内部存储器进行访问。

7、可选地,在所述对所述寄存器组中的目标寄存器的预设位进行写操作之后,所述方法还包括:

8、对所述目标寄存器的预设位进行读操作;

9、根据读操作结果,判断针对所述目标寄存器的预设位的写操作是否执行成功;

10、若所述读操作结果表征所述内部存储器未处于被所述参考cpu访问的状态,则判定针对所述目标寄存器的预设位的写操作执行成功;

11、若所述读操作结果表征所述内部存储器处于被所述参考cpu访问的状态,则判定针对所述目标寄存器的预设位的写操作执行失败。

12、可选地,所述读操作结果是所述目标寄存器的预设位的值为预设写入值,则表征所述内部存储器未处于被所述参考cpu访问的状态;

13、所述读操作结果是所述目标寄存器的预设位的值为预设默认值,则表征所述内部存储器处于被所述参考cpu访问的状态。

14、可选地,所述目标cpu为通过总线与所述交换芯片连接的芯片外部cpu,所述参考cpu为安装在所述交换芯片上的芯片内嵌cpu,所述寄存器组包括第一寄存器和第二寄存器,所述第一寄存器为目标寄存器,所述对所述寄存器组中的目标寄存器的预设位进行写操作的步骤包括:

15、基于所述第二寄存器的预设位的值,对所述第一寄存器的预设位进行写操作,所述第二寄存器的预设位的值表征所述内部存储器是否处于被所述芯片内嵌cpu访问的状态。

16、可选地,所述基于所述第二寄存器的预设位的值,对所述第一寄存器的预设位进行写操作的步骤包括:

17、在所述第二寄存器的预设位的值为预设默认值的情况下,将所述第一寄存器的预设位的值修改为预设写入值,所述第二寄存器的预设位的值为预设默认值表征所述内部存储器未处于被所述芯片内嵌cpu访问的状态;

18、在所述第二寄存器的预设位的值为预设写入值的情况下,将所述第一寄存器的预设位的值保持为预设默认值,所述第二寄存器的预设位的值为预设写入值表征所述内部存储器处于被所述芯片内嵌cpu访问的状态。

19、可选地,所述目标cpu为安装在所述交换芯片上的芯片内嵌cpu,所述参考cpu为通过总线与所述交换芯片连接的芯片外部cpu,所述寄存器组包括第一寄存器和第二寄存器,所述第二寄存器为目标寄存器,所述预设位包括第一预设位和第二预设位,所述对所述寄存器组中的目标寄存器的预设位进行写操作的步骤包括:

20、基于所述第一寄存器的第一预设位的值和第二预设位的值,对所述第二寄存器进行写操作,其中,所述第一寄存器的第一预设位的值表征所述内部存储器是否处于被芯片外部cpu访问的状态,所述第一寄存器的第二预设位的值表征所述内部存储器是否处于被芯片外部cpu抢占的状态。

21、可选地,所述基于所述第一寄存器的第一预设位的值和第二预设位的值,对所述第二寄存器进行写操作的步骤包括:

22、对所述第一寄存器的第二预设位进行读操作,获取所述第一寄存器的第二预设位的值;

23、若所述第一寄存器的第二预设位的值为预设默认值,则基于所述第一寄存器的第一预设位的值,对所述第二寄存器的第一预设位进行写操作,其中,所述第一寄存器的第二预设位的值为预设默认值表征所述内部存储器未处于被芯片外部cpu抢占的状态;

24、若所述第一寄存器的第二预设位的值为预设写入值,则不对所述第二寄存器的第一预设位进行写操作,其中,所述第一寄存器的第二预设位的值为预设写入值表征所述内部存储器处于被芯片外部cpu抢占的状态。

25、可选地,所述基于所述第一寄存器的第一预设位的值,对所述第二寄存器的第一预设位进行写操作的步骤包括:

26、在所述第一寄存器的第一预设位的值为预设默认值的情况下,将所述第二寄存器的第一预设位的值修改为预设写入值,所述第一寄存器的第一预设位的值为预设默认值表征所述内部存储器未处于被芯片外部cpu访问的状态;

27、在所述第一寄存器的第一预设位的值为预设写入值的情况下,将所述第二寄存器的第一预设位的值保持为预设默认值,所述第一寄存器的第一预设位的值为预设写入值表征所述内部存储器处于被芯片外部cpu访问的状态。

28、可选地,所述方法还包括:

29、在结束对所述内部存储器的访问后,将所述目标寄存器的预设位的值从预设写入值修改为预设默认值,以使所述参考cpu能够访问所述内部存储器。

30、第二方面,本发明提供一种公共资源访问装置,应用于交换机中的目标cpu,所述交换机还包括参考cpu和交换芯片,所述交换芯片包括内部存储器和寄存器组,所述目标cpu和所述参考cpu均通过寄存器读写接口访问所述寄存器组,所述装置包括:

31、处理模块,用于对所述寄存器组中的目标寄存器的预设位进行写操作;

32、访问模块,用于:

33、在所述内部存储器未处于被所述参考cpu访问的状态的情况下,针对所述目标寄存器的预设位的写操作执行成功,对所述内部存储器进行访问;

34、在所述内部存储器处于被所述参考cpu访问的状态的情况下,针对所述目标寄存器的预设位的写操作执行失败,不对所述内部存储器进行访问。

35、第三方面,本发明提供一种cpu,其烧录有计算机程序,所述计算机程序被执行时实现如前述第一方面所述的公共资源访问方法。

36、第四方面,本发明提供一种交换机,其包括交换芯片以及如前述第三方面所述的cpu。

37、第五方面,本发明提供一种计算机可读存储介质,其存储有计算机程序,所述计算机程序被执行时实现如前述第一方面所述的公共资源访问方法。

38、相较于现有技术,本发明提供的一种公共资源访问方法,目标cpu通过对寄存器组中的目标寄存器的预设位进行写操作;在内部存储器未处于被参考cpu访问的状态的情况下,针对目标寄存器的预设位的写操作执行成功,对内部存储器进行访问;在内部存储器处于被参考cpu访问的状态的情况下,针对目标寄存器的预设位的写操作执行失败,不对内部存储器进行访问,从而使不同指令集架构的cpu在访问公共资源时实现原子操作。

39、为了使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

- 还没有人留言评论。精彩留言会获得点赞!