一种FPGA仿真验证方法、装置、电子设备及存储介质与流程

本技术涉及通信,尤其涉及一种fpga仿真验证方法、装置、电子设备及存储介质。

背景技术:

1、随着通信技术的发展,在数据通信芯片设计上,大规模、高速度、高复杂度的数据通信芯片设计越来越多,尤其是基于现场可编程门阵列(field programmable gatearray,fpga)实现的大规模逻辑设计,完成的逻辑功能既多又复杂。通常为了保证fpga设计投入实际应用的可靠性,在投入使用前需要对设计好的fpga进行仿真验证。

2、现有技术中,在对fpga进行仿真验证时,通常开发相应的测试激励模块对fpga的逻辑功能模块进行仿真验证。

3、例如,参阅图1所示,为一种测试激励模块仿真的示意图,逻辑功能模块a有一个输入端和输出端,仿真时需要开发一个测试激励模块a对逻辑功能模块a进行仿真测试,测试激励模块a的输出对应逻辑功能模块a的输入,测试激励模块a的输入则对应逻辑功能模块a的输出,测试激励模块a产生的测试数据经过逻辑功能模块a处理之后通过逻辑功能模块a的输出端把处理结果传递到测试激励模块a的输入端,测试激励模块a通过比较接收到的处理结果与预期结果是否一致判断逻辑功能模块a的功能是否正常。

4、然而,由于测试激励模块只是对相应的逻辑功能模块进行仿真验证,未对fpga在实际的物理设备上的功能进行仿真验证,因此,与实际物理设备的硬件接口相关的问题在仿真验证过程中难以暴露,仿真验证结果与在实际的物理设备上测试的结果不贴切,导致仿真结果不准确。

5、另外,由于每开发一个逻辑功能模块就需要开发对应的测试激励模块对逻辑功能模块进行仿真验证,因此,测试激励模块的开发工作量比逻辑功能模块更大,使得fpga仿真验证的执行效率较低。

6、有鉴于此,相关技术下,fpga仿真验证的准确度和执行效率,有待进一步提高。

技术实现思路

1、本技术实施例提供一种fpga仿真验证方法、装置、电子设备及存储介质,以提高fpga仿真验证的准确度和执行效率。

2、本技术实施例提供的具体技术方案如下:

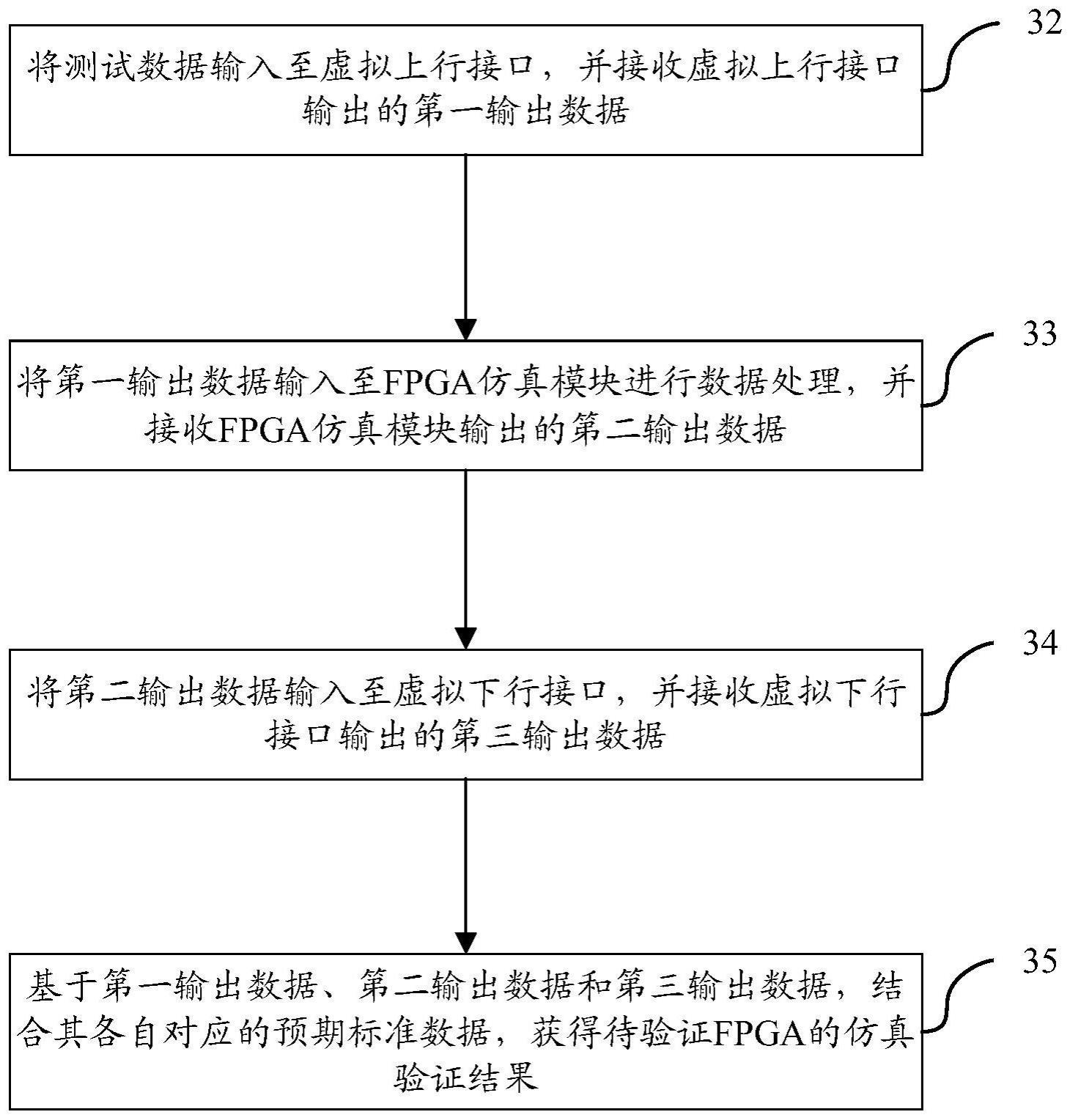

3、第一方面,提供一种fpga仿真验证方法,包括:

4、将测试数据输入至虚拟上行接口,并接收虚拟上行接口输出的第一输出数据,其中,虚拟上行接口是对目标物理设备的上行硬件接口进行虚拟化处理获得的,目标物理设备是待验证fpga的待安装设备;

5、将第一输出数据输入至fpga仿真模块进行数据处理,并接收fpga仿真模块输出的第二输出数据,其中,fpga仿真模块是对待验证fpga的目标逻辑功能的仿真;

6、将第二输出数据输入至虚拟下行接口,并接收虚拟下行接口输出的第三输出数据,其中,虚拟下行接口是对目标物理设备的下行硬件接口进行虚拟化处理获得的;

7、基于第一输出数据、第二输出数据和第三输出数据,结合其各自对应的预期标准数据,获得待验证fpga的仿真验证结果。

8、可选的,将测试数据输入至虚拟上行接口之前,所述方法还包括:

9、将目标物理设备的上行硬件接口的物理资源,抽象成对应的第一逻辑资源,并基于第一逻辑资源,生成上行硬件接口对应的虚拟上行接口;

10、将目标物理设备的下行硬件接口的物理资源,抽象成对应的第二逻辑资源,并基于第二逻辑资源,生成下行硬件接口对应的虚拟下行接口。

11、可选的,将测试数据输入至虚拟上行接口,包括:

12、基于虚拟上行接口的属性信息,确定传输测试数据的物理接口;

13、将测试数据通过物理接口转发至虚拟上行接口。

14、可选的,将第一输出数据输入至fpga仿真模块进行数据处理,并接收fpga仿真模块输出的第二输出数据,包括:

15、对待验证fpga的逻辑开发程序进行编译,获得逻辑开发程序对应的逻辑动态链接库;

16、调用fpga仿真工具对逻辑动态链接库进行加载;

17、将第一输出数据输入至fpga仿真工具,获得fpga仿真工具采用逻辑动态链接库处理后输出的第二输出数据。

18、可选的,基于第一输出数据、第二输出数据和第三输出数据,结合其各自对应的预期标准数据,获得待验证fpga的仿真验证结果,包括:

19、若第一输出数据、第二输出数据和第三输出数据,满足以下至少一个条件,则确定待验证fpga的仿真验证结果为异常:

20、第一输出数据与其对应的第一标准数据不一致;

21、第二输出数据与其对应的第二标准数据不一致;

22、第三输出数据与其对应的第三标准数据不一致。

23、可选的,确定待验证fpga的仿真验证结果为异常之后,所述方法还包括:

24、若仿真验证结果表征虚拟上行接口异常,则基于保存的虚拟上行接口对应的第一调试信息,确定虚拟上行接口相关的异常问题;

25、若仿真验证结果表征目标逻辑功能异常,则基于fpga仿真工具保存的仿真波形图,确定目标逻辑功能中的异常问题;

26、若仿真验证结果表征虚拟下行接口异常,则基于保存的虚拟上行接口对应的第二调试信息,确定虚拟下行接口相关的异常问题。

27、第二方面,提供一种fpga仿真验证装置,包括:

28、第一处理模块,用于将测试数据输入至虚拟上行接口,并接收虚拟上行接口输出的第一输出数据,其中,虚拟上行接口是对目标物理设备的上行硬件接口进行虚拟化处理获得的,目标物理设备是待验证fpga的待安装设备;

29、第二处理模块,用于将第一输出数据输入至fpga仿真模块进行数据处理,并接收fpga仿真模块输出的第二输出数据,其中,fpga仿真模块是对待验证fpga的目标逻辑功能的仿真;

30、第三处理模块,用于将第二输出数据输入至虚拟下行接口,并接收虚拟下行接口输出的第三输出数据,其中,虚拟下行接口是对目标物理设备的下行硬件接口进行虚拟化处理获得的;

31、生成模块,用于基于第一输出数据、第二输出数据和第三输出数据,结合其各自对应的预期标准数据,获得待验证fpga的仿真验证结果。

32、可选的,将测试数据输入至虚拟上行接口之前,所述装置还包括预处理模块,所述预处理模块用于:

33、将目标物理设备的上行硬件接口的物理资源,抽象成对应的第一逻辑资源,并基于第一逻辑资源,生成上行硬件接口对应的虚拟上行接口;

34、将目标物理设备的下行硬件接口的物理资源,抽象成对应的第二逻辑资源,并基于第二逻辑资源,生成下行硬件接口对应的虚拟下行接口。

35、可选的,将测试数据输入至虚拟上行接口时,所述第一处理模块还用于:

36、基于虚拟上行接口的属性信息,确定传输测试数据的物理接口;

37、将测试数据通过物理接口转发至虚拟上行接口。

38、可选的,将第一输出数据输入至fpga仿真模块进行数据处理,并接收fpga仿真模块输出的第二输出数据时,所述第二处理模块还用于:

39、对待验证fpga的逻辑开发程序进行编译,获得逻辑开发程序对应的逻辑动态链接库;

40、调用fpga仿真工具对逻辑动态链接库进行加载;

41、将第一输出数据输入至fpga仿真工具,获得fpga仿真工具采用逻辑动态链接库处理后输出的第二输出数据。

42、可选的,基于第一输出数据、第二输出数据和第三输出数据,结合其各自对应的预期标准数据,获得待验证fpga的仿真验证结果时,所述生成模块还用于:

43、若第一输出数据、第二输出数据和第三输出数据,满足以下至少一个条件,则确定待验证fpga的仿真验证结果为异常:

44、第一输出数据与其对应的第一标准数据不一致;

45、第二输出数据与其对应的第二标准数据不一致;

46、第三输出数据与其对应的第三标准数据不一致。

47、可选的,确定待验证fpga的仿真验证结果为异常之后,所述装置还包括确定模块,所述确定模块用于:

48、若仿真验证结果表征虚拟上行接口异常,则基于保存的虚拟上行接口对应的第一调试信息,确定虚拟上行接口相关的异常问题;

49、若仿真验证结果表征目标逻辑功能异常,则基于fpga仿真工具保存的仿真波形图,确定目标逻辑功能中的异常问题;

50、若仿真验证结果表征虚拟下行接口异常,则基于保存的虚拟上行接口对应的第二调试信息,确定虚拟下行接口相关的异常问题。

51、第三方面,提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现上述第一方面任一项所述方法的步骤。

52、第四方面,提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述第一方面任一项所述方法的步骤。

53、第五方面,提供一种计算机程序产品,所述计算机程序产品包括计算机程序,所述计算机程序存储在计算机可读存储介质中;当电子设备的处理器从计算机可读存储介质读取所述计算机程序时,所述处理器执行所述计算机程序,使得所述电子设备执行上述第一方面任一项所述方法的步骤。

54、本技术实施例中,服务设备首先将数据设备构造的测试数据输入至虚拟上行接口,并接收虚拟上行接口输出的第一输出数据,其中,虚拟上行接口是对目标物理设备的上行硬件接口进行虚拟化处理获得的,目标物理设备是待验证fpga的待安装设备,再将第一输出数据输入至fpga仿真模块进行数据处理,并接收fpga仿真模块输出的第二输出数据,其中,fpga仿真模块是对待验证fpga的目标逻辑功能的仿真,然后,将第二输出数据输入至虚拟下行接口,并接收虚拟下行接口输出的第三输出数据,其中,虚拟下行接口是对目标物理设备的下行硬件接口进行虚拟化处理获得的,最后,基于第一输出数据、第二输出数据和第三输出数据,结合其各自对应的预期标准数据,获得待验证fpga的仿真验证结果。这样,在确定待验证fpga的仿真验证结果时,不仅对待验证fpga的目标逻辑功能进行仿真,而且对待验证fpga的待安装设备的上行硬件接口和下行硬件接口进行仿真,提高了仿真验证的准确度,并且调用数据设备构造的测试数据,不需要开发大量的激励测试模块,简化了测试数据输入的过程,从而提高了fpga仿真验证的执行效率。

- 还没有人留言评论。精彩留言会获得点赞!