一种LIF神经元电路

本发明涉及脉冲神经网络领域,具体涉及一种可以延迟连接多突触的lif神经元电路。

背景技术:

1、脉冲神经网络作为第三代神经网络,相比传统的人工神经网络更加贴近于生物的工作原理,它能够有效的模仿生物神经元之间的连接与通信。在脉冲神经网络中神经元作为一个基本单元,它能够接收脉冲信号并激发出尖峰脉冲,是实现复杂时空信息处理的重要基础。lif(泄漏积分和点火)神经元以生物神经元为模型,能够有效的模仿生物神经元的信息传递特性,例如动作电位尖峰的有或无尖峰、累积发放和不应期等。然而由于生物神经元的激发脉冲较为复杂,以传统器件构建的lif神经元电路不仅需要大量元器件,而且lif神经元激发尖峰脉冲与生物神经元激发脉冲相似度较低。这就导致了实用性低下,功耗高,不利于电路集成等问题。忆阻器作为一种新型元器件,它在外部施加电压时,忆阻值会随着施加电压的方向增大或减小。由于忆阻器阻值变化的非线性能更好的贴近生物神经元离子通道开关阻值变化的非线性,因此基于忆阻器的lif神经元电路能有效降低lif电路的复杂度,这将有利于提高类脑芯片的集成密度,降低类脑芯片的功耗。然而当前大多忆阻lif神经元激发尖峰脉冲宽度、峰值强弱和不应期时长不可调控,这种神经元在脉冲神经网络中限制了信息的编码方式和传递速率,导致了神经计算灵活性大幅下降。

2、在生物神经网络中,神经突触是神经元之间在功能上发生联系的部位,是两个神经元之间信息传递的关键。单个神经元连接多突触时的传递速率和传递尖峰信息的幅度大小可能因突触类型、神经递质类型、受体类型、突触前和突触后的机制等多种因素影响。而在仿生神经元相关的硬件研究中,研究人员往往忽略了单个神经元连接多突触时因多种因素导致的不同神经突触上传递尖峰信息不同,这就导致仿生神经元的激发脉冲特性与生物神经元存在差异。由于这种差异在以此构建的神经网络中可能会导致模型的行为与真实生物神经网络的行为不同,从而导致神经网络预测准确性下降。

技术实现思路

1、针对与现有技术的不足,本发明的目的在于发明一种激发尖峰和不应期范围调控且可延迟连接多突触的忆阻lif神经元电路。

2、为了实现上述技术目的,本发明的技术方案是,

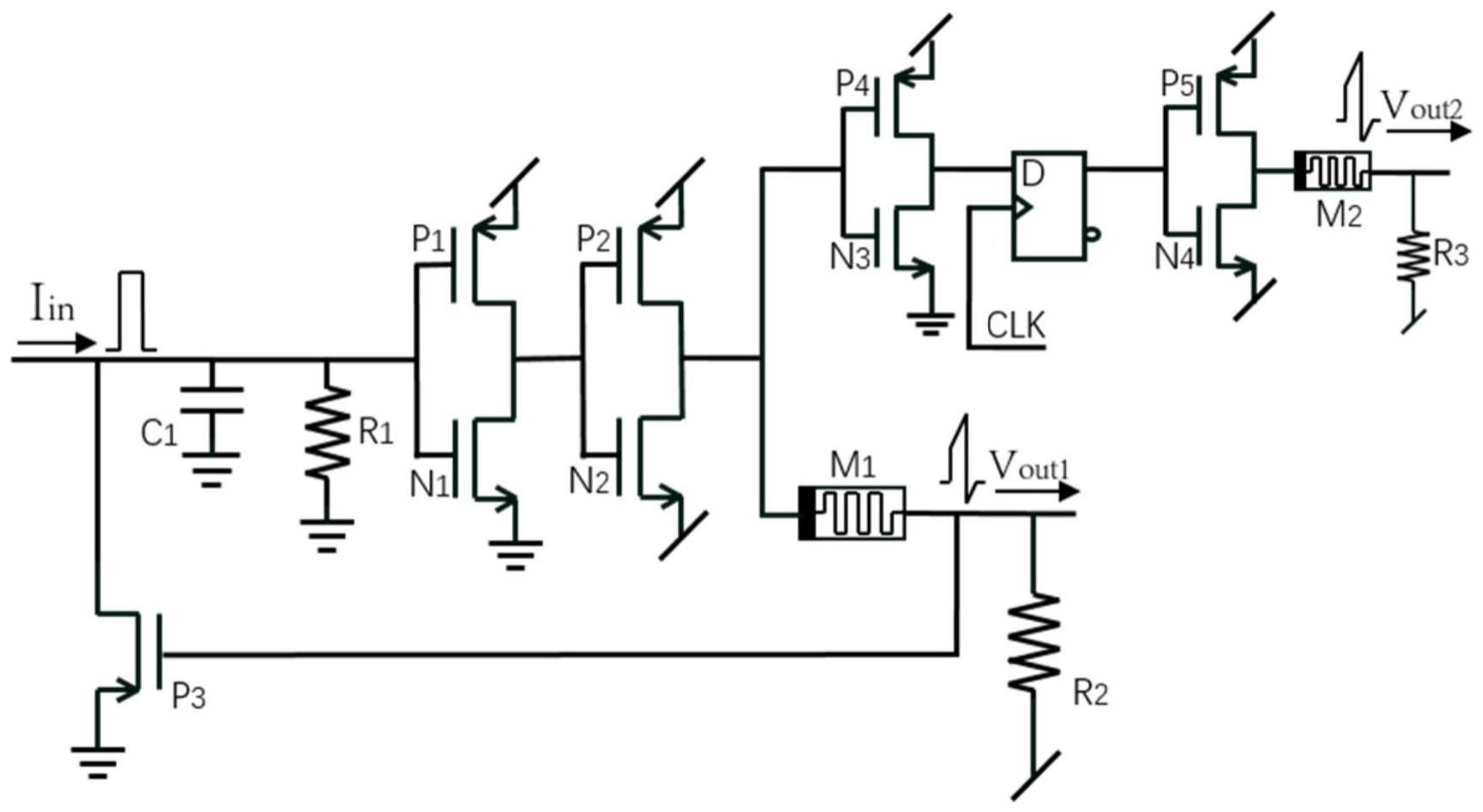

3、一种lif神经元电路,包括电流输入端和至少两个电压输出端,以及膜电位积累单元、波形整形单元、泄漏单元、脉冲产生单元、不应期单元和数量与电压输出端相等的延迟单元。其中各个电压输出端均产生尖峰脉冲输出但产生的延时均不相同。

4、电流输入端连接膜电位积累单元的输入端,并通过膜电位积累单元来对输入电流进行积分。

5、膜电位积累单元的输出端通过泄漏单元连接波形整形单元的输入端,以通过泄漏单元向波形整形单元输出达到预设阈值的电压。

6、波形整形单元的输出端分别连接至脉冲产生单元和各个延迟单元,以输出由膜电位积累单元产生的模拟信号转换并整形后得到的数字信号。

7、脉冲产生单元基于接收的数字信号产生尖峰脉冲输出,脉冲产生单元的输出端作为电压输出端中的一个,且同时还连接到不应期单元以控制不应期单元。

8、不应期单元的输出端连接到膜电位积累单元的输入端,以对膜电位积累单元的输入进行通断控制。

9、各个延迟单元基于接收的数字信号产生延时不同的尖峰脉冲输出,且各个延迟单元输出端均作为电压输出端。

10、所述的一种lif神经元电路,所述的膜电位积累单元包括电容,所述的电容的一端连接于电流输入端和波形整形单元之间,另一端接地。所述的泄漏单元包括泄漏电阻,所述的泄漏电阻的一端连接于膜电位积累单元和波形整形单元之间,另一端接地。

11、所述的一种lif神经元电路,所述的波形整形单元包括一级反相器和二级反相器,所述的一级反相器的输入端通过泄漏单元连接至膜电位积累单元,并在接收到预设阈值的电压后马上由输出正电压转为输出0电压,从而向二级反相器输出在正电压和0之间转换的方波信号。二级反相器在接收到0电压后马上由输出负电压转换为输出正电压,从而输出在负电压和正电压之间转换的方波信号。

12、所述的一种lif神经元电路,所述的一级反相器包括第一nmos管和第一pmos管。所述的第一nmos管和第一pmos管的栅极互相连接,并通过泄漏单元连接至膜电位积累单元。第一nmos管的漏极和第一pmos管的漏极相连。第一nmos管的源极接地,第一pmos管的源极接正电压。

13、所述的二级反相器包括第二nmos管和第二pmos管。所述的第二nmos管和第二pmos管的栅极互相连接,并通过泄漏单元连接至膜电位积累单元。第二nmos管的漏极和第二pmos管的漏极相连。第二nmos管的源极接负电压,第二pmos管的源极接正电压。

14、所述的一种lif神经元电路,所述的脉冲产生单元包括脉冲单元忆阻器和脉冲单元电阻,所述的脉冲单元忆阻器的输入端连接至波形整形单元的输出端,脉冲单元忆阻器的输出端作为电压输出端,并连接至不应期单元。所述的脉冲单元电阻的一端连接至脉冲单元忆阻器的输出端,另一端连接至正电压。

15、所述的一种lif神经元电路,所述的不应期单元包括不应期单元pmos管,所述的不应期单元pmos管的栅极连接至脉冲产生单元,漏极连接至电流输入端和膜电位积累单元之间,源极接地。

16、所述的一种lif神经元电路,所述的延迟单元包括依次连接的第一反相器、d触发器、第二反相器、延迟单元忆阻器和延迟单元电阻。

17、所述的第一反相器的输入端连接至波形整形单元的输出端,并在接收到预定阈值的电压后马上由输出正电压转为输出0电压,从而向d触发器输出在正电压和0之间转换的方波信号。

18、所述的d触发器的输出端连接至第二反相器,且d触发器的clk端控制延迟时间,在延迟时间达到后来向第二反相器输出0电压。

19、所述的第二反相器在接收到0电压后马上由输出负电压转换为输出正电压,从而输出在负电压和正电压之间转换的方波信号至延迟单元忆阻器的输入端。

20、延迟单元忆阻器的输出端作为电压输出端。

21、延迟单元电阻的一端连接至脉冲单元忆阻器的输出端,另一端连接至正电压。

22、所述的一种lif神经元电路,所述的第一反相器包括nmos管和pmos管。所述的nmos管和pmos管的栅极互相连接,并连接至波形整形单元的输出端。nmos管的漏极和pmos管的漏极相连并连接至d触发器的输入端。nmos管的源极接地,pmos管的源极接正电压。

23、所述的第二反相器包括nmos管和pmos管。所述的nmos管和pmos管的栅极互相连接,并连接至d触发器的输出端。nmos管的漏极和pmos管的漏极相连并连接至延迟单元忆阻器的输入端。nmos管的源极接负电压,pmos管的源极接正电压。

24、本发明的技术效果在于,忆阻lif神经元通过忆阻器阻值的变化和mos管的开关特性实现了激发尖峰脉冲宽度、峰值电位大小和不应期时长可调控。本发明的忆阻lif神经元通过d触发器对信号延迟,实现了能够连接多突触并激发延迟尖峰脉冲。此种忆阻lif神经元更为接近生物神经元信息的传递机制,提高了神经突触的信息传递的多样性和稳定性。在脉冲神经网中为速率编码和脉冲幅度编码方式提供了灵活高效的时空信息,在以脉冲神经网络对图像分类,语音识别等应用中,神经元对输入图像、语音的不同特征编码时有很大优势。另外,所用元器件数目少,利于高密度集成和降低成本。

- 还没有人留言评论。精彩留言会获得点赞!