一种基于BCD工艺的数模混合集成电路的设计方法与流程

本发明涉及数据处理,尤其涉及一种基于bcd工艺的数模混合集成电路的设计方法。

背景技术:

1、bcd是一种单片集成工艺技术,这种技术能够在同一芯片上制作双极型晶体管(bipolar junction transistor),cmos器件和dmos器件。bcd工艺不仅综合了双极型器件高跨导、强负载驱动能力和cmos器件集成度高、低功耗的优点,而且集成进了开关速度很快的dmos功率器件。由于dmos器件同时具有高速和大电流能力的特性,耐压通常也较高,因而用bcd工艺制造的电源管理芯片能工作在是高频、高压和大电流下,是制造高性能电源芯片的理想工艺。采用bcd工艺制造的单片集成芯片还可以提高系统性能,节省电路的封装费用,并具有更好的可靠性。

2、中国专利公开号:201710851519.4。公开了一种高压工艺集成电路方法。在p型衬底上注入形成n型深阱注入形成p阱;在高阻区域形成热氧化层;对器件表面进行杂质的整体注入,调整n型深阱区硅表面掺杂的浓度,进而调整pmos阈值电压达到设计要求;淀积栅极热氧化层及多晶硅,进行低掺杂注入,调节多晶硅电阻值达到高值电阻的阻值要求,完成多晶硅栅极及高值电阻的刻蚀成型,完成cmos器件中pmos和nmos的源漏极注入;淀积层间介质,刻蚀接触孔并制作电极、引出。由此可见,上述方案存在以下问题:仅单一的对电路进行设计并没有考虑到具体应用时用户端多需要的具体需求,无法在设计过程中针对对应参数的调节以使设计的电路能够适用于对应输出电压需求的环境,针对数模混合集成电路的设计效率低。

技术实现思路

1、为此,本发明提供一种基于bcd工艺的数模混合集成电路的设计方法。用以克服现有技术中无法使设计的数模混合集成电路能够适用于对应输出电压需求的环境导致针对数模混合集成电路的设计效率低的问题。

2、为实现上述目的,本发明提供一种基于bcd工艺的数模混合集成电路的设计方法,包括:

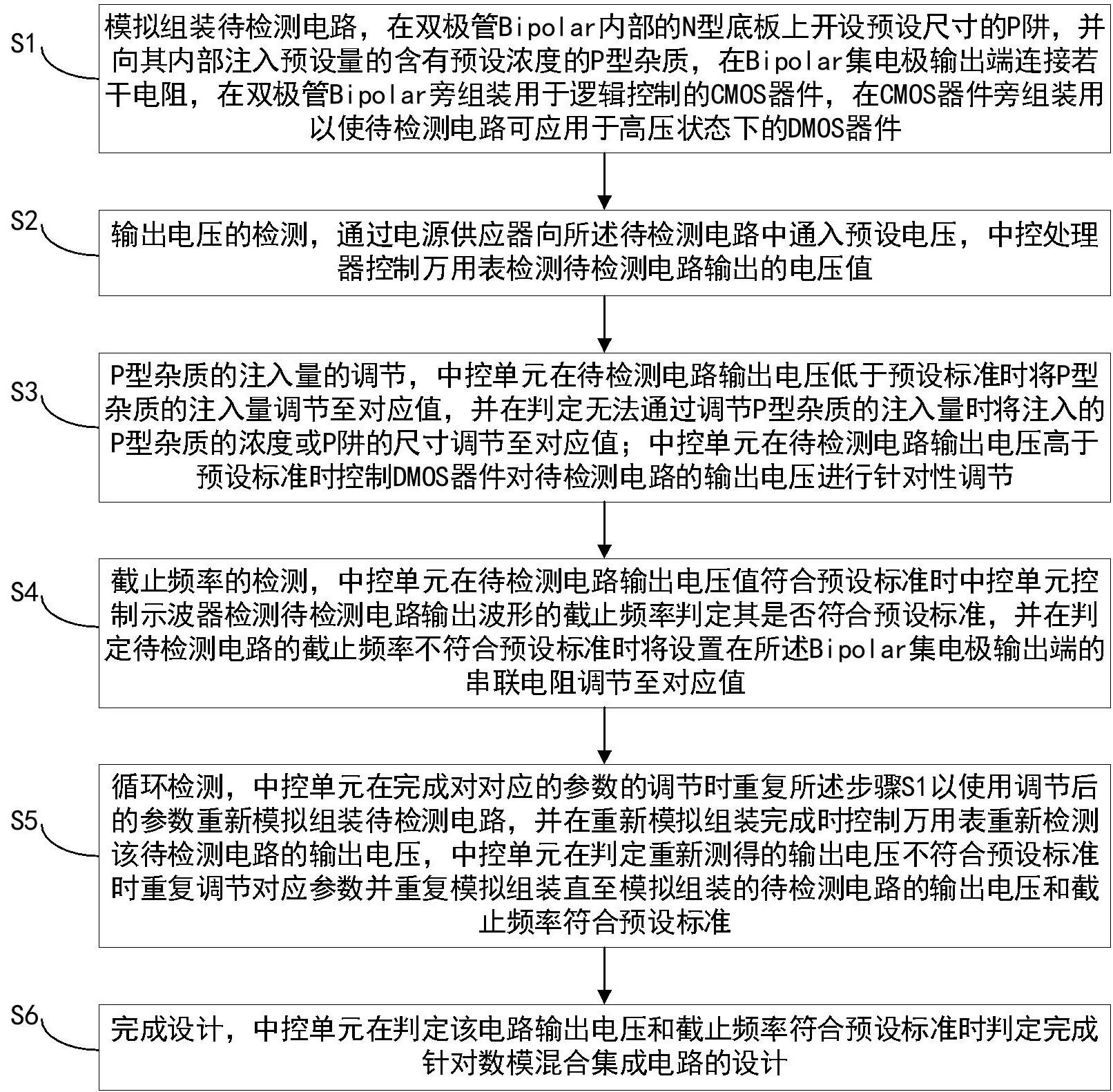

3、步骤s1,模拟组装待检测电路,按照高压bcd工艺在双极管bipolar内部的n型底板上开设预设尺寸的p阱,并向其内部注入预设量的含有预设浓度的p型杂质,在bipolar集电极输出端连接若干电阻,在双极管bipolar旁组装用于逻辑控制的cmos器件,在cmos器件旁组装用以使待检测电路可应用于高压状态下的dmos器件。

4、步骤s2,输出电压的检测,通过电源供应器向所述待检测电路中通入预设电压,中控处理器控制万用表检测待检测电路输出的电压值;

5、步骤s3,p型杂质的注入量的调节,中控单元在所述待检测电路输出电压低于预设标准时将所述p型杂质的注入量调节至对应值,并在判定无法通过调节p型杂质的注入量时将注入的p型杂质的浓度或所述p阱的尺寸调节至对应值;所述中控单元在所述待检测电路输出电压高于预设标准时控制所述dmos器件对所述待检测电路的输出电压进行针对性调节;

6、步骤s4,截止频率的检测,所述中控单元在所述待检测电路输出电压值符合预设标准时中控单元控制示波器检测待检测电路输出波形的截止频率判定其是否符合预设标准,并在判定待检测电路的截止频率不符合预设标准时将设置在所述bipolar集电极输出端的串联电阻调节至对应值;

7、步骤s5,循环检测,所述中控单元在完成对对应的参数的调节时重复所述步骤s1以使用调节后的参数重新模拟组装待检测电路,并在重新模拟组装完成时控制所述万用表重新检测该待检测电路的输出电压,中控单元在判定重新测得的输出电压不符合预设标准时重复调节对应参数并重复模拟组装直至模拟组装的待检测电路的输出电压和截止频率符合预设标准;

8、步骤s6,完成设计,所述中控单元在判定该电路输出电压和截止频率符合预设标准时判定完成针对数模混合集成电路的设计。

9、进一步地,在所述步骤s2中,所述中控单元将所述万用表测得的所述待检测电路的输出电压记为u,并根据u判定该待检测电路的输出电压是否符合预设标准,中控单元中设有第一预设标准电压u1和第二预设差标准电压u2,其中u1<u2,

10、若u≤u1,所述中控单元判定所述待检测电路的输出电压低于预设标准,中控单元计算所述第一预设标准电压u1与待检测电路的输出电压u的差值△u,并根据△u将所述p型杂质的注入量调节至对应值,设定△u=u1-u;

11、若u1<u≤u2,所述中控单元判定所述待检测电路的输出电压符合预设标准,中控单元控制所述示波器检测待检测电路输出波形的截止频率fc判定其是否符合预设标准,若不符合则将所述bipolar集电极输出端的串联电阻阻值r调节至对应值;

12、若u>u2,所述中控单元判定该电路处于高压状态,控制所述dmos器件对电路进行控制以将所述待检测电路的输出电压调节至对应值。

13、进一步地,所述中控单元在第一预设条件根据所述第一预设标准电压u1与待检测电路的输出电压u的差值△u将所述p型杂质的注入量q调节至对应值,所述中控单元中设有第一预设电压差值△u1、第二预设电压差值△u2、第一预设注入量调节系数α1、第二预设注入量调节系数α2以及第三预设注入量调节系数α3,其中,△u1<△u2,1<α1<α2<α3<1.9,

14、若△u≤△u1,所述中控单元使用α1将所述p型杂质的注入量q调节至对应值;

15、若△u1<△u≤△u2,所述中控单元使用α2将所述p型杂质的注入量q调节至对应值;

16、若△u>△u2,所述中控单元使用α3将所述p型杂质的注入量q调节至对应值;

17、所述中控单元将使用αk调节后的p型杂质的注入量记为q’,其中,k=1,2,3,设定q’=q×αk;

18、所述第一预设条件为所述待检测电路的输出电压值u小于所述第一预设标准电压u1。

19、进一步地,所述中控单元在第二预设条件将调节后的p型杂质的注入量q’与中控单元内设置的预设临界注入量qmax进行比对以判定是否将所述p型杂质的浓度或所述p阱的尺寸调节至对应值,

20、若q’<qmax,所述中控单元使用调节后的p型杂质的注入量设置为q’并重新模拟组装所述待检测电路;

21、若q’>qmax,所述中控单元使用调节后的p型杂质的注入量设置为qmax,中控单元计算q’与qmax的差值△qs并根据△qs将所述p型杂质的浓度或所述p阱的尺寸调节至对应值,设定△qs=qmax-q’,中控单元中还设有预设注入量差值△qx,

22、若△qs≤△qx,所述中控单元判定将所述p型杂质的浓度调节至对应值,中控单元计算所述△qx与所述△qs的差值△qxs,并根据△qxs将所述p型杂的质浓度调节至对应值;

23、若△qs>△qx,所述中控单元通过△qx和△qs的差值将所述p阱尺寸调节至对应值;

24、所述第二预设条件为所述中控单元判定该电路不符合预设标准且需将所述p型杂质的注入量调节至q’。

25、进一步地,所述中控单元在第三预设条件根据预设注入量差值△qx与△qs的差值△qxs将所述p型杂质的浓度c调节至对应值,所述中控单元中设有第一预设浓度差值△qxsa、第二预设浓度差值△qxsb、第一预设浓度调节系数β1、第二预设浓度调节系数β2以及第三预设浓度调节系数β3,其中,△qxsa<△qxsb,1<β1<β2<β3<3.2,

26、若△qxs≤△qxsa,所述中控单元使用β1将所述p型杂质的浓度c调节至对应值;

27、若△qxsa<△qxs≤△qxsb,所述中控单元使用β2将所述p型杂质的浓度c调节至对应值;

28、若△qxs>△qxsb,所述中控单元使用β3将所述p型杂质的浓度c调节至对应值;

29、所述中控单元将使用βr调节后的p型杂质的浓度记为c’,其中,r=1,2,3,设定c’=c×βr;

30、所述第三预设条件为预设临界注入量qmax与调节后的所述p型杂质的注入量q’之间的差值△qs小于预设注入量差值△qx。

31、进一步地,所述中控单元在第四预设条件根据△qs和预设注入量差值△qx的差值△qsx将所述p阱尺寸s调节至对应值,所述中控单元中设有第一预设尺寸差值△qsxa、第二预设尺寸差值△qsxb、第一预设尺寸调节系数f1、第二预设尺寸调节系数f2以及第三预设尺寸调节系数f3,其中,△qsxa<△qsxb,1<f1<f2<f3<1.3,

32、若△qsx≤△qsxa,所述中控单元使用f1将所述p阱尺寸s调节至对应值;

33、若△qsxa<△qsx≤△qsxb,所述中控单元使用f2将所述p阱尺寸s调节至对应值;

34、若△qsx>△qsxb,所述中控单元使用f3将所述p阱尺寸s调节至对应值;

35、所述中控单元将使用fω调节后的p阱尺寸记为s’,其中,ω=1,2,3,设定s’=s×fω;

36、所述第四预设条件为预设临界注入量qmax与调节后的所述p型杂质的注入量q’之间的差值△qs大于预设注入量差值△qx。

37、进一步地,所述中控单元在第五预设条件将s’与中控单元内设置的预设临界p阱尺寸smax进行比对,

38、若s’<smax,所述中控单元使用s’作为所述bipolar的p阱尺寸;

39、若s’≥smax,所述中控单元控制使用smax作为所述bipolar的p阱尺寸,并将p型杂质的浓度调节至对应值;

40、所述中控单元将调节后的p型杂质的浓度调节记为cb’,设定cb’=1.2×cb,其中,cb为p型杂质的初始浓度;

41、所述第五预设条件为所述中控单元判定预设临界注入量与调节后的所述p型杂质的注入量之间的差值大于预设注入量差值并判定需将p阱尺寸调节至s’。

42、进一步地,所述中控单元在第六预设条件将所述待检测电路输出波形的截止频率fc与中控单元内设置的预设截止频率fa对比,

43、若fc<fa,所述中控单元判定该电路截止频率符合预设标准,并判定完成针对数模混合集成电路的设计;

44、若fc>fa,所述中控单元通过万用表检测所述bipolar集电极输出端的串联电阻阻值r并根据r、fc和fa将其更改至对应值r’,设定r’=fa×r/fc+w×fc其中,w与为权重系数,设定w=0.2ω/hz;

45、所述第六预设条件为所述中控单元判定所述待检测电路的输出电压符合预设标准。

46、进一步地,所述中控单元在完成对所述电阻的调节后重新模拟组装所述待检测电路,并控制所述万用表重新检测该待检测电路输出电压,中控单元在判定重新测得的输出电压不符合预设标准时重复调节对应参数并重复模拟组装直至模拟组装的待检测电路的输出电压和截止频率符合预设标准;

47、进一步地,所述dmos器件输出达到临界值时,若输出电压仍不符合标准,中控单元发出警报提醒工作人员变更dmos器件。

48、与现有技术相比,本发明的有益效果在于,本发明通过使用中控单元在判定待检测电路输出的电压值不符合预设标准时根据待检测电路输出的电压值将所述p型杂质的注入量或p阱尺寸调节至对应值,并在判定待检测电路输出的电压值符合预设标准时根据所述待检测电路输出波形的截止频率fc是否将所述bipolar集电极输出端的串联电阻阻值r调节至对应值,通过针对对应参数的调节以使通过本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境,从而有效提高了本发明所述方法针对数模混合集成电路的设计效率。

49、进一步地,本发明所述中控单元根据待检测电路的输出电压u与中控单元中预设的第一预设标准电压u1和第二预设标准电压u2的比对结果判定是否调节所述p型杂质的注入量q、检测待检测电路输出波形的截止频率fc或控制所述dmos器件调节待检测电路的输出电压,通过根据不同的比对结果将对应的参数调节至对应值,能够有效保证通过调节对应参数以避免待检测电路输出电压不符合预设标准的情况发生,在进一步保证本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境的同时,进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

50、进一步地,所述中控单元中还设有若干预设电压差值,所述中控单元在所述待检测电路输出的电压u满足u小于等于u1时计算u1与u的差值并根据该差值与各预设电压差值的比对结果将所述p型杂质的注入量q调节至对应值,本发明通过根据待检测电路的实际输出电压值将所述p型杂质的注入量调节至对应值,能够有效保证将待检测电路输出的电压值增加至对应区间,在进一步保证本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境的同时,进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

51、进一步地,所述中控单元中还设有预设临界注入量qmax,所述中控单元在判定需将p型杂质的注入量调节至q’时将q’与qmax进行比对并根据比对结果判定是否将所述p型杂质的的浓度调节至对应值,本发明通过设置临界注入量,能够有效避免调节后p型杂质注入量过多导致后续待检测电路在运行时溢出的p型杂质对待检测电路产生影响的情况发生,同时,本发明在q’>qmax时根据q’与qmax的差值△qs将p型杂质的浓度c调节至对应值,能够进一步避免调节后p型杂质注入量过多导致后续待检测电路在运行时溢出的p型杂质对待检测电路产生影响的情况发生,在进一步保证本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境的同时,进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

52、进一步地,所述中控单元在判定无法通过调节p型杂质的注入量或浓度以将所述待检测电路的输出电压调节至对应值时根据△qs与预设注入量差值△qx的差值将所述p阱的尺寸调节至对应值,在进一步避免调节后p型杂质注入量过多导致后续待检测电路在运行时溢出的p型杂质对待检测电路产生影响的情况发生的同时,保证本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境,并进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

53、进一步地,本发明所述中控单元中还设有预设临界p阱尺寸smax,中控单元在判定需将所述p阱的尺寸调节至s’时将s’与smax进行比对并在s’>smax时对p型杂质的浓度进行进一步调节,通过对对p型杂质浓度的进一步调节,能够有效避免p阱尺寸过大或p型杂质注入量过多导致后续待检测电路在运行时溢出的p型杂质对待检测电路产生影响的情况发生,在进一步保证本发明设计的数模混合集成电路能够适用于对应输出电压需求的环境的同时,进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

54、进一步地,本发明所述中控单元中还设有预设截止频率fa,中控单元在判定所述待检测电路输出的电压符合预设标准时检测检测电路输出波形的截止频率fc以对待检测电路是否设计完成进行判定并在判定fc<fa时将所述bipolar集电极输出端的串联电阻阻值调节至对应值,本发明通过对待检测电路输出的电压以及输出波形的截止频率进行检测以对待检测电路是否设计完成进行多重标准的判定,在保证本发明设计的数模混合集成电路能够适用于对应需求的环境的同时,进一步提高了本发明所述方法针对数模混合集成电路的设计效率。

- 还没有人留言评论。精彩留言会获得点赞!