单环形振荡器的真随机数发生器电路结构

本发明涉及电路的,尤其涉及一种单环形振荡器的真随机数发生器电路结构。

背景技术:

1、随机数发生器已成为安全通信和信息系统的基本组成部分,它在广泛的加密应用中发挥着关键作用,包括认证协议、数据加密和随机填充。此外,软件的数值模拟和随机实验也需要大量高质量的随机数。然而伪随机数生成器(pseudo-random numbergenerators,prngs)依赖于确定性的数学模型以及初始状态(也称为种子),这使得它们容易被攻破。相比之下,真随机数发生器(ture random number generators,trngs),它从非确定性的物理过程中提取随机性,如固态电路中普遍存在的电噪声,从理论上不可被预测。通过使用专用的芯片电路收集基于电子噪声的熵源就可以产生具有高随机性的原始比特流。这些比特流通常会输入后续的后处理模块,以进一步优化其随机性。

2、现有技术方法中已经公开了多种类型的真随机数发生器,如目前公开的一种真随机数发生器直接放大由热噪声引起的器件电压波动,并与给定的阈值电压进行比较,得到随机的输出比特。虽然热噪声是一种理想的具有均匀功率谱的熵源,但电路中必需的放大器和具有超宽带宽的比较器使其难以被利用在低能耗且小面积的方案中。基于混沌映射的trng可以产生高度稳定的随机比特,但模数转换器使整个结构变得复杂,同时输出吞吐率也限制在0.27mbps。目前公开的另一种真随机数发生器基于亚稳态的trng设计,如使用sram单元和交叉耦合电路的设计,可以实现高达3gbps的超高吞吐率;然而,为最大程度减小生产、电压-温度(process,voltage and temperature,pvt)变化的影响,基于亚稳态的trng设计中往往需要一个复杂的校准电路,从而导致面积和功率的显著增加。因此,现有技术中的真随机数发生器存在无法兼顾吞吐速率及电路功耗的问题。

技术实现思路

1、本发明实施例提供了一种单环形振荡器的真随机数发生器电路结构,旨在解决现有技术中的真随机数发生器存在无法兼顾吞吐速率及电路功耗的问题。

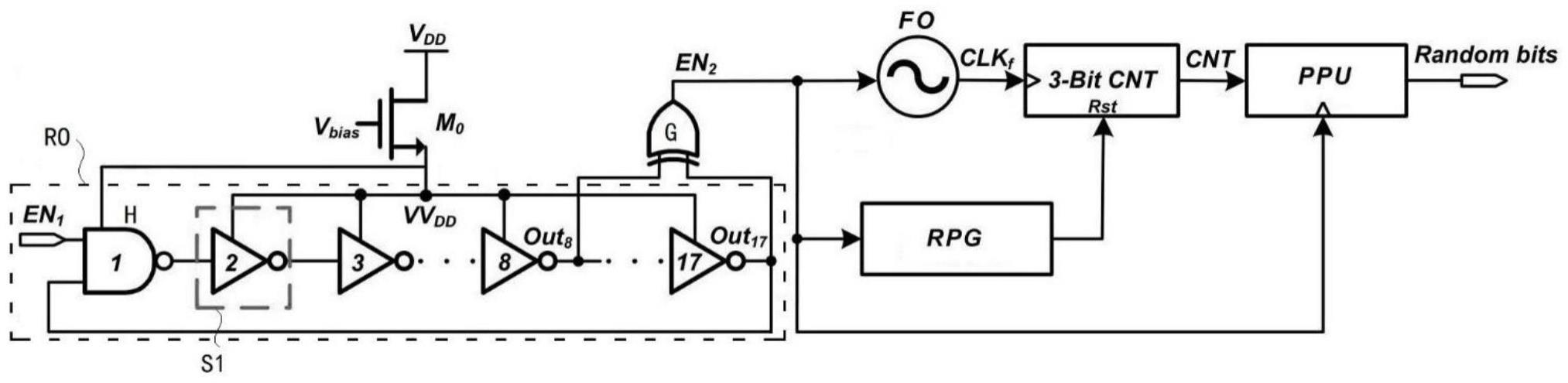

2、本发明实施例公开了一种单环形振荡器的真随机数发生器电路结构,其特征在于,所述电路结构包括环形振荡器、快速振荡电路、计数器、本征晶体管、异或门、复位信号发生电路及后处理电路;所述环形振荡器包括依次级联的与非门及多个反相器;所述与非门的第一输入端输入电平信号,所述与非门的第二输入端与所述环形振荡器末尾的一个反相器的输出端相连接;所述环形振荡器首位的反相器的输入端连接所述与非门的输出端,且前一所述反相器的输出端连接后一所述反相器的输入端;所述本征晶体管的控制输出端连接各所述反相器的控制端及与非门的控制端;其中,所述本征晶体管的源极作为控制输出端、栅极连接偏置电压端、漏极连接电源电压端;所述环形振荡器中段的一个所述反相器的输出端及末尾的一个所述反相器的输出端分别连接所述异或门的一个输入端;所述异或门的输出端连接所述快速振荡电路的输入端、所述复位信号发生电路的输入端及所述后处理电路的第一处理输入端;所述快速振荡电路的输出端连接所述计数器的第一计数输入端,所述复位信号发生电路的复位信号输出端连接所述计数器的第二计数输入端,所述计数器的输出端连接所述后处理电路的第二处理输入端,所述后处理电路的输出端用于输出真随机数序列。

3、所述的单环形振荡器的真随机数发生器电路结构,其中,所述环形振荡器包含的反相器的数量为2n+1,其中,n为大于2的正整数。

4、所述的单环形振荡器的真随机数发生器电路结构,其中,与所述异或门的输入端相连接的反相器为所述环形振荡器中的第n个反相器及第2n+1个反相器。

5、所述的单环形振荡器的真随机数发生器电路结构,其中,所述环形振荡器中的反相器包括第一mos管及第二mos管;

6、所述第一mos管的栅极连接所述第二mos管的栅极,且连接点作为所述反相器的输入端;所述第一mos管的源极作为所述反相器的控制端连接所述本征晶体管的控制输出端;所述第一mos管的漏极连接所述第二mos管的漏极,且连接点作为所述反相器的输出端;所述第二mos管的源极接地。

7、所述的单环形振荡器的真随机数发生器电路结构,其中,所述本征晶体管为nmos晶体管。

8、所述的单环形振荡器的真随机数发生器电路结构,其中,所述快速振荡电路包括依次级联的振荡与非门、第一振荡反相器及第二振荡反相器;

9、所述振荡与非门的一个输入端作为所述快速振荡电路的输入端连接所述异或门的输出端、另一输入端连接第二振荡反相器的输出端并作为所述快速振荡电路的输出端连接所述计数器的第一计数输入端;所述第一振荡反相器的输入端连接所述振荡与非门的输出端,所述第二振荡反相器的输入端连接所述第一振荡反相器的输出端。

10、所述的单环形振荡器的真随机数发生器电路结构,其中,所述计数器包括三个相级联的计数电路;每一所述计数电路均包含一个计数输出端。

11、所述的单环形振荡器的真随机数发生器电路结构,其中,每一所述计数电路均包括第一计数mos管、第二计数mos管、第三计数mos管、第四计数mos管、第五计数mos管、第六计数mos管、第七计数mos管、第八计数mos管、第九计数mos管、第十计数mos管、第十一计数mos管;

12、所述第一计数mos管的源极、所述第二计数mos管的源极、所述第四计数mos管的源极、所述第七计数mos管的源极、所述第八计数mos管的源极及所述第十计数mos管的源极均连接稳压电源;所述第三计数mos管的源极、所述第五计数mos管的源极、所述第六计数mos管的源极、所述第九计数mos管的源极及所述第十一计数mos管的源极均接地;所述第三计数mos管的栅极、所述第五计数mos管的栅极、所述第七计数mos管的栅极相连接并作为时钟信号输入端接收时钟信号;所述第二计数mos管的栅极、所述第六计数mos管的栅极、所述第八计数mos管的栅极相连接并作为复位信号输入端用于获取来自所述复位信号发生电路的复位信号;

13、所述第一计数mos管的栅极作为第一环接端连接第二环接端,所述第一计数mos管的漏极连接所述第二计数mos管的漏极、所述第三计数mos管的漏极及第四计数mos管的栅极;所述第四计数mos管的漏极与所述第五计数mos管的漏极、所述第六计数mos管的漏极及所述第九计数mos管的栅极相连接;

14、所述第七计数mos管的漏极连接所述第九计数mos管的漏极、所述第八计数mos管的漏极、所述第十计数mos管的栅极及所述第十一计数mos管的栅极,且连接点作为所述第二环接端;所述第十计数mos管的漏极连接所述第十一计数mos管的漏极,且连接点作为所述计数输出端。

15、所述的单环形振荡器的真随机数发生器电路结构,其中,所述复位信号发生电路包括第一延时单元、第二延时单元及复位与非门,且所述第一延时单元为同相位输出,所述第二延时单元为反相位输出;

16、所述第一延时单元的输入端及所述第二延时单元的输入端均连接所述异或门的输出端;所述第一延时单元的输出端及所述第二延时单元的输出端分别连接所述复位与非门的一个输入端,所述复位与非门的输出端作为所述复位信号发生电路的复位信号输出端。

17、所述的单环形振荡器的真随机数发生器电路结构,其中,所述后处理电路为5级异或链电路,所述后处理电路中每一级异或处理电路由两个后处理d触发器及一个后处理异或门组成。

18、本技术实施例公开了一种单环形振荡器的真随机数发生器电路结构,该电路结构包括环形振荡器、快速振荡电路、计数器、本征晶体管、异或门、复位信号发生电路及后处理电路。上述的电路结构中,环形振荡器的两个不同反相器级进行异或并输出产生的矩形脉冲,其宽度由时不变的固有传播延迟和时变抖动噪声引起的变化所决定,通过快速振荡电路及计数器对生成的连续脉冲的宽度进行量化,即可从上述计数器的最小显著位中表征由抖动噪声引起的延迟变化;通过改变本征晶体管栅极电压,从而调节环形振荡器的供应电压,以使环形振荡器的抖动噪声的幅度通过降低其充电/放电电流实现最大化,使真随机数发生器电路结构具有高能量效率及高吞吐率的应用效果。

- 还没有人留言评论。精彩留言会获得点赞!