Arm架构分支记录缓冲区的并发错误检测方法及系统

本发明涉及并发缺陷检测领域,特别是一种arm架构分支记录缓冲区的并发错误检测方法及系统。

背景技术:

1、并发性是现代计算机的一个重要特征,它使计算机能够更有效地执行复杂任务并提高整体性能。并发提供了同一时间执行多个任务的能力,这也就提高了系统的可靠性和可拓展性。引入并发可以帮助开发者更好地处理复杂的任务和问题,但是,凡事都有它的两面性。尽管多核时代之下并发编程对于实现提升性能有着极大的重要性,但是由于多线程程序执行的不确定性极易导致严重的并发错误,同时也给并发错误检测带来了困难。并发错误指的是多个进程或线程同时访问共享资源的并发系统中发生的错误。当多个进程或线程同时访问共享资源时,可能出现共享资源未经过正确同步就被修改而导致程序出现意想不到的行为或崩溃。并发错误可以以各种形式表现出来,例如争用条件、死锁、活锁和线程饥饿。一旦并发错误发生,程序或系统运行可能会出现不可预测的行为或错误的结果情况,这会严重损害系统的可用性,甚至造成巨大的经济损失。更重要的是,由于多线程并发执行的不确定性,与其他类型的错误相比,并发错误往往很难查明其产生的原因。所以对于开发者来说如何避免和正确解决并发错误是一件极为头疼的事情。

2、由于并发错误的出现会对系统的可用性和可靠性造成严重负面影响,我们必须及时地发现并解决该错误。目前已有一些解决并发问题的方法,如锁机制、信号量、原子操作等。但这些方法都各有利弊,需要根据具体的场景来选择解决方案。比如锁机制是通过加锁来防止多个线程同时访问同一资源的同步机制,当线程获取锁时设置,当线程释放锁时释放,保证同一时间只有一个线程可以访问该资源,从而避免并发错误。但锁机制可能会导致死锁,即多个线程被阻塞等待彼此释放锁。当许多线程争夺同一个锁时,它们也可能导致性能问题。原子操作是一种不可中断的操作,在执行期间不会被其他线程中断,从而避免了并发错误。不足的是,原子操作只能解决数据竞争这种特殊的并发错误,对于死锁这类并发错误只能使用其他的解决方法。此外,原子操作也可能会导致性能问题。以上这些方法为了避免死锁、竞争条件等问题则需要谨慎地设计代码,这又会增加编程复杂度和维护成本。很显然,目前的解决方法都有一定的劣势,使用这些方法是无法有效以及高效的解决困难的并发问题。

3、除了以上提到的技术,在计算机系统中用于解决并发错误的常见技术还包括回滚-重新执行。这项技术包括检测并发错误的发生,消除在导致错误的指令之后执行的任何指令的影响,然后从导致错误指令之前的点开始重新执行指令。当程序运行期间发生错误时,可以将程序回滚并从先前正确的检查点重新执行。由于并发性错误的不确定性重新执行可以避免失败。当多个事务同时对同一数据进行操作时,可能会出现并发冲突,比如两个事务同时对同一个数据进行修改,这时就可以通过回滚-重新执行来解决问题。虽然回滚-重新执行可以有效地降低并发错误发生的可能性,但它在性能和系统资源方面有很大的开销,并且并不能解决全部并发错误,例如无法解决死锁以及丢失更新的问题。

4、想要解决并发错误,首先得检测出并发错误,查明其发生的原因。目前,学术界及工业界已经在使用的检测并发错误的一种方法是使用动态分析技术,如数据竞争检测和模型检查。数据竞争检测包括分析程序的执行,以识别多个线程在没有适当同步的情况下访问同一共享资源的实例。模型检查包括系统地探索所有可能的程序执行,以识别潜在的并发错误。这两种技术都可以有效地检测并发错误,但由于监控和分析的开销,它们可能会减慢软件系统的执行速度。另一种方法是静态分析技术,这种方法包括分析软件系统的源代码,以识别潜在的并发问题,如竞争条件或死锁。静态分析工具可以扫描代码中可能导致并发错误的特定模式或构造,并为开发人员提供解决这些问题的反馈。静态分析技术可能比动态分析技术更高效,但在检测细微的并发错误方面可能会产生误报。

5、除了以上两种分析方法,实际上还可以通过记录和跟踪软件系统的行为来检测并发错误。x86架构上的last branch record(lbr)是一个用于记录处理器执行的分支指令的信息的硬件功能。现在已经有不少研究者通过使用lbr寄存器进行检测并发错误相关的研究。例如,lbr-record使用lbr寄存器来检测linux内核代码中的竞争条件。通过分析lbr寄存器中的存储记录,lbr-record可以检测当多个线程在没有适当同步的情况下访问共享资源时发生的竞争条件。

6、arm架构凭借着其功率效率、可扩展性、低成本和高性能等优势在近些年来越来越受欢迎,尤其是在移动设备和物联网(iot)领域。所以如今搭载arm架构机器的可靠性也变得尤为重要。2021年arm公司发布armv9体系结构。armv9体系结构在兼容armv8体系结构的基础上加入了一些新的特性,其中就包括分支记录缓冲区扩展(branch record bufferextension,brbe)(martin weidmann,director product management,atg arm,lvc20-214https://static.linaro.org/connect/lvc20/presentations/lvc20-214-0.pdf)。分支记录缓冲区(brb)是arm处理器的一个硬件组件,它以低成本方式捕获控制路径历史的分支记录缓冲区。具体而言,分支指令的地址会记录在brbsrc寄存器中,分支记录的目标地址会记录在brbtgt寄存器中,而分支指令的类型、跳转是否有效以及目标地址的异常等级等信息则记录brbinf寄存器中,如图1所示。现有技术中,没有在arm架构上利用硬件功能来检测并发错误问题的研究。

技术实现思路

1、本发明所要解决的技术问题是,针对现有技术不足,提供一种arm架构分支记录缓冲区的并发错误检测方法及系统,降低开销。

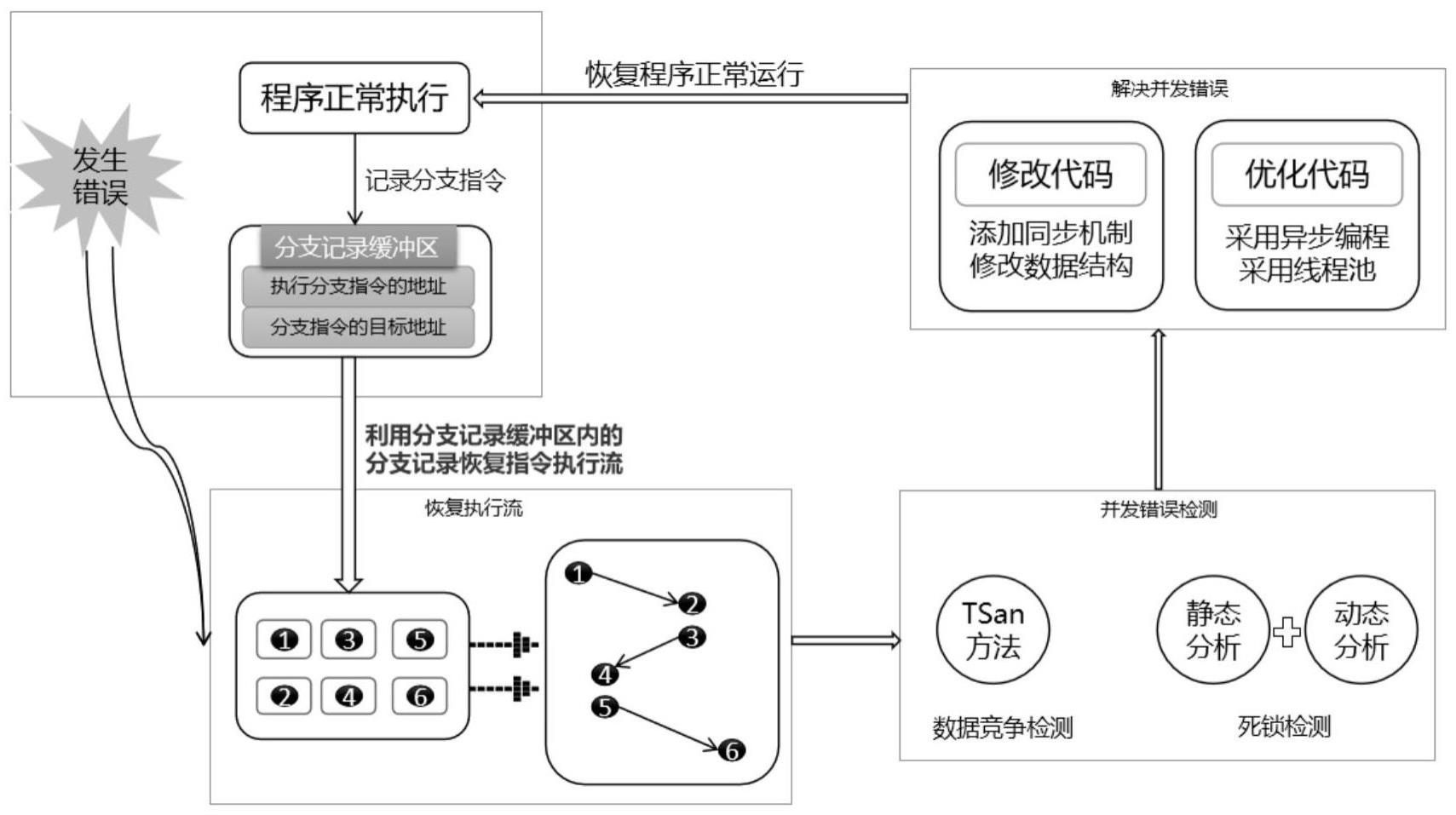

2、为解决上述技术问题,本发明所采用的技术方案是:一种arm架构分支记录缓冲区的并发错误检测方法,该方法包括:

3、s1、利用性能监控单元的事件计数器统计已记录的分支记录数,若所述事件计数器的计数值已达到阈值,则性能监控单元触发中断处理程序;

4、s2、读取分支记录缓冲区内最新的一条分支记录,中断处理程序成功跳转执行的最后位置即发生并发错误的位置。

5、arm架构中的性能监控单元(pmu)是一种硬件组件,用于收集和监控处理器的性能数据。与分支记录缓冲区不同的是,性能监控单元是可以引发中断的。pmu提供了一组专门的寄存器用于度量和分析处理器的各种性能指标,一般情况下编程人员只会使用性能监控单元来计算与cpu相关的事件(执行指令数、捕获异常数、时钟周期数等)、与cache有关的事件(cache访问次数,miss次数等)以及与tlb有关的事件等。现有技术中,并未通过操作这些计数器的相应的控制寄存器来控制事件计数器计数一些其他事件。本发明利用pmu记录分支记录缓冲区内存储分支记录的数量,硬件性能计数器的开销极低,几乎为零,因此极大地提高了软件系统的执行速度。

6、本发明步骤s1中,还包括:将分支记录缓冲区内存储的指令信息数据放入提前分配好的物理内存块中。当分支记录缓冲区已满时,分支记录缓冲区不能引发中断,而是会采用循环覆盖的方式将之前的分支记录数据覆盖,从而导致分支记录指令跟踪丢失。本发明将分支记录缓冲区内存储的指令信息数据放入提前分配好的物理内存块中,能够有效防止循环缓冲导致旧的分支记录数据被覆盖。

7、步骤s2之后,还包括:

8、s3、读取分支记录缓冲区内的分支记录,确定节点之间的跳转关系,通过时间戳记录的指令执行时间判断指令的执行顺序,结合执行顺序以及节点之间的跳转关系,将无序的指令执行节点连接成为有序的指令执行流。

9、本发明借助分支记录缓冲区来获得分支指令的分支记录,该过程由硬件组件分支记录缓冲区获取,且分支记录缓冲区上下文切换和在线阅读成本低,所以开销几乎为零。利用硬件机制来记录程序执行的路径,不需要修改程序的源代码,进一步提高了软件系统的执行速度。

10、本发明步骤s3之后,还包括:

11、s4、利用所述有序的指令执行流检测发生并发错误的原因。

12、本发明步骤s4之后,还包括:

13、s5、根据步骤s4确定的原因,选择纠正措施处理并发错误。

14、本发明中,所述纠正措施包括修复代码或优化代码。

15、步骤s1之前,还包括:判断分支记录缓冲区是否处于可用状态,若是,则进入步骤s1;否则,停止产生分支记录,结束。

16、作为一个发明构思,本发明还提供了一种arm架构分支记录缓冲区的并发错误检测系统,其包括:

17、一个或多个处理器;

18、存储器,其上存储有一个或多个程序,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器实现本发明上述方法的步骤。

19、作为一个发明构思,本发明还提供了一种计算机可读存储介质,其存储有计算机程序,所述计算机程序被处理器执行时实现本发明上述方法的步骤。

20、与现有技术相比,本发明所具有的有益效果为:

21、1.本发明提供了一种新的解决并发错误的方法,可以有效提高多线程程序的稳定性和可靠性。本发明利用arm架构新引入的分支记录缓冲区实现恢复处理器指令执行流,再结合其他调试或分析工具能够检测出导致并发错误的根本原因,从而解决难以处理的并发错误。

22、2.本发明利用硬件机制来记录程序执行的路径,不需要修改程序的源代码,恢复执行流的过程是借助分支记录缓冲区来获得分支指令的分支记录,该过程由硬件组件分支记录缓冲区获取,且分支记录缓冲区上下文切换和在线阅读成本低,所以开销几乎为零。

23、3.由于分支记录缓冲区是arm架构上的通用机制,因此本发明适用于大多数arm架构的计算机,具有一定普遍性。

24、4.本发明在提供安全可靠的解决并发错误的同时,几乎不影响软件系统的性能。

- 还没有人留言评论。精彩留言会获得点赞!