电源电压的调整方法及装置、存储介质、电子设备与流程

本技术实施例涉及计算机领域,具体而言,涉及一种电源电压的调整方法及装置、存储介质、电子设备。

背景技术:

1、现场可编程门阵列(field programmable gate array,简称为fpga)具有可定制性、低延迟和高性能功耗比,所以fpga加速卡用于机器学习推理、图像语音识别、大数据分析、存储虚拟化等,通常部署到机房或者数据中心的服务器中为用户带来更先进的ai计算加速解决方案。fpga加速卡所需要的电源种类较多(即fpga加速卡需要同时在多种不同的电压下工作),不同的电源需要满足一定的上电时序要求,且不同版本的fpga以及不同应用场景下的fpga需要的工作电压是不一样的,进而会要求同一电源输出不同的电压值,以满足fpga改变工作电压的需求,而按照目前市面上的dcdc电源,同一电源如果要输出不同电压值,则需要手动重新配置dcdc芯片的外围电路。

2、目前,fpga加速卡上的fpga通常在以下两种情况下会要求某一项电源输出不同电压:(1)加速卡上主芯片fpga版本不同,但是pin to pin;(2)加速卡在不同应用场景中,某一项电源要求电压不同。

3、针对以上两种情况,现有的技术一般是手动重新配置直流转直流(directcurrent-direct current,简称为dcdc)电源的外围电路,即根据实际情况,rework dcdc的外围电路,满足fpga的供电要求。如下举例说明,如图1是常见dcdc芯片框图架构,引脚主要包括输入vin、输出vout、使能en、电源ok(pgood)、软启动设置(ss)以及设置输出电压的feedback(fb),fb引脚通过两个电阻r1、r2配置确定输出电压。当输出电压需要改变的时候,连接fb引脚的配置电阻r1、r2需要rework改变阻值。

4、但通过上述方式修改电源电压实际操作起来比较麻烦,并且当批量部署的加速卡需要对fpga的某项供电电源配置改变时,如果通过手动rework改变,工作量巨大,而且不能随时切换电压,不便于管理。

5、针对相关技术中,无法自适应配置fpga加速卡中的fpga的工作电压的问题,目前尚未提出有效的解决方案。

6、因此,有必要对相关技术予以改良以克服相关技术中的所述缺陷。

技术实现思路

1、本技术实施例提供了一种电源电压的调整方法及装置、存储介质、电子设备,以至少解决无法自适应配置fpga加速卡中的fpga的工作电压的问题。

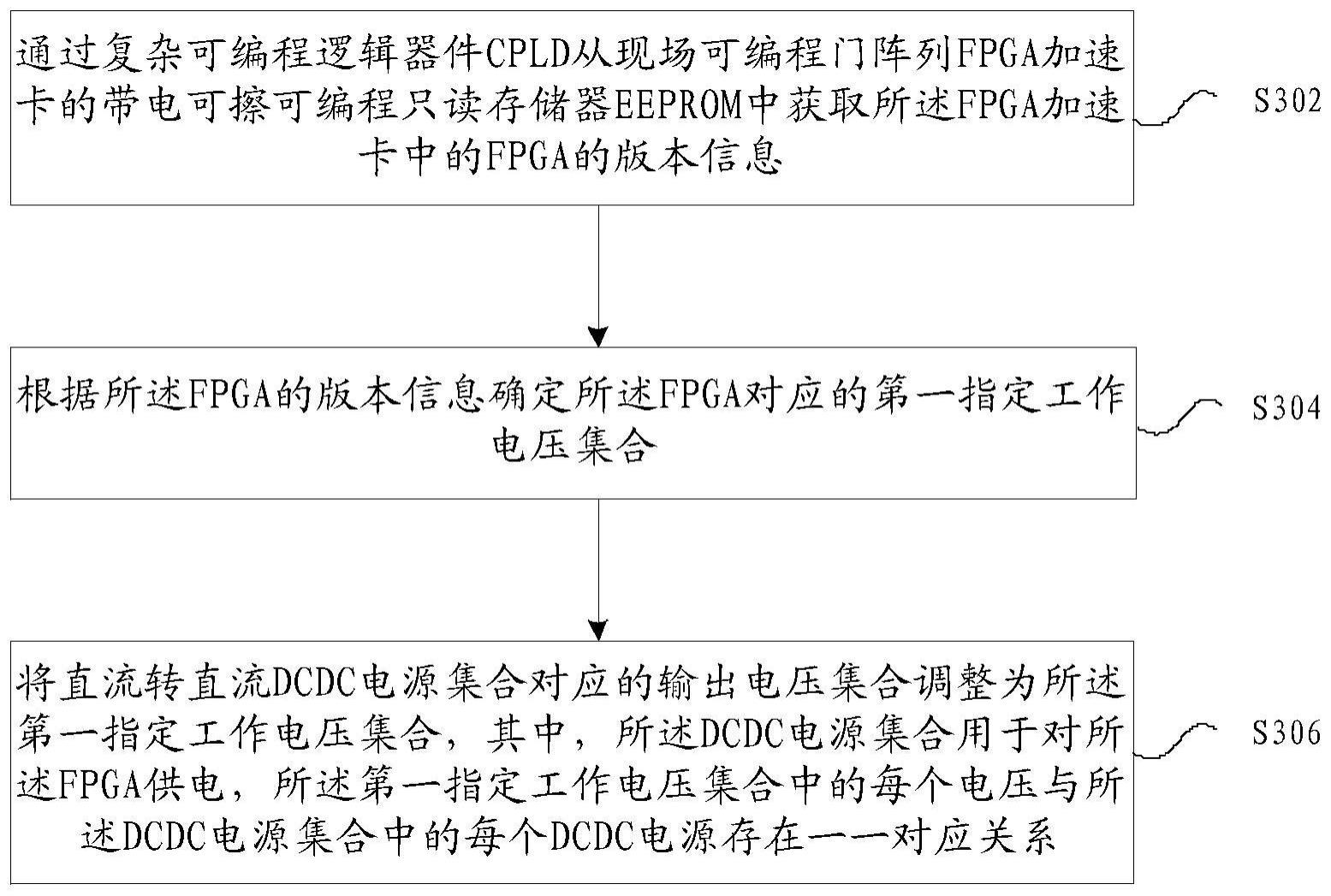

2、根据本技术的一个实施例,提供了一种电源电压的调整方法,包括:通过复杂可编程逻辑器件cpld从现场可编程门阵列fpga加速卡的带电可擦可编程只读存储器eeprom中获取所述fpga加速卡中的fpga的版本信息;根据所述fpga的版本信息确定所述fpga对应的第一指定工作电压集合;将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合,其中,所述dcdc电源集合用于对所述fpga供电,所述第一指定工作电压集合中的每个电压与所述dcdc电源集合中的每个dcdc电源存在一一对应关系。

3、在一个示例性实施例中,将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合,包括:通过以下方式调整所述dcdc电源集合中第i个dcdc电源的输出电压,以将所述dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合:根据所述第一指定工作电压集合中的第i个指定工作电压确定电压调整信号;通过所述cpld将所述电压调整信号发送至电压控制器,并指示所述电压控制器根据所述电压调整信号配置所述第i个dcdc电源对应的反馈fb电路,其中,所述fb电路用于设置dcdc的输出电压。

4、在一个示例性实施例中,将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合之后,所述方法还包括:根据所述fpga的版本信息确定所述fpga的供电要求,其中,所述供电要求包括所述fpga接收所述第一指定工作电压中每个工作电压对应的电压信号的时间要求;根据所述时间要求为所述dcdc电源集合中每个dcdc电源供电,以使所述dcdc电源集合根据所述时间要求为所述fpga提供所述第一指定工作电压集合。

5、在一个示例性实施例中,将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合之后,所述方法还包括:在通过所述cpld确定所述fpga的工作模式发生变化的情况下,确定所述fpga在当前工作模式下对应的第二指定工作电压集合;将直流转直流dcdc电源集合对应的输出电压集合调整为所述第二指定工作电压集合。

6、在一个示例性实施例中,确定所述fpga在当前工作模式下对应的第二指定工作电压集合,包括:从所述eeprom中获取第一表格,其中,所述第一表格中具有所述fpga在不同工作模式下对应的指定工作电压集合;从所述第一表格中确定所述fpga在所述当前工作模式下对应的第二指定工作电压集合。

7、在一个示例性实施例中,将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合之后,所述方法还包括:通过模数转换器adc获取所述dcdc电源集合中第i个dcdc电源的输出电压;确定所述第i个dcdc电源的输出电压与所述第一指定工作电压集合中对应的第i个指定工作电压的第一差值;在所述第一差值大于预设阈值的情况下,再次基于第i个指定工作电压调整所述第i个dcdc电源的输出电压;确定调整后的所述第i个dcdc电源的输出电压与所述第i个指定工作电压的第二差值;在所述第二差值大于所述预设阈值的情况下,通过所述cpld向服务器发送警告信息,其中,所述警告信息用于指示所述第i个dcdc电源对应的fb电路故障,所述fb电路用于设置dcdc的输出电压。

8、在一个示例性实施例中,根据所述fpga的版本信息确定所述fpga对应的第一指定工作电压集合,包括:从所述eeprom中获取第二表格,并从所述第二表格中获取所述fpga在对应版本下的第一指定工作电压集合,其中,所述第二表格中具有不同版本的fpga对应的指定工作电压集合;或者通过所述cpld将所述版本信息发送至服务器,并获取所述服务器发送的所述第一指定工作电压集合。

9、根据本技术的另一个实施例,提供了一种电源电压的调整装置,包括:获取模块,用于通过复杂可编程逻辑器件cpld从现场可编程门阵列fpga加速卡的带电可擦可编程只读存储器eeprom中获取所述fpga加速卡中的fpga的版本信息;确定模块,用于根据所述fpga的版本信息确定所述fpga对应的第一指定工作电压集合;调整模块,用于将直流转直流dcdc电源集合对应的输出电压集合调整为所述第一指定工作电压集合,其中,所述dcdc电源集合用于对所述fpga供电,所述第一指定工作电压集合中的每个电压与所述dcdc电源集合中的每个dcdc电源存在一一对应关系。

10、根据本技术的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

11、根据本技术的又一个实施例,还提供了一种电子设备,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

12、通过本技术,由于可以通过cpld从fpga加速卡的eeprom中获取fpga加速卡中的fpga的版本信息,并根据fpga的版本信息确定fpga对应的第一指定工作电压集合,进而将dcdc电源集合对应的输出电压集合调整为第一指定工作电压集合,进而无需在fpga的版本发生改变的情况下,手动重新配置dcdc芯片的外围电路以修改fpga的供电电压,因此,解决了现有技术中无法自适应配置fpga加速卡中的fpga的工作电压的问题,进而达到了可以自适应配置fpga加速卡中的fpga的工作电压的效果。

- 还没有人留言评论。精彩留言会获得点赞!