一种时序性能调整方法及装置与流程

本发明属于电子设计自动化(eda),具体涉及一种时序性能调整方法及装置。

背景技术:

1、集成电路布局是电子设计自动化(eda)中非常重要的一环,其目的是将电路元件合理地布置在芯片上,以实现电路的最优性能。在集成电路的设计中,时序分析也是非常重要的一步,其目的是分析电路中最长的关键路径,以确定电路的最大工作频率和时序性能。随着芯片工艺的提升,fpga的规模也越来越大,布局、布线这些流程显得愈发重要,它们对芯片的使用面积、功耗、用户电路的工作频率等性能有着直接的影响,尤其是满足用户电路的时序约束的时序性能,是一个非常重要的目标,它将直接影响到设计功能是否能够实现。

2、现有的eda编译流程是先执行布局,布局完成之后再依据布局结果进行布线;在现有技术中没有时序分析这一环节导致了在布局、布线后往往会发现布线的集成电路不满足设计要求,导致需要推倒重来大大降低了集成电路设计的效率;同时现有技术中也存在使用启发式算法进行集成电路优化验证的方法,但是由于集成电路布局具有极高的复杂性,仅以运算的方式进行布局优化很难保证效率和质量,出现设计效率低下和优化结果不符合用户预期的现象。

3、所以目前需要开发一种时序性能调整方法,可以达到提高时序性能调整效率、提升时序性能调整效果的目的。

技术实现思路

1、本发明是为解决上述现有技术的全部或部分问题,提出一种时序性能调整方法,以提升时序性能调整效率和效果。本发明还提供了一种时序性能调整装置。

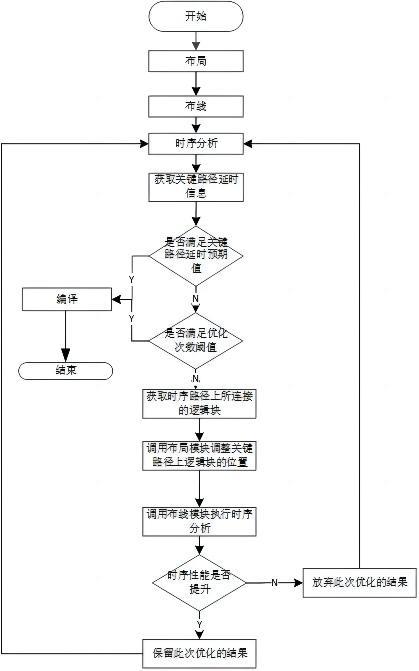

2、本发明提供的一种时序性能调整方法,包括:预定义优化次数阈值和关键路径延时预期值;执行优化:步骤s1.对当前电路进行时序分析并返回关键路径延时信息;步骤s2.基于所述关键路径延时信息和当前优化次数判断所述当前电路是否满足所述优化次数阈值或关键路径延时预期值,若满足,则对所述当前电路进行优化后的编译操作,若不满足,则执行时序优化操作,得到本次优化后的电路,执行步骤s3;步骤s3.对所述本次优化后的电路进行时序分析,判断时序性能是否提升。

3、所述预定义优化次数阈值是指设置一个优化次数的上限值,由于集成电路布局的复杂性往往难以达到最优布局,也无法验证现有布局是否是最优布局,此时就需要通过设置一个最大的优化次数来防止由于无限制地反复优化导致的效率低下问题;所述关键路径延时信息指的是对集成电路性能制约能力最强的一条路径,通过设置关键路径延时预期值,使得集成电路优化至设置程度后不再进行再次优化,提升设计效率;通过布局优化后再次进行时序分析,保留正向优化结果,放弃无优化效果或负优化效果的新布局,保证了优化的效率。

4、首次时序分析前进行:对所述当前电路进行布局;对所述当前电路进行布线,其中所述布局需要调用所述布局模块,所述布线需要调用所述布线模块。

5、所述步骤s2中,进行编译操作后,结束执行;所述步骤s3中,判断时序性能是否提升;若提升,则保留所述本次优化结果,返回步骤s1,基于此次优化的结果继续执行;若无提升,则放弃所述此次优化的结果,返回步骤s1,重新执行。由于集成电路具有高度的复杂性,信号之间高度复杂,每次对所述关键路径进行优化时难以一步到位,为了取得相较于传统集成电路优化方式更好的优化效果,采用了累次优化的方法,通过循环进行时序分析、时序优化、再次时序分析以确认保留或者放弃此次时序优化的结果,这几个步骤,保证每次循环均对所述电路进行了正向优化或不作改动,使得时序优化的正向结果不断累加,得到性能更优的电路布局。

6、所述时序分析的方法包括:建立两个时序参数:第一参数和第二参数,分别表征接收数据到达时间、建立时间数据要求到达时间;基于第一参数、第二参数,计算得到关键路径的slack值作为所述关键路径信息,其中,第一参数和第二参数通过静态时序分析获取,所述静态时序分析包括:建立时间(set up time)分析和保持时间(hold time)分析,更具体的是指通过静态时序分析中的建立时间分析完成的,所述关键路径是集成电路中最长的路径,所述关键路径很小的浮动也能够影响整个电路的工作效率,关键路径所需的时长决定了整个电路所需的时长。

7、计算得到关键路径的slack值的方法包括,设置延时公式;所述延时公式为:slack值=第二参数-第一参数。

8、所述关键路径指所述slack值最小的一条路径,其中关键路径制约了电路的性能,电路的频率高低取决于所述关键路径slack的值的大小,所述slack值大于等于零时所述电路频率能够达到用户期望值,所述slack值小于等于零时,所述电路频率无法达到用户期望值,此时就需要对所述电路进行优化,所述slack值越小电路的频率越低,效率越低。

9、所述逻辑块分为空逻辑块和非空逻辑块。

10、所述时序优化操作包括:交换逻辑块;所述交换逻辑块的方法包括:划定逻辑块的交换范围;优先遍历所述交换范围中的空逻辑块,依次与所述关键路径上的逻辑块交换位置直到计算得出的slack值增加;遍历所有所述空逻辑块后,slack值未增,则所述关键路径上的逻辑块与所述交换范围内的非空逻辑块进行交换,直到计算得出的slack值增加;所述交换范围内所有逻辑块均被交换过后,slack值仍未增加,则按预定义执行:交换所述交换范围外相邻的逻辑块或直接返回交换失败;执行交换所述交换范围外相邻的逻辑块的过程包括:若经交换使得所述slack值增加,则保留使得slack值增加的布局并输出,若经交换未使得所述slack值增加,则直接输出原有布局。所述预定义是指优化开始前用户设置的当所述交换范围内所有逻辑块均被交换过后slack值未增加时执行的操作,其中,相邻的逻辑块指,所述交换范围向四周外扩一个逻辑块形成的新范围中不属于所述交换范围内逻辑块的部分,交换后所述逻辑块间的曼哈顿距离之和小于交换前的初始距离之和,基于所述预定义,能够使用户灵活选择逻辑块交换遍历的程度,按需进行时序优化操作。

11、所述布线操作使用的是不协商的增量布线方法。其中所述不协商的增量布线方法能够提高所述布线操作的效率。

12、所述优化次数阈值是用户自定义的最大优化次数;所述步骤s2中,获取当前优化次数判断是否达到所述阈值,若是,则不满足优化条件直接进行编译,若不是,则执行步骤s3;所述关键路径的延时预期值是slack值的预期值,所述步骤s2中,获取当前电路的slack值是否大于预期值,若是,则不满足优化条件直接进行编译,若不是,则执行步骤s3。其中所述阈值限制了最大循环次数,使得优化次数得以控制在合理范围内,防止出现过度优化的情况,有效提高了效率;同时所述slack预期值的设置控制了优化效果,当所述关键路径的延时优化至预期程度时优化循环即停止优化进入编译流程,一方面防止过度优化,另一方面也保证了优化效果。

13、本发明另一方面提供了一种装置,包括:布局模块用于将打包的逻辑块,依照物理约束规则映射到芯片上;布线模块用于获取逻辑块的位置和延时信息反馈至所述布局模块,通过所述布局模块和所述布线模块,所述装置能够达到高效优化电路的目的。

14、本发明通过使用时序分析和预设的逻辑块移动方法提高了集成电路的布局效率;通过设置阈值防止循环优化的集成电路过度优化、节约资源;同时由于基于实际电路的时序分析能够相对于理论运算有更高的精确度,本发明能达到提高集成电路优化精度的效果。

- 还没有人留言评论。精彩留言会获得点赞!