一种基于FPGA的I2C从机的测试系统

本发明涉及集成电路、接口测试,尤其涉及一种基于fpga的i2c从机的测试系统。

背景技术:

1、i2c总线是一种双线串行协议,在传统的验证过程中,激励的产生往往是根据主机产生的scl(i2c总线的时钟信号)时钟信号沿来判断什么时候发送或采样sda(i2c总线的数据信号)数据信号,从而实现协议通信。

2、原型验证中一般用mcu作为i2c mster对i2c slave的原型机进行测试,但是mcu生成的i2c有最大频率的限制,调节sda与scl关系也有步长的限制,此外,测试机台(昂贵、有限制、不方便携带或移动),非常影响研发和测试的沟通效率。

3、经检索,申请号cn114237992a的中国专利,公开了i2c总线验证方法与验证系统,其目的是能通过仿真动态的调节时钟信号的占空比,满足了更广泛的应用测试,提高验证的可靠性。

4、但是,在fpga原型验证或者芯片测试阶段,很难相对简易地搭建一套可调节i2c时序的硬件测试系统。在芯片原型验证阶段,没法在硬件上(非仿真)对芯片的i2c slave时序进行测试分析,在芯片测试阶段,针对i2c slave时序的测试,在一些缺乏测试机台的场景中无法对芯片进行测试,而且测试机台成本昂贵且资源相对紧张,非专业人士难以上手,因此,亟需一种基于fpga的i2c从机的测试系统。

技术实现思路

1、本发明的目的是为了解决现有技术中存在的缺陷,而提出的基于fpga的i2c从机的测试系统。

2、为了实现上述目的,本发明采用了如下技术方案:

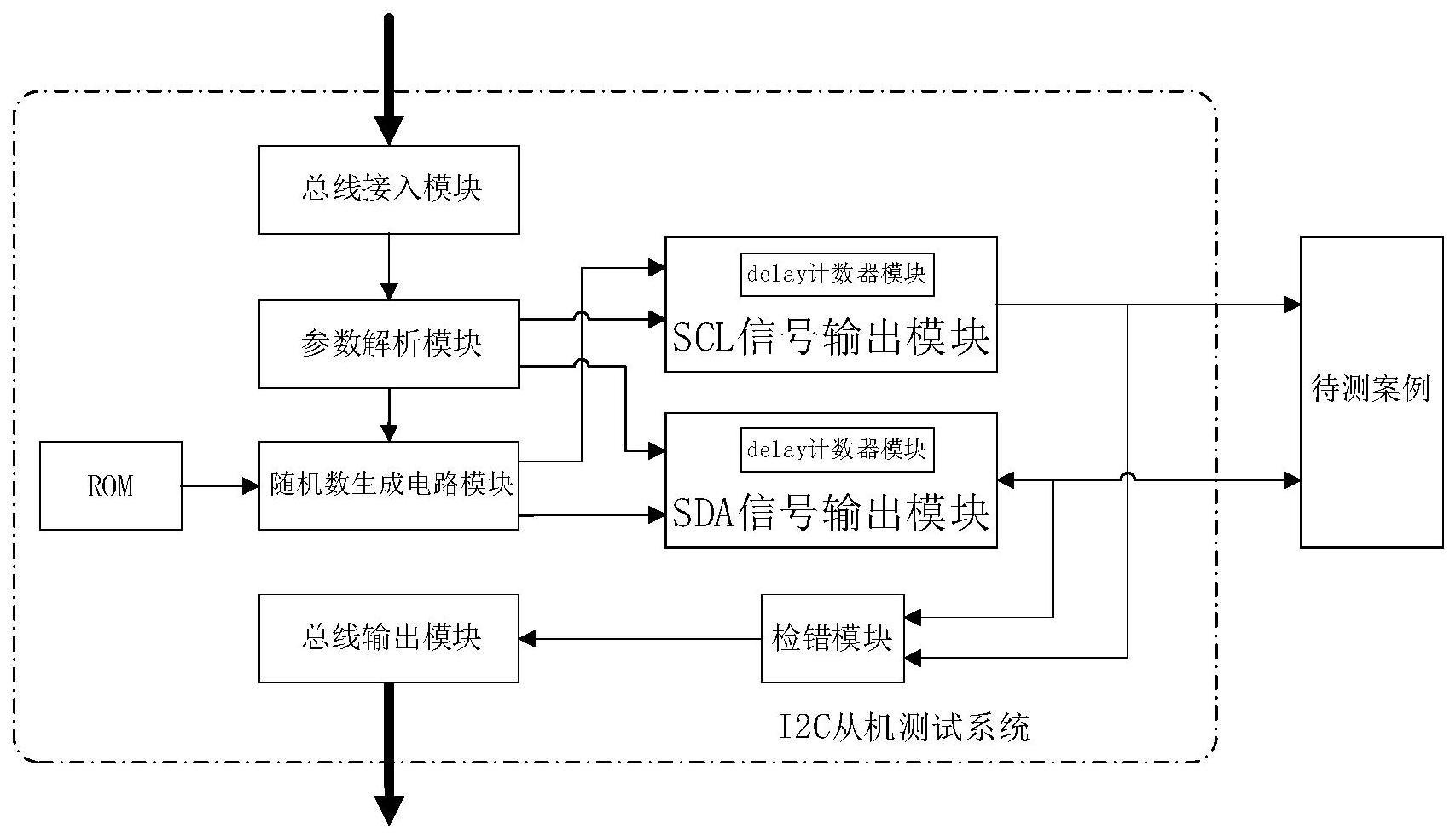

3、一种基于fpga的i2c从机的测试系统,包括总线接入模块、参数解析模块、随机数生成电路模块、总线输出模块、scl信号输出模块、sda信号输出模块和检错模块,其中,所述总线接入模块与上位机相连接;

4、所述总线接入模块通过所述参数解析模块与所述随机数生成电路模块相连接,所述参数解析模块与所述随机数生成电路模块均连接所述scl信号输出模块和所述sda信号输出模块,所述scl信号输出模块和所述sda信号输出模块均通过所述检错模块连接所述总线输出模块。

5、进一步地,所述scl信号输出模块和所述sda信号输出模块均设有delay计数器模块,所述scl信号输出模块和所述sda信号输出模块均连接待测终端。

6、进一步地,所述总线接入模块,用于将上位机传输的相应数据按照既定协议将需要调节和控制的i2c时序参数和需要读写参数传入系统。

7、进一步地,参数解析模块,用于得到系统需要的参数,其中,参数具体包括读写参数、scl频率、scl时钟个数、占空比、抖动参数、随机使能参数a、随机使能参数b以及sda的关键时序参数;

8、scl信号输出模块,用于获取到参数解析模块传输的参数数据之后,调节内部计数器和分频器信息,输出相应频率、占空比的scl信号,单位读写周期内的scl的数量也可以控制。

9、进一步地,随机数生成电路模块,用于根据随机使能参数a,选择不同的硬件数据通路;

10、scl信号输出模块、随机数生成电路模块和所述参数解析模块相互连接,具体流程为:

11、①如果随机数生成电路模块的随机使能打开(由随机使能参数a决定),则使能内部的随机数生成电路,时序参数全部由随机数电路自动生成,而随机使能参数b可决定随机化的边界条件是选择上位机所传的参数还是直接使用协议所规定的时序参数,该参数保存在fpga的rom中;

12、②如果随机数生成电路模块的随机使能关闭(由随机使能参数a决定),则不经过内部的随机数生成电路,时序参数全部由用户上位机给出,用户获得对延时电路和分频电路的控制权;

13、生成的随机数值或者用户指定的数值会被给到scl输出模块的计数器和分频器模块,对scl信号进行一些占空比和频率的抖动处理。

14、进一步地,所述随机数生成电路模块的随机数生成电路具有约束条件,具体为:

15、scl占空比所对应的随机数需要满足i2c协议规定的thigh和tlow的条件;

16、scl时钟的抖动所对应的随机数需要满足在一定个数的时钟周期内,其平均频率保持恒定并且和用户所设置的频率数值保持一致;

17、在i2c start阶段的thd_sta所对应的随机数需要满足i2c协议规定。

18、进一步地,sda信号输出模块、随机数生成电路模块和所述参数解析模块相互连接,具体流程为:

19、随机数生成电路模块根据随机使能参数a,选择不同的硬件数据通路:

20、①如果随机使能打开(由随机使能参数a决定),则使能内部的随机数生成电路,时序参数全部由随机数电路自动生成,而随机使能参数b可决定随机化的边界条件是选择上位机所传的参数还是直接使用协议所规定的时序参数,该参数保存在fpga的rom中;

21、②如果随机使能关闭(由随机使能参数a决定),则时序参数全部由用户上位机给出,用户获得对延时电路的控制权;

22、根据所得的时序参数,sda输出模块结合从scl输出模块获取到沿的信息,调节内部计数器信息,输出相应的sda信号。

23、进一步地,所述随机数生成电路模块的随机数生成电路具有约束条件,具体为:生成的随机数需要满足i2c协议规定的tsu_sta、thd_dat、tsu_dat、tsu_sto的条件。

24、进一步地,所述检错模块,用于通过检测内部状态机是否异常来进行报错,其中,该检错模块会检测因为时序不满足导致从机发出nack或者不发ack/nack的故障。

25、进一步地,检错模块与总线输出模块相互连接,具体流程为:检测到故障之后,将出错的时序参数和读写数据通过总线输出模块进行上传,上传的对象可以是个人电脑或者其他微控制器。

26、相比于现有技术,本发明的有益效果在于:

27、具有低成本、易搭建、易携带、易移植、易上手等性能,在一些远程场景中,可以方便复现和定位问题,提升研发沟通效率,降低研发测试成本,加快产品落地;

28、能够调节i2c scl占空比、频率且最大频率可超过协议规定,满足一些特定需求,能够调节i2c sda与scl沿之间的时序关系,其中,时序参数可由内部自动随机化产生也可以由用户通过上位机传入,随机化的边界可以是协议规定的参数也可以是用户传入的数值,可下发时序参数和上报出错参数;

29、用户可以根据自己的特殊需求构造独特的测试场景,比如发若干次start,再正常发送数据;或者发一次start之后直接就stop了等,可结合uvm平台输入随机参数使得uvm仿真平台硬件化;

30、可以作为原型验证的主要测试系统,作为芯片测试的备用测试系统;

31、通信接口方式灵活多样,可通过串口/网口连接电脑,也可以通过i2c/spi连接mcu等微控制芯片,用以下发命令和上报数据;

32、此外,具备功能可扩展性。根据自己的需求加入想要的功能,且更改灵活便捷。

- 还没有人留言评论。精彩留言会获得点赞!