器件、芯片、设备、存算调度和多层神经网络训练方法与流程

本技术涉及半导体,具体地,涉及一种半导体器件、集成芯片、电子设备、存算调度方法和多层神经网络训练方法。

背景技术:

1、集成电路(integrated circuit,简称ic)是一种微型电子器件或部件。电子产品目前正在朝小型化、高密度化、高可靠性、低功耗方向发展,因此,集成电路/芯片发展方向也是小型化、高密度化、高可靠性、低功耗,3d-ic应运而生。

2、一般ic为一层器件,内部通过金属进行平面互联,3d-ic通过工艺做到了2层或多层器件,为了缩小芯片体积,业界不断发展出了很多新的工艺技术,目前主流的方式主要包括embedit-dram(嵌入式)工艺,和hbm(high bandwidth memory,垂直堆叠存储)方式,3d,2.5d封装技术等其中:

3、嵌入式工艺是在芯片内部实现,把dram(dynamic random access memory,动态随机存取存储器,)工艺和logic(逻辑)工艺结合在一起,在一个芯片上集成了存储单元和逻辑单元。两种工艺在一个平面上集成,edram的工艺需求较为特殊,如图1所示,其电容要么往下挖,要么往上做成垂直状,纵向开孔容易对已经形成的逻辑单元造成影响;其次,在打孔工艺中,若孔的宽高比较小,工艺难度过大,很容易出现如图2中开孔断层的情况,开孔良率低;若为了保证半导体性能,开孔过宽,开孔在半导体表面占比过大容易导致半导体表面积的浪费,且容易导致半导体表面出现翘曲变形情况;

4、hbm工艺是实现计算芯片和dram芯片之间的互联技术,是一种高性能,高带宽的ddr(ddr sdram,双倍速率同步动态随机存储器)连接模式。一般的hbm由多个hbm存储单元(例如图3中的dram die)和1个逻辑单元(例如图3中的logic die)组成,存储单元里面不包含和处理单元(例如图3中的cpu/gpu/soc die)通信的部分,所有的存储单元通过tsv孔(硅通孔)连接到逻辑单元,然后通过逻辑单元的hbm phy接口与处理单元互联;hbm工艺本质上是存储单元的一种立体封装技术,成本高昂,需要额外一颗高速接口来与处理单元通信。其次,hbm phy接口是一种多位宽的并行接口,在一定程度上可以有效提高带宽,但所需要的dram颗粒的ddr接口一个都不能少,而高速接口的设计与制备难度很高。同时,hbm ddr还需要一片互联层(例如图3中的interposer si)来与处理单元进行互联,成本较高,且也会影响整体产品的良率。

5、因此,目前的3d-ic均无法适应芯片的发展方向,亟需一款真正的3d-ic。

6、在背景技术中公开的上述信息仅用于加强对本技术的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、为了解决上述技术问题,本技术实施例中提供了一种半导体器件、集成芯片、电子设备、存算调度方法和多层神经网络训练方法。

2、本技术实施例的第一个方面,提供了一种半导体器件,包括:

3、逻辑器件层,逻辑器件层包括多个计算单元;

4、在逻辑器件层上的孤岛隔离层;

5、在孤岛隔离层上形成的存储器件层,存储器件层包括多个存储单元;

6、多个层间通孔,多个层间通孔实现逻辑器件层与存储器件层电连接。

7、在本技术一个可选实施例中,逻辑器件层还包括多个计算调度单元,计算调度单元分别与各计算单元与存储单元信号连接,计算调度单元用于根据待处理任务的计算量从计算单元中确定目标计算单元,并调用目标计算单元;

8、存储器件层还包括多个存储调度单元,存储调度单元分别与各计算单元与存储单元信号连接,存储调度单元用于根据待处理任务的内存量从存储单元中确定目标存储单元,并调用目标存储单元。

9、在本技术一个可选实施例中,存储单元包括:独立存储单元与共享存储单元,独立存储单元与共享存储单元均与存储单元信号连接;其中,独立存储单元与存储单元耦合匹配。

10、在本技术一个可选实施例中,独立存储单元与共享存储单元相间铺设于存储器件层内;或,独立存储单元与共享存储单元相互堆叠于存储器件层内。

11、在本技术一个可选实施例中,存储器件层为共享存储器件层,存储单元为共享存储单元;或存储器件层为独立共享存储器件层,存储单元为独立存储单元。

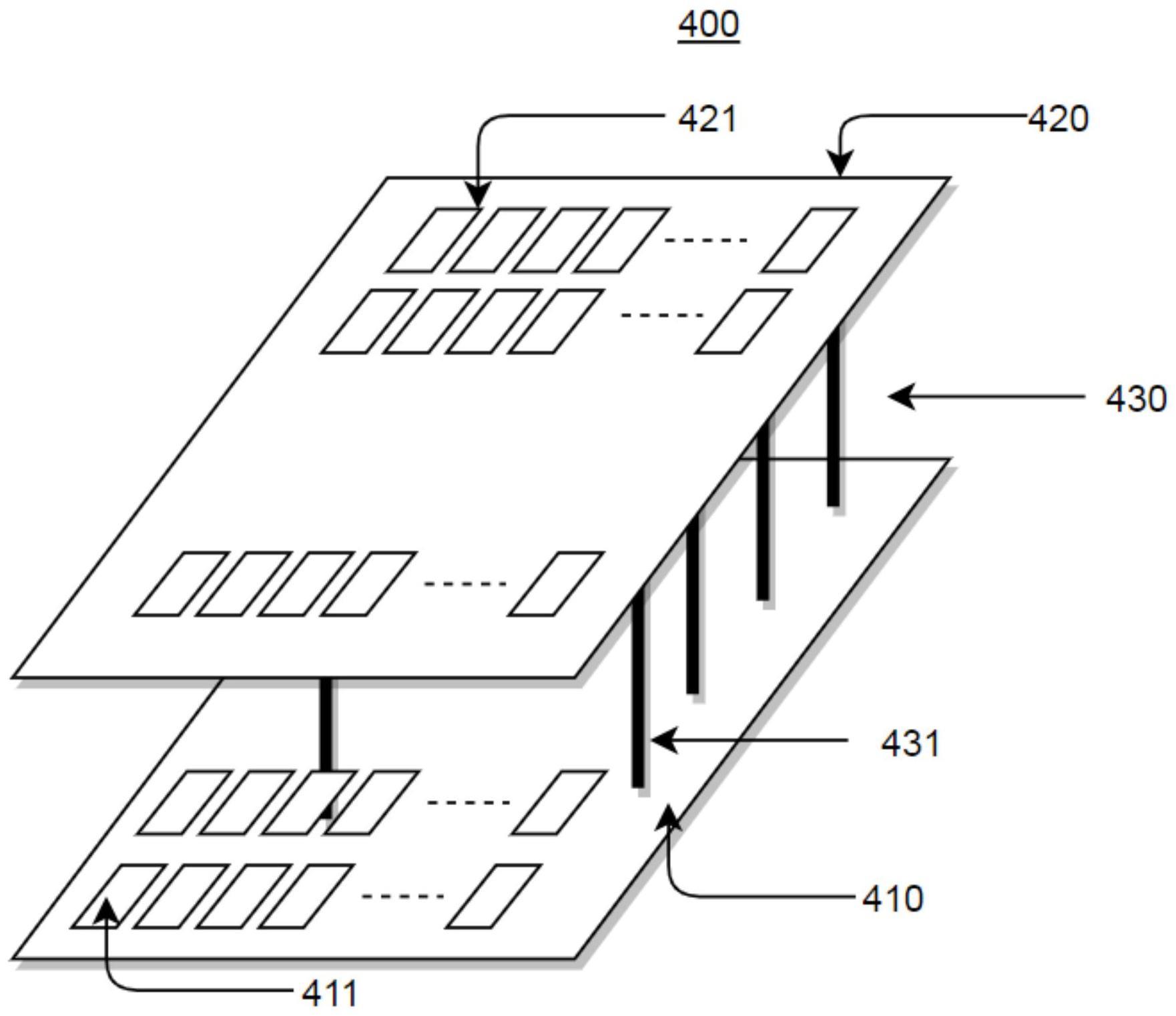

12、在本技术一个可选实施例中,计算单元包括多个矩阵排列的子计算单元,存储单元包括多个矩阵排列的子存储单元,层间通孔分别与子计算单元和子存储单元一一对应。

13、在本技术一个可选实施例中,逻辑器件层还包括:

14、hbm连接单元,用于连接外接半导体器件。

15、在本技术一个可选实施例中,逻辑器件层和/或存储器件层的数量为多个,相邻两个器件层之间均设置有包含层间通孔的孤岛隔离层;其中,器件层为逻辑器件层或存储器件层中的至少一种。

16、在本技术一个可选实施例中,层间通孔的径长为小于或等于80纳米,和/或,层间通孔的深度为小于或等于500纳米。

17、在本技术一个可选实施例中,该半导体器件采用如下方法制备:

18、在衬底表面制备逻辑器件层;

19、在逻辑器件层表面制备孤岛隔离层;

20、采用低温退火工艺在孤岛隔离层表面制备存储器件层。

21、本技术实施例的第二个方面,提供了一种集成芯片,包括:

22、芯片本体;

23、如上任一项的半导体器件,设置于芯片本体。

24、本技术实施例的第三个方面,提供了一种电子设备,包括:

25、如上的集成芯片。

26、本技术实施例的第四个方面,提供了一种存算调度方法,应用于如上任一项的半导体器件,该方法包括:

27、确定待处理任务所需的计算量与存储量;

28、根据计算量从半导体器件中的多个计算单元调用目标子计算单元;

29、根据存储量从半导体器件中的多个存储单元调用目标子存储单元;

30、基于目标子计算单元与目标子存储单元对待处理任务进行处理。

31、在本技术一个可选实施例中,上述存算调度方法还包括:

32、确定半导体器件对待测信号的损耗模型;

33、对应的,在基于目标子计算单元与目标子存储单元对待处理任务进行处理之后,该存算调度方法还包括:

34、基于损耗模型对处理后的结果信号进行校准,得到目标信号。

35、在本技术一个可选实施例中,上述确定半导体器件对待测信号的损耗模型,包括:

36、构建半导体器件对应的半导体器件模型;

37、基于测试信号确定半导体器件模型中针对测试信号的信号噪声;信号噪声包括:层间通孔电阻、信号延时、信号衰减中的至少一种。

38、基于信号噪声与半导体器件模型构建损耗模型。

39、在本技术一个可选实施例中,上述存储单元包括:独立存储单元与共享存储单元;该存算调度方法还包括:

40、确定待处理任务中数据的交互类型;其中,交互类型至少包括:互联交互与片内交互;

41、根据交互类型从存储单元中调用独立存储单元或共享存储单元。

42、本技术实施例的第五个方面,提供了一种多层神经网络训练方法,使用如上任一项所述的半导体器件进行分布式计算和/或存储。

43、本技术实施例提供的半导体器件包括逻辑器件层,所述逻辑器件层包括多个计算单元;在所述逻辑器件层上的孤岛隔离层;在所述孤岛隔离层上形成的存储器件层,所述存储器件层包括多个存储单元;多个层间通孔,所述多个层间通孔实现所述逻辑器件层与所述存储器件层电连接。,通过这种器件结构,第一方面,本技术实施例无需传统方式中的逻辑单元(例如图3中的logic die)、hbm phy高速接口以及互联层(例如图3中的interposersi)等,通过电性的层间通孔即可实现计算单元与存储单元的互联,大大降低了成本;第二方面,本技术实施例中的存储单元处于储存器件层与计算单元处于逻辑器件层,两者均属于半导体器件中功能层级,距离较短,相比于传统方式中通过芯片外的介质芯片(例如图3中的logic die和interposer si)的远距离传输效率更高,同时,较短的距离可以降低提高信号的传输损耗,提高信号的传输速率与传输质量,进一步提高半导体器件的计算效率,可适用于大型模型训练与预测的需求;第三方面,本技术实施例逻辑器件层与存储器件层间隔距离短,即孤岛隔离层厚度较小,层间通孔的开设难度小,容易形成良率较高的层间通孔,在保障器件性能的前提下进一步降低了工艺制备难度,大大降低了成本;第四方面,本技术实施例逻辑器件层与存储器件层间隔距离短,孤岛隔离层厚度较小,较小内径的层间通孔即可满足计算单元与存储单元之间的互联以及例如电容等需要开槽的功能器件的制备,层间通孔内径越小,器件表面的平整度越高,可以很大程度上避免传统方式中由于必须开始较大内径的层间通孔而引起的表面翘曲等情况的发生,本技术实施例提供的半导体结构表面更为平整,工艺制备要求更低,良品率更高;第五方面,本技术实施例提供的半导体器件在孤岛隔离层开设有连通计算单元与存储单元的层间通孔,可以基于该层间通孔同时实现在逻辑器件层制备例如cmos器件中的电容极板等,大大降低了工艺复杂度与工艺难度。

- 还没有人留言评论。精彩留言会获得点赞!