一种基于标准状态机功能扩展的快速配置寄存器方法与流程

本发明涉及超大规模数字集成电路测试领域,具体涉及一种基于标准状态机功能扩展的快速配置寄存器方法。

背景技术:

1、芯粒技术作为芯片算力提升和先进工艺节点遭遇瓶颈的解决方案,通过将不同工艺的模块化、小型化的芯粒堆叠成芯片,以用较低的成本获得较高的性能,同时改善芯片的良率。芯粒技术极具前景,其应用以及面向芯粒的研究越来越广泛。伴随着芯粒低成本、高良率以及高性能等特点,芯粒也存在堆叠芯片内部互连情况复杂、io数目庞大的问题,给测试带来了极大的挑战。

2、针对芯粒绑定后的互连测试问题,目前主流的测试方案都是基于ieee 1149、ieee1687以及ieee 1838三大标准进行设计并改进,并设计配置电路对改进的功能进行控制。通常为了一致性的需要,配置电路的控制往往采用新增指令或新增状态机状态的方法,但这会大大增加配置时间。例如使用菊花链连接n个芯粒,单芯粒内有k个配置寄存器时,新增指令增加的配置时间至少为o(4n+6)、在新增指令不能满足寄存器配置需要时,新增的配置时间至多为o(4n+kn+6+5),新增状态机状态的配置时间为o(kn+7)。

技术实现思路

1、本发明的目的在于提供一种基于标准状态机功能扩展的快速配置寄存器方法,本发明该方法可以适用于测试问题中广泛场景,用以快速配置相关寄存器。当标准测试结构在特定场景下缺乏测试效率时,往往需要加入配置寄存器,对配置寄存器进行配置会增加额外的时间,本发明提出的快速配置寄存器方法,相较于传统的新增指令和新增状态机状态两种方法,在大部分应用场景中都具有配置时间较短的优势。在改进的互连测试结构场景下,本发明提出的方法硬件开销小、配置时间短。

2、为解决上述技术问题,本发明提供了一种基于标准状态机功能扩展的快速配置寄存器方法,包括如下步骤:

3、步骤1:在定义的配置周期内从tdi端口输入3’b000对状态机进行默认配置;

4、步骤2:将指令寄存器配置为双芯粒工作状态,输入8位指令,即在shift-ir状态下从tdi端口输入8’b10101000;

5、步骤3:进行扫描链的配置,配置寄存器链长为4;输入4位配置信号,即在update-ir、run-test/idle、select-dr、capture-dr四个状态下从tdi端口输入4’b1001进行配置;

6、步骤4:输入测试数据,对左侧芯粒chiplet0的扫描链和右侧芯粒chiplet1的互连输出引脚进行全0信号赋值;其中有24个信号为低有效使能信号;

7、步骤5:全0信号赋值经过capture-shift-update即csu周期后,测试数据通过互连线从互连的芯粒chiplet0或chiplet1的output引脚赋值到芯粒chiplet1或chiplet0的input引脚,此时扫描链上存储有792位全0数据;

8、步骤6:此时第一次移位赋值更新结束,为保持下一次移位赋值的互连测试状态,在两次移位赋值中经过配置状态时,与步骤3相同,继续从tdi端口输入4’b1001进行配置;

9、步骤7:从tdi端口输入792位测试数据,其中使能信号位赋0,以移出步骤5存储的792位全0数据;此时检验测试数据输出tdo的值是否为步骤5赋值更新后的全0数据;

10、步骤8:与步骤5-7同理,数据双向update后,为保持下一次移位赋值的互连测试状态,在两次移位赋值中经过配置状态时,与步骤3相同,从tdi端口输入4’b1001进行配置,随后从tdi端口输入792位测试向量以移出步骤7存储并update后的792位数据,输入与步骤7的赋值奇偶相反的向量,并检验测试数据输出tdo的值;

11、步骤9:与步骤5-7同理,数据双向update后,在下一次进入移位赋值状态之前,在最后四个配置状态,即update-dr、run-test/idle、select-dr和capture-dr四个状态,从tdi端口输入4’b1001进行配置,以保持互连测试状态,随后从tdi端口输入588位全0测试向量,以移出右侧芯粒chiplet1的扫描链以及左侧芯粒chiplet0的互连输入引脚的边界扫描单元存储值;并检验测试数据输出tdo的值;

12、步骤10编写比较逻辑,期望测试数据输出为tdo_exp,在非观测tck周期内,赋tdo_exp为1’bx;每个观测tck周期内当tdo与tdo_exp不匹配时,比较结果compare为1,否则compare为0;32位信号compare_count记录compare为1的周期数,即从测试开始的匹配失败次数。

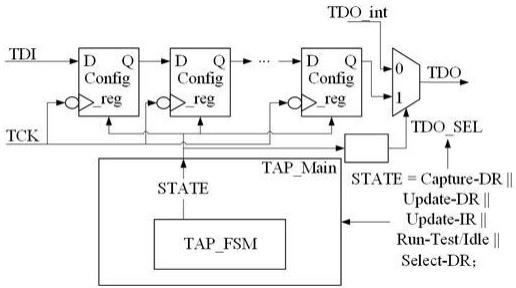

13、优选的,将标准tap状态机,划分为可配置状态和不可配置状态;其中capture-dr、update-dr、update-ir、run-test/idle和select-dr五个状态划分为可配置状态,其余状态为不可配置状态。

14、优选的,所述芯粒chiplet0和芯粒chiplet1为两个相同的768引脚芯粒,其中384引脚为input,384引脚为output;两个芯粒通过192个input引脚和192个output引脚互相通信。

15、优选的,每个芯粒内配置寄存器链长为2,通过左侧芯粒chiplet0和右侧芯粒chiplet1互连,使其芯片的配置寄存器链长为4。

16、优选的,假设配置寄存器链长度为n,正常的两次移位赋值操作时,从update-ir/update-dr到capture-dr需经过4个周期,若测试电路此时工作在配置寄存器控制的某个状态,则需要增加状态机中配置状态周期数为n个周期;

17、若测试电路工作在无需配置寄存器控制的标准状态,对应为配置寄存器全0的默认状态,由于寄存器初始值为0,首次配置全0或前一次配置为全0时,不需要增加状态机配置状态的周期数,仍使配置状态的周期数为4即可。

18、优选的,在需要增加配置状态周期数时,若此时需要6个配置周期,则应在update-ir/update-dr->run-test/idle->run-test/idle->run-test/idle ->select-dr->capture-dr六个周期中完成配置;其中“->”表示按时间顺序的状态变化。

19、本发明与现有技术相比,具有如下有益效果:

20、本发明提出了一种基于标准状态机功能扩展的快速配置寄存器方法。该快速配置寄存器方法以ieee 1149.1为基础,关键在于扩大了ieee 1149.1规定的tap fsm的功能;以相关的寄存器(数据寄存器、指令寄存器)为对象,可将标准规定的fsm中的状态分为操作周期(csu period,capture-shift-update period)以及空闲周期(非csu period),快速配置寄存器方法即在空闲周期的部分状态对相关控制寄存器进行配置操作。本发明提出的快速配置方法可以在两次操作周期之间对相关寄存器快速配置,在不增加额外的端口、不增加额外的指令和状态机状态的基础上,不影响原有的数据寄存器赋值和指令寄存器赋值,同时对配置寄存器进行快速赋值。该方法面向一种改进的互连测试结构而设计,但该发明提出的配置方法具有通用性,可广泛适用于基于ieee 1149设计的测试结构。改进的互连测试结构中,可对片内扫描链配置寄存器进行配置,以缩短扫描链的配置时间。

- 还没有人留言评论。精彩留言会获得点赞!