布线方法及装置、计算装置和存储介质与流程

本发明涉及集成电路仿真,特别涉及一种应用于集成电路仿真设计的布线方法及装置、计算装置和存储介质。

背景技术:

1、随着集成电路的发展,芯片规模不断增大、工艺需求不断增加,eda(electronicsdesign automation,电子设计自动化)工具成了芯片设计领域必不可少的辅助工具。

2、在现有技术中,布线阶段eda工具的首要目标是实现不同模块之间的连接关系。eda工具在实现连接关系的同时还需要满足设计规则。但是现有的布线方法不能很好的兼顾连接关系和设计规则。

3、因此,希望有一种新的布线方法及装置、计算装置和存储介质,能够解决上述问题。

技术实现思路

1、鉴于上述问题,本发明的目的在于提供一种布线方法及装置、计算装置和存储介质,从而减少设计规则违反。

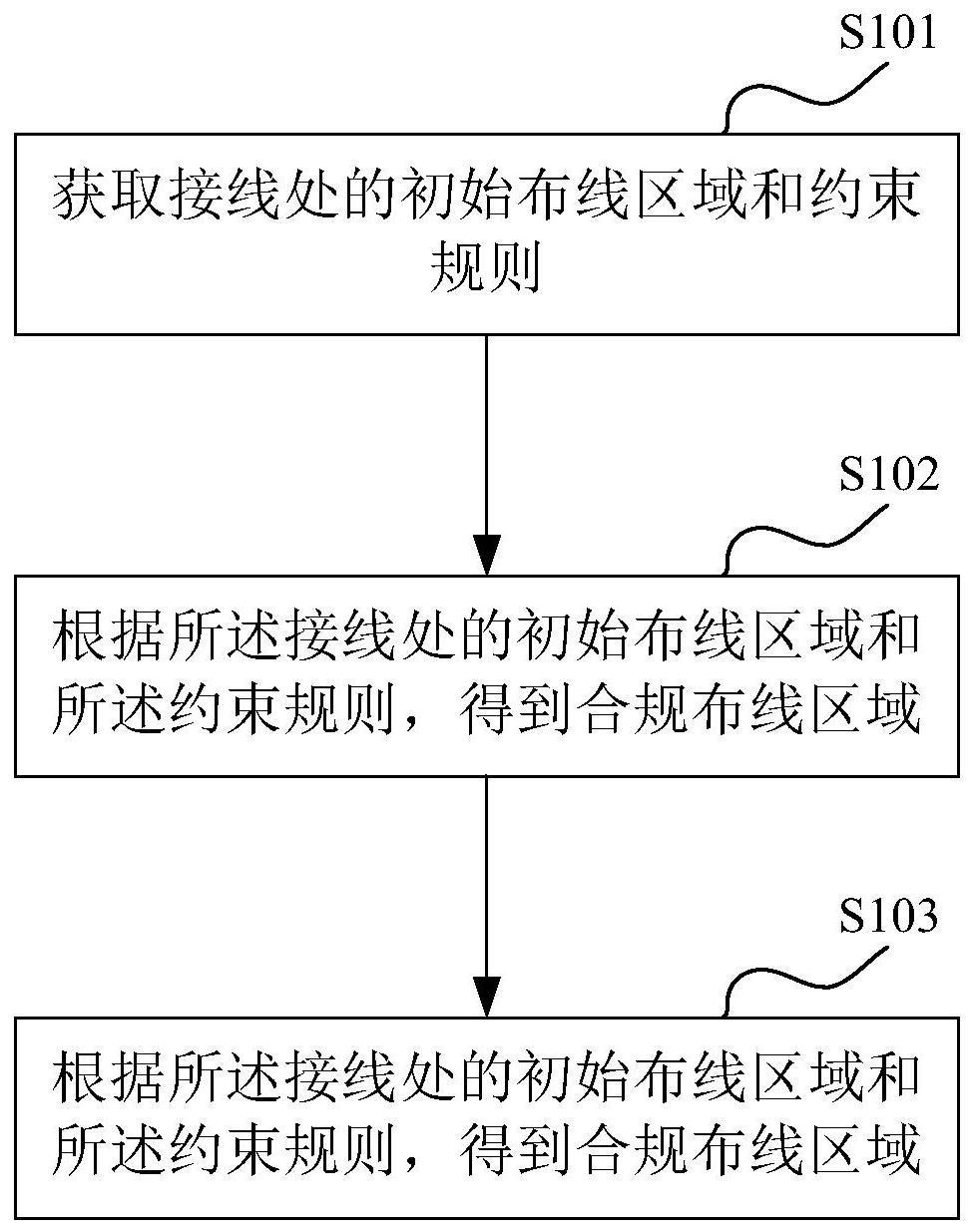

2、根据本发明的一方面,提供一种布线方法,应用于集成电路仿真设计,所述布线方法包括:获取接线处的初始布线区域和约束规则;根据所述接线处的初始布线区域和所述约束规则,得到合规布线区域;以及根据所述合规布线区域进行布线,其中,所述合规布线区域位于所述初始布线区域中。

3、可选地,所述接线处包括引脚区域。

4、可选地,所述根据所述接线处的初始布线区域和所述约束规则,得到合规布线区域包括:

5、根据所述接线处的初始布线区域和所述约束规则,获取第一合规布线区域;以及

6、根据所述接线处的初始布线区域和所述约束规则,获取第二合规布线区域,

7、其中,所述第一合规布线区域允许沿第一方向布线;所述第二合规布线区域允许沿第二方向布线。

8、可选地,所述初始布线区域为矩形;

9、所述根据所述接线处的初始布线区域和所述约束规则,得到合规布线区域包括:

10、根据所述初始布线区域和所述约束规则,得到新建布线区域;以及

11、根据所述初始布线区域、所述新建布线区域和所述约束规则,得到第一区域、第二区域、第三区域和第四区域,所述合规布线区域包括所述第一区域、所述第二区域和所述第三区域,

12、其中,所述新建布线区域位于所述初始布线区域中;所述新建布线区域为矩形,所述新建布线区域的边界与相邻的所述初始布线区域的边界间的距离为第一距离;

13、所述第一区域允许在x方向上布线,允许在y方向上布线;

14、所述第二区域允许在x方向上布线,禁止在y方向上布线;

15、所述第三区域禁止在x方向上布线,允许在y方向上布线;

16、所述第四区域禁止在x方向上布线,禁止在y方向上布线。

17、可选地,所述约束规则包括约束距离;

18、所述初始布线区域为矩形,包括上边界、下边界、左边界和右边界;

19、所述第二区域包括位于所述上边界、第一边界、第三边界和第四边界之间的区域,以及位于所述下边界、第二边界、所述第三边界和所述第四边界之间的区域;

20、所述第三区域包括位于所述左边界、所述第三边界、所述第一边界和所述第二边界之间的区域,以及位于所述右边界、所述第四边界、所述第一边界和所述第二边界之间的区域,

21、其中,所述第一边界位于所述上边界和所述下边界之间,且平行于所述上边界;所述第一边界与所述上边界之间的距离为所述约束距离与第一距离的和;

22、所述第二边界位于所述上边界和所述下边界之间,且平行于所述上边界;所述第二边界与所述下边界之间的距离为所述约束距离与所述第一距离的和;

23、所述第三边界位于所述左边界和所述右边界之间,且平行于所述左边界;所述第三边界与所述左边界之间的距离为所述约束距离与所述第一距离的和;

24、所述第四边界位于所述左边界和所述右边界之间,且平行于所述左边界;所述第四边界与所述右边界之间的距离为所述约束距离与所述第一距离的和。

25、可选地,所述布线方法还包括:

26、获取布线参数,所述布线参数包括布线宽度,

27、其中,所述第一距离为所述布线宽度的一半。

28、可选地,所述布线方法还包括:

29、获取所述接线处相邻的候选连接处;

30、根据所述合规布线区域,从所述相邻的候选连接处中选择一个候选连接处作为连接点;以及

31、在所述接线处和所述连接点间布线。

32、可选地,所述布线方法还包括:

33、获取与所述接线处相邻的多个候选连接处;

34、遍历所述多个候选连接处,分别获取所述候选连接处的代价值;以及

35、选取代价值最小的候选连接处作为连接点,并在所述接线处和所述连接点之间布线,

36、其中,所述遍历包括在x方向上遍历和在y方向上遍历;

37、在x方向上遍历时,在所述候选连接处全部处于所述第二区域和/或所述第一区域时,所述候选连接处的代价值为原始代价值;在所述候选连接处的至少一部分处于所述第三区域和/或所述第四区域时,所述候选连接处的代价值为所述原始代价值加上惩罚值;

38、在y方向上遍历时,在所述候选连接处全部处于所述第三区域和/或所述第一区域时,所述候选连接处的代价值为原始代价值;在所述候选连接处的至少一部分处于所述第二区域和/或所述第四区域时,所述候选连接处的代价值为所述原始代价值加上惩罚值;

39、所述原始代价值大于零;所述惩罚值大于零。

40、可选地,在布线层为多层时,所述布线方法还包括:

41、读取布线参数,获取各个所述布线层对应的约束规则;以及

42、根据所述接线处的初始布线区域和所述接线处所在布线层对应的约束规则,得到所述合规布线区域。

43、根据本发明的另一方面,提供一种布线装置,应用于集成电路仿真设计,所述布线装置包括:获取单元,用于获取接线处的初始布线区域和约束规则;约束单元,用于根据所述接线处的初始布线区域和所述约束规则,得到合规布线区域;以及布线单元,用于根据所述合规布线区域进行布线,其中,所述合规布线区域位于所述初始布线区域中。

44、根据本发明的又一方面,提供一种计算装置,包括处理器;存储器,用于存储一个或多个程序,其中,当所述一个或多个程序被所述处理器执行,使得所述处理器实现如上所述的布线方法。

45、根据本发明的再一方面,提供一种计算机可读存储介质,其上存储有计算机程序,其中,该程序被处理器执行时实现如上所述的布线方法。

46、根据本发明实施例的布线方法及装置、计算装置和存储介质,根据接线处的初始布线区域和约束规则得到合规布线区域,在合规布线区域中任意布线都不会违反规则,能够方便、高效且合规的实现布线。

47、进一步地,根据接线处的初始布线区域和约束规则得到合规布线区域,在合规布线区域中产生的布线能够满足minedgelength约束,进而提高芯片的良率。

48、进一步地,在不同的布线方向上对应生成合规布线区域,能够得到范围更精准的合规布线区域,并且使得在沿不同方向布线时,有对应的准确无误的合规布线区域。

49、进一步地,依据边界分别确定x方向上可以/不可以出线的区域和y方向上可以/不可以出线的区域,使得生成合规布线区域的可操作性强,有利于计算机自动执行,且得到的合规布线区域的范围更精准。

50、进一步地,遍历当前节点的邻居节点的过程中,根据遍历方向和邻居节点的所属的区域更新代价,若邻居节点在该区域中不能布线,给当前邻居节点代价增加一个惩罚值,反之则不增加惩罚值,能够找到最优的邻居节点,使得整体布线更加合理。

- 还没有人留言评论。精彩留言会获得点赞!