量子芯片的控制方法、装置以及量子计算机与流程

本发明涉及量子计算,尤其是涉及一种量子芯片的控制方法、装置以及量子计算机。

背景技术:

1、量子计算与量子信息是一门基于量子力学的原理来实现计算与信息处理任务的交叉学科,与量子物理、计算机科学、信息学等学科有着十分紧密的联系,在最近二十年有着快速的发展。因数分解、无结构搜索等场景的基于量子计算机的量子算法展现出了远超越现有基于经典计算机的算法的表现,也使这一方向被寄予了超越现有计算能力的期望。由于量子计算在解决特定问题上具有远超经典计算机性能的发展潜力,而为了实现量子计算机,需要获得一块包含有足够数量与足够质量量子比特的量子芯片,并且能够对量子比特进行极高保真度的量子逻辑门操作与读取。

2、量子芯片之于量子计算机就相当于cpu之于传统计算机,量子芯片是量子计算机的核心部件,量子芯片就是执行量子计算的处理器,量子芯片上集成有多个一一对应的且相互耦合的量子比特和读取腔。每一片量子芯片在正式上线使用前,均需要对量子芯片进行测试表征。量子计算机还包括为量子芯片提供测控环境的测控系统。该测控系统主要包括位于室温层的硬件设备和位于稀释制冷机内的低温器件和信号传输线。量子芯片封装完毕之后,被固定在稀释制冷机最下层的极低温层,通过层与层之间的同轴线最终连接至室温的硬件设备。该测控系统中,在对量子比特的量子态进行调控时,主要用到两类线路,一类是用于对量子比特的量子态进行驱动的第一类传输线(也即量子态控制线),另一类是用于对量子比特的频率进行调控的第二类传输线(也即频率控制线)。

3、在基于可调耦合器的量子比特扩展架构中,两个量子比特间可通过一个固定的电容耦合以及一个可以调节耦合系数的可调耦合器实现耦合,可调耦合器与量子比特的结构相似,区别在于可调耦合器不具有量子态控制线以及可以直接读取信息的谐振腔。为了避免相邻的量子比特和可调耦合器之间频率相差过小导致共振等问题,一般在分配量子比特和可调耦合器的工作频率时,会将可调耦合器的频率设置的较高,以图1中示出的量子芯片为例,其中q0、q1、q2、q3、q5、q6为量子比特,c01、c12、c23、c03、c15、c56、c26为可调耦合器,可调耦合器的工作频率可以设置在6-8ghz的范围内,量子比特的工作频率则可设置在4-5ghz的范围内,并且,相邻的两个量子比特之间的频率也呈现高、低频变化,例如,若量子比特q0设置为高频比特,那么量子比特q1设置为低频比特,量子比特q2和量子比特q5则需要设置为高频比特,其中,高频比特的工作频率高于低频比特的工作频率。这种量子芯片结构参数的设计优点是避免了相邻量子比特之间的共振影响,但是在实际应用时会产生另一个问题,还是以图1为例,由于量子比特q0和量子比特q2都是高频比特,在其中一个量子比特(假设是量子比特q0)被激发到激发态时,由于这两个量子比特的工作频率可能会被分配的很接近,量子比特q0的量子态会泄露到量子比特q2中,也即量子比特q0的量子态从激发态变成基态,而量子比特q2在未接收到任何量子态控制信号时变为激发态,这种情况我们称为量子态泄露。一旦出现量子态泄露,会导致量子计算任务出现严重错误。

4、因此,提出一种可以避免出现量子态泄露的方案,成为本领域亟待的问题。

5、需要说明的是,公开于本技术背景技术部分的信息仅仅旨在加深对本技术一般背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种量子芯片的控制方法、装置以及量子计算机,用于解决现有技术中量子芯片存在量子态泄露的问题。

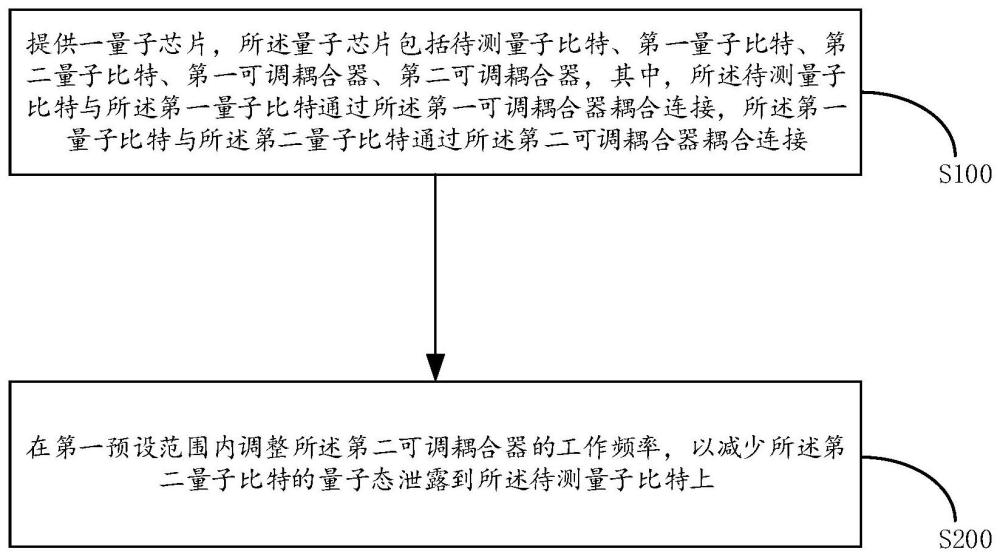

2、为了解决以上技术问题,本发明提出一种量子芯片的控制方法,包括:

3、提供一量子芯片,所述量子芯片包括待测量子比特、第一量子比特、第二量子比特、第一可调耦合器、第二可调耦合器,其中,所述待测量子比特与所述第一量子比特通过所述第一可调耦合器耦合连接,所述第一量子比特与所述第二量子比特通过所述第二可调耦合器耦合连接;

4、在第一预设范围内调整所述第二可调耦合器的工作频率,以减少所述第二量子比特的量子态泄露到所述待测量子比特上。

5、可选地,所述方法还包括:

6、获取所述待测量子比特与所述第二量子比特之间的等效耦合强度;

7、若所述等效耦合强度大于预设阈值,则执行所述在第一预设范围内调整所述第二可调耦合器的工作频率。

8、可选地,所述待测量子比特与所述第二量子比特之间的等效耦合强度通过以下公式获取:

9、

10、其中,gq0,q2为所述待测量子比特与所述第二量子比特之间的等效耦合强度,ωq0为所述待测量子比特的频率,ωq1为所述第一量子比特的频率,ωq2为所述第二量子比特的频率,ωc01为所述第一可调耦合器的频率,ωc12为所述第二可调耦合器的频率,gq0,c01为所述待测量子比特与所述第一可调耦合器之间的耦合强度,gq1,c01为所述第一量子比特与所述第一可调耦合器之间的耦合强度,gq1,c12为所述第一量子比特与所述第二可调耦合器之间的耦合强度,gq2,c12为所述第二量子比特与所述第二可调耦合器之间的耦合强度,gq0,q1为所述待测量子比特与所述第一量子比特之间的耦合强度,gq1,q2为所述第一量子比特与所述第二量子比特之间的耦合强度。

11、可选地,所述等效耦合强度的预设阈值根据所述待测量子比特上当前执行的量子线路的长度确定。

12、可选地,所述预设阈值的大小与所述待测量子比特上当前执行的量子线路的长度呈反相关。

13、可选地,所述在第一预设范围内调整所述第二可调耦合器的工作频率,包括:

14、在所述第一预设范围内调整所述第二可调耦合器的工作频率,获取所述第二量子比特与所述待测量子比特之间的频率差值随所述第二可调耦合器的工作频率的调整量的第一变化情况;

15、基于所述第一变化情况获取所述第二量子比特与所述待测量子比特之间的频率差值的极大值点对应的所述第二可调耦合器的工作频率的调整量为第一调整量;

16、利用所述第一调整量调整所述第二可调耦合器的频率。

17、可选地,所述在第一预设范围内调整所述第二可调耦合器的工作频率,包括:

18、获取所述第二量子比特处于|1>态的概率随所述第二可调耦合器的工作频率的调整量的第二变化情况,其中,所述第二量子比特的初始状态为|0>态;

19、基于所述第二变化情况获取所述第二量子比特处于|1>态的概率的极小值点对应的所述第二可调耦合器的工作频率的调整量为第二调整量;

20、利用所述第二调整量调整所述第二可调耦合器的频率。

21、可选地,所述在第一预设范围内调整所述第二可调耦合器的工作频率,包括:

22、获取所述第二量子比特处于|0>态的概率随所述第二可调耦合器的工作频率的调整量的第三变化情况,其中,所述第二量子比特的初始状态为|0>态;

23、基于所述第三变化情况获取所述第二量子比特处于|0>态的概率的极大值点对应的所述第二可调耦合器的工作频率的调整量为第三调整量;

24、利用所述第三调整量调整所述第二可调耦合器的频率。

25、可选地,所述第一预设范围根据所述第一量子比特以及所述第二量子比特的频率确定。

26、基于同一发明构思,本发明还提出一种量子芯片的控制装置,包括:

27、量子芯片提供单元,用于提供一量子芯片,所述量子芯片包括待测量子比特、第一量子比特、第二量子比特、第一可调耦合器、第二可调耦合器,其中,所述待测量子比特与所述第一量子比特通过所述第一可调耦合器耦合连接,所述第一量子比特与所述第二量子比特通过所述第二可调耦合器耦合连接;

28、工作频率调整单元,用于在第一预设范围内调整所述第二可调耦合器的工作频率,以减少所述第二量子比特的量子态泄露到所述待测量子比特上。

29、基于同一发明构思,本发明还提出一种量子控制系统,利用上述特征描述中任一项所述的量子芯片的控制方法,或包括上述特征描述中所述的量子芯片的控制装置。

30、基于同一发明构思,本发明还提出一种量子计算机,包括上述特征描述中所述的量子控制系统。

31、基于同一发明构思,本发明还提出一种可读存储介质,其上存储有计算机程序,所述计算机程序被一处理器执行时能实现上述特征描述中任一项所述的量子芯片的控制方法。

32、与现有技术相比,本发明具有以下有益效果:

33、本发明提出的量子芯片的控制方法,在第一预设范围内调整所述第二可调耦合器的工作频率,由于在调整所述第二可调耦合器的工作频率时,会影响所述第二量子比特的频率,可以理解为调整所述第二可调耦合器的工作频率会修正所述第二量子比特的频率,从而抑制量子态泄露现象的出现。通过本技术的方案有效解决了现有技术中量子芯片存在的量子态泄露的问题,在一定程度上提高了量子计算机执行结果的准确性。

34、本发明提出的量子芯片的控制装置、量子控制系统、量子计算机以及可读存储介质,与所述量子芯片的控制方法属于同一发明构思。

- 还没有人留言评论。精彩留言会获得点赞!