硬件加速单元、硬件加速方法、芯片及存储介质与流程

本发明属于半导体设计领域,尤其涉及一种采用硬件加速单元提高芯片运行效率的方法,具体为一种硬件加速单元、硬件加速方法、芯片及存储介质。

背景技术:

1、汽车应用涉及较多的三相无刷电机控制应用场景,例如:水泵、风扇、压缩机等,需使用foc算法进行无刷电机的控制,该控制涉及矢量控制,需使用大量的除法、开根号、开平方根、三角函数等数学运算。

2、此类汽车电机应用所使用的计算控制芯片主频一般不高于48m,不同处理器内核对矢量控制所需的大量计算支持能力不足,主要体现在除法、开根号运算、开平方根、三角函数执行时间不能满足应用需求,或内核本身无法进行此类运算。

3、此类汽车电机应用所使用的计算控制芯片不带浮点运算单元,实际的电机矢量控制算法实现方案中,一般采用定点格式实现。一般而言,使用c语言编程时采用定标法来确定小数,此时变量定义为整型变量(int16或int32),只是通过假定小数点位于二进制码的哪一位来确定小数的精度。当用低1位表示小数时称为q1,用低15位表示小数时称为q15。int16所能表示的q格式范围为q0~q15,int32所能表示的q格式范围为q0~q31,对数据的放大的倍数为2,2^2,2^3,2^4,…。

4、因此,对于汽车应用涉及的三相无刷电机控制场景,主要存在如下缺陷:

5、1.汽车计算控制芯片内核对电机矢量控制所需的运算类型支持不足:计算执行时间过长或不支持。

6、2.在低成本却需要高性能的应用场景下,例如:水泵、风扇、压缩机等电机应用,需要使用复杂的矢量控制算法,导致中断负载率过高,不能满足应用需求。

7、3.少数汽车计算控制芯片包含除法和平方和开根号运算,但不能同时执行。

8、4.现有方案中少数厂家除法加速引擎支持32 bits /32 bits 除法,而实际的低成本电机场景中由于计算控制芯片的算力有限,且不支持浮点运算,因此必须采用低定点格式方式实现,一般采用q15或q14格式,采用32 bits /32 bits除法必要性不高,且会增加单个除法的计算时长。

9、5.现有方案中少数厂家平方和开根号加速引擎中用于计算两个32 bits有符号输入的计算,必要性不高,且会增加单次计算的时长。

10、6.现有方案不支持完整的电机控制支持所需的运算引擎方案:除法、开根号、开平方根、正弦、余弦、反正切等运算。

技术实现思路

1、为克服上述现有技术的不足,本发明提供一种采用硬件加速单元提高芯片运行效率的方法及装置,用以解决上述至少一个技术问题。

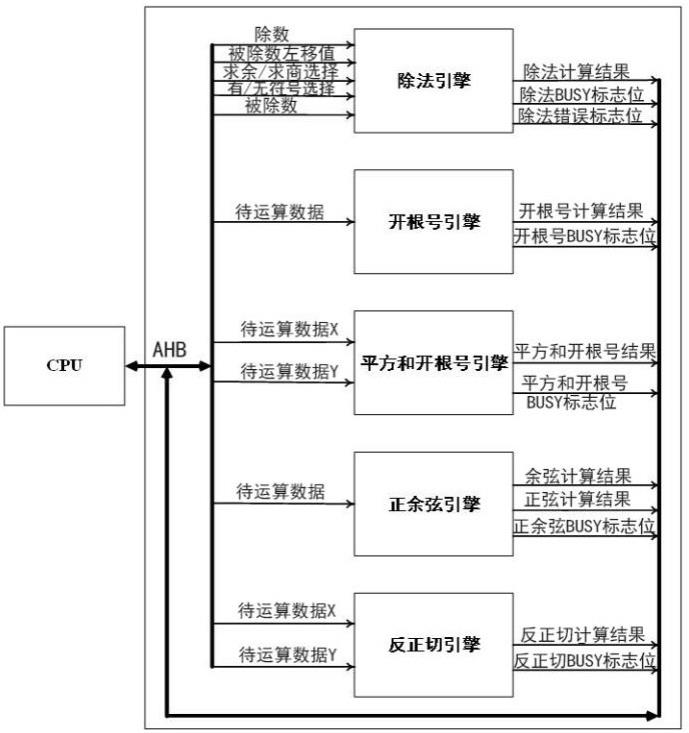

2、根据本发明说明书的一方面,提供一种硬件加速单元,包括多个并行运算的加速引擎,每一加速引擎实现一不同的数学运算,用于提供并行的除法运算、开根号运算、平方和开根号运算、正余弦运算或反正切运算;多个所述加速引擎分别通过总线与cpu进交互,且每一加速引擎对应一数据输入单元,用于按照运算顺序依次向各个数据输入单元进行数据写入,各个加速引擎根据运算顺序依次在总线空闲状态时读取对应数据输入单元的数据并执行对应的数学运算。

3、上述技术方案包含完整的电机控制支持所需的运算引擎,可以提供硬件加速的除法、开根号、平方和开根号、正余弦、反正切等运算,且各加速引擎可以同时运行而不会相互干扰,实现并行运算,能够支持复杂的矢量控制算法,解决现有三相无刷电机控制时存在的计算执行时间过长或不支持的问题。

4、可选地,每个加速引擎配置有busy标志位。不同加速引擎计算过程中,通过busy标志位判定是否计算完成,busy标志位清零后即可从加速引擎中获取计算结果。

5、可选地,所述总线可为高级高性能总线(advanced high-performance bus,ahb)。_

6、作为进一步的技术方案,用于除法运算的加速引擎,执行如下指令:

7、判断当前总线是否处于空闲状态;

8、在当前总线处于空闲状态时,判断输入除数是否为零;

9、在输入除数不为零时,对输入的除数和被除数取绝对值并进行除数比特流处理;

10、基于比特流处理后的数据,进行移位除法运算;

11、在输入的移位值位于可配置范围内时,进行除法递归计算;

12、组合不同迭代过程中的值,输出除法计算的商和余数。

13、上述技术方案用于除法的硬件加速计算,可以实现支持32位/24位的有、无符号除法,支持商和余数的计算,且包含除零标志指示,在准确可靠的前提下兼顾除法执行效率。

14、可选地,用于除法运算的加速引擎主要包括以下功能:有符号或者无符号整数除法运算;支持商和余数的计算;支持移位除法运算,方便不同定点数格式计算;写被除数寄存器后开始执行除法运算;除数为零时会产生除零错误标志位;32位被除数输入,24位除数输入,32位结果输出。

15、进一步地,所述加速引擎支持的除法计算公式为:x / y,x % y,(x<<z) / y,(x<<z) % y;其中,“/”表示除法求商计算,“%”表示除法求余数计算,“<<”表示左移移位操作;x为32位被除数输入,有符号除法时被除数范围为-(2^31) ~ (2^31-1),无符号除法时被除数范围为0 ~ (2^32-1);y为24位除数输入,有符号除法时除数范围为-(2^23) ~ (2^23-1),无符号除法时除数范围为0 ~ (2^24-1);z为5位移位输入,范围为0 ~ 31。

16、作为进一步的技术方案,用于平方和开根号运算和反正切运算的加速引擎,均执行如下指令:

17、判断当前总线是否处于空闲状态;

18、在当前总线处于空闲状态时,获取输入数据并进行绝对值处理;

19、执行迭代计算,并在达到设定的迭代计算次数后,通过计算类型标注位区分是平方和开根号运算或反正切运算。

20、作为进一步的技术方案,在通过计算类型标注位判定为反正切运算时,用于反正切运算的加速引擎还执行如下指令:对迭代计算结果进行四象限及边界处理,并以反正切格式输出计算结果。

21、可选地,用于反正切运算的加速引擎,其主要功能是计算两个输入值之商的反正切角度,并根据两个输入值的正负号进行象限处理,输出定点数格式为q16的角度信号。

22、进一步地,所述加速引擎支持的反正切计算公式为:,其中,x,y为16位有符号数,范围为-(2^15) ~ (2^15-1),计算结果范围为(0~65535),重映射对应(0~360°)。

23、作为进一步的技术方案,在通过计算类型标注位判定为平方和开根号运算时,用于平方和开根号运算的加速引擎还执行如下指令:将输入数据写入寄存器,执行平方和开根号输出。

24、可选地,用于平方和开根号运算的加速引擎,其主要功能是计算两个输入值平方之和开根号的大小,广泛应用在电机矢量控制等高性能场景中,用于计算两个矢量电流或电压的幅值。

25、进一步地,所述加速引擎支持的平方和开根号计算公式为:,其中:x,y为16位有符号整数,范围为-(2^15) ~ (2^15-1)。

26、作为进一步的技术方案,用于正余弦运算的加速引擎,执行如下指令:

27、判断当前总线是否处于空闲状态;

28、在当前总线处于空闲状态时,获取输入数据并进行绝对值处理;

29、执行迭代角度查表,并在达到设定的迭代次数后,进行定点数格式处理,输出处理结果。

30、可选地,用于正余弦运算的加速引擎,其主要功能是计算角度的正余弦值大小,其中正余弦输入定点数格式为q16,输出定点数格式为q14。

31、进一步地,所述加速引擎支持的正余弦计算公式为:,,其中,x为16位无符号数,范围 (0~65535),重映射对应 (0~360°),正余弦运算输出为16位有符号数,范围(-16384 ~ 16383)重映射对应(-1 ~ 1)。

32、可选地,用于开根号运算的加速引擎,其主要功能是计算x的平方根值。

33、进一步地,所述加速引擎支持的开根号计算公式为,其中,x为32位无符号整数,范围为0 ~ (2^32-1)。

34、作为进一步的技术方案,所述数据输入单元为寄存器。

35、根据本发明说明书的一方面,提供一种硬件加速方法,采用所述的硬件加速单元实现,所述方法包括:

36、获取总线状态;

37、在总线处于空闲状态时,读取待运算数据;

38、执行与待运算数据对应的加速引擎,所述加速引擎包括用于除法运算的加速引擎、用于开根号运算的加速引擎、用于平方和开根号运算的加速引擎、用于正余弦运算的加速引擎和用于反正切运算的加速引擎;

39、读取加速引擎的计算结果。

40、根据本发明说明书的一方面,提供一种芯片,包括所述的硬件加速单元。

41、上述技术方案所设计的计算控制类芯片,适合支持复杂的矢量控制算法,能够降低系统中断负载率过高的现象,满足三相无刷电机矢量控制的应用场景需求。

42、根据本发明说明书的一方面,提供一种计算机可读存储介质,该计算机可读存储介质上存储有计算机程序,该计算机程序被处理器运行时执行所述的硬件加速单元,或者,执行所述的硬件加速方法的步骤。

43、与现有技术相比,本发明的有益效果在于:

44、1.本发明构建了包括多个可并行运算的加速引擎的硬件加速单元,多个加速引擎通过ahb总线与cpu进行交互,可以提供硬件加速的除法、开根号、开平方根、三角函数等运算,能够支持复杂的矢量控制算法,降低系统中断负载率,满足三相无刷电机的矢量控制需求。

45、2.本发明的各加速引擎可以同时运行而不会相互干扰,实现并行运算。

46、3.本发明的除法加速引擎可实现支持32位/24位的有、无符号除法,支持商和余数的计算,且包含除零标志指示,在准确可靠的前提下兼顾除法执行效率。

47、4.本发明的平方和开根号加速引擎用于计算两个矢量电流或电压的幅值,支持q0~q15格式,输入范围为-32768~32767,仅需一个32bit寄存器进行数据输入,通过减少配置寄存器个数相应的减少了整个计算所需的时钟周期。

48、5.本发明的正余弦计算在sin/cos加速引擎中实现,计算角度的正余弦值大小,其中正余弦输入定点数格式为q16,即输入范围为0~65536,输出定点数格式为q14,即输出范围为-16384~16383,正余弦计算输出可同时得到。

49、6.本发明的反正切加速引擎计算两个输入值之商的反正切角度,并根据两个输入值的正负号进行象限处理,输出定点数格式为q16的角度信号,即输出范围为0~65536。

- 还没有人留言评论。精彩留言会获得点赞!