一种FPGA详细布局方法及系统与流程

本发明属于可编程逻辑器件的软件设计领域,尤其是涉及一种fpga详细布局方法及系统。

背景技术:

1、fpga布局的目的是确定电路中的可编程逻辑块(clb)、输入/输出管脚(input/output block,iob)、存储器(bram)、数字信号处理(dsp)等逻辑单元在fpga芯片上的物理位置。布局是fpga cad流程中的一个重要阶段,其结果直接影响了电路的布通率和性能。随着fpga容量和复杂性的增加,高性能的fpga布局算法已成为当前cad领域的一个研究热点。提高fpga布局算法的性能,对于提升整个cad工具的水平,缩短应用电路的设计周期,具有十分重要的作用。

2、当前主流的fpga布局算法包含三个阶段:初始布局、全局布局和详细布局。初始布局阶段通过随机或模拟退火等方法,为布局的所有逻辑块分配初始的坐标位置。全局布局阶段通过求解数学方程的方法来最小化线长,求解方程之后得到的布局结果存在大量的逻辑块重叠,是非法的。因此需要再通过合法化移动来移开重叠的逻辑块,产生合法的布局结果。但这通常会导致布局质量的下降,如线长和延时的增加。详细布局阶段是对合法布局结果的进一步优化,进而提高电路的性能。目前详细布局采用较多的方法是模拟退火算法。但是模拟退火算法在详细布局中存在运行时间长,且容易陷入局部最优的问题。

技术实现思路

1、本发明所要解决的技术问题是针对当前详细布局效率较低的问题,提出了一种fpga详细布局方法及系统。

2、为解决上述技术问题,本发明所采用的技术方案是:

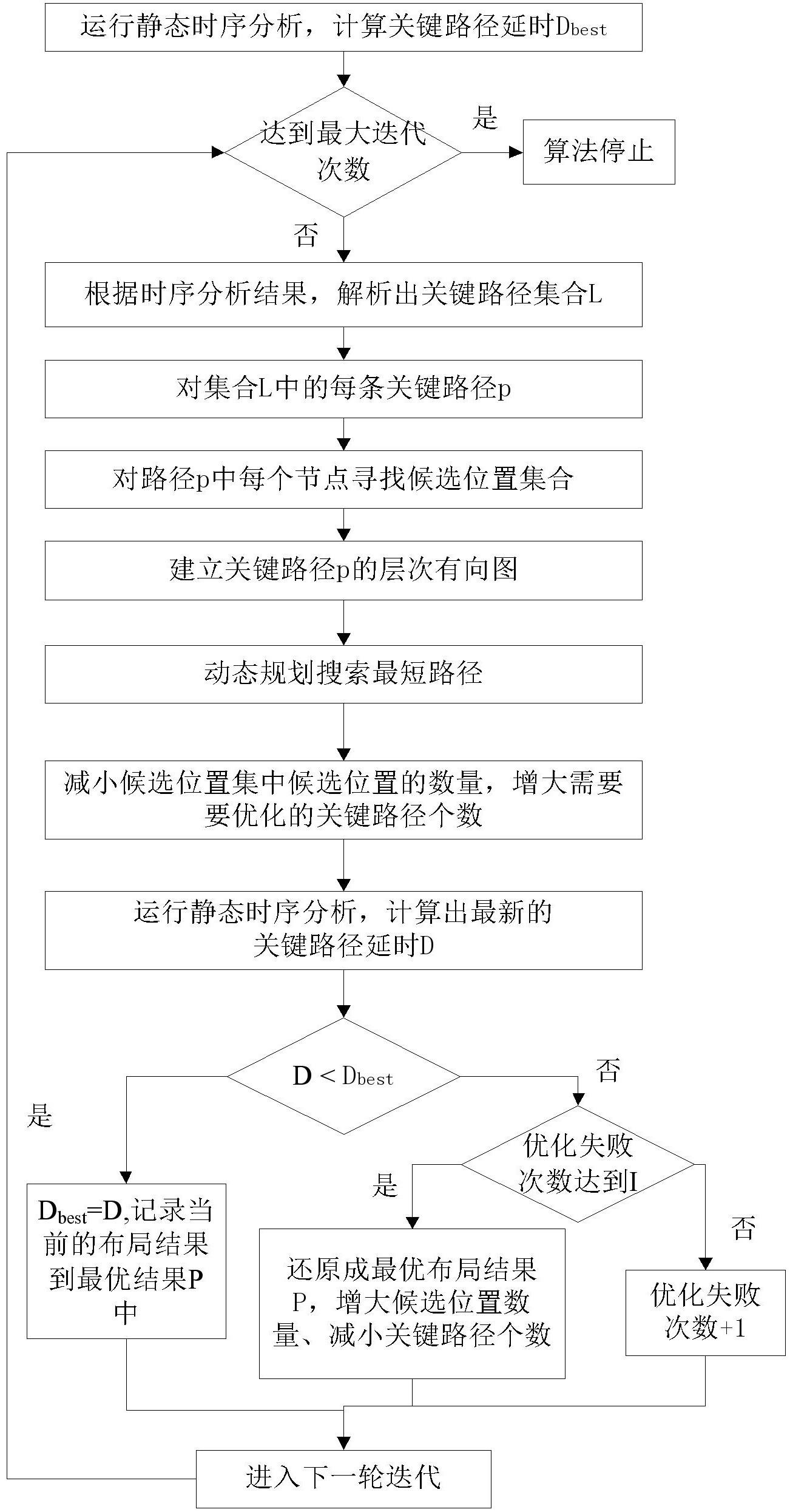

3、一种fpga详细布局方法,包括以下步骤:

4、步骤1:获取电路网表和全局布局的结果;

5、步骤2:对所述电路网表和全局布局的结果使用静态时序分析方法进行分析,计算拟详细布局电路的关键路径延时dbest;

6、步骤3:根据静态时序分析结果,解析出关键路径集合l,对关键路径集合l中每条关键路径p上的各节点寻找候选位置集;

7、步骤4:根据每条关键路径p上各节点的候选位置集,构建每条关键路径p的有向层次图;

8、步骤5:根据有向层次图,使用动态规划方法搜索出每条关键路径p的最短路径,并使用最短路径上的节点更新相应关键路径的布局位置;

9、步骤6:对对更新布局位置后的电路网表进行静态时序分析,计算出最新的关键路径延时d;

10、步骤7:减小候选位置集中的候选位置数量,增大关键路径的条数,如果最新的关键路径延时d小于dbest,将d赋予dbest,并记录当前的布局结果为最优布局结果,返回步骤3进行下一轮迭代直到达到最大迭代次数则停止布局优化,否则认为此轮迭代布局失败,判断布局失败的总次数是否超过预设次数,超过则将当前布局结果还原为最优布局结果,并增大候选位置集中的候选位置数量,减小关键路径条数后返回步骤3进行下一轮迭代直到达到最大迭代次数则停止布局优化,没超过则记录失败次数后返回步骤3进行下一轮迭代直到达到最大迭代次数则停止布局优化;

11、步骤8:输出最优布局结果。

12、进一步地,步骤3中为各节点寻找候选位置集的方法是:为关键路径中的每个节点划分出一片用于覆盖多个节点位置的候选区域,当候选区域内的某一坐标位置和当前节点资源类型相同时,将该坐标位置作为当前节点的候选位置,以此方法对候选区域内的每一个坐标位置进行判断,形成候选位置集。

13、进一步地,为关键路径中的每个节点划分出一片用于覆盖多个节点位置的候选区域是指,以每个节点为中心,以预设的长度为边长形成的正方形所覆盖的区域。

14、进一步地,步骤4中构建有向层次图的方法是:

15、以一条关键路径上的每个节点为一个层次,以每个节点的候选位置集中的候选位置为该节点所处层次上的节点,有向层次图中的方向是按照关键路径节点的顺序,从前往后的方向依次构建;上一层中的每个节点分别连接指向下一层中的每个节点,两个节点之间的边的权重是两个节点所在坐标位置之间的延时。

16、进一步地,步骤5中动态规划的方法是:

17、步骤5.1:在有向层次图的基础上,计算每一节点的输出延时,所述输出延时为一节点所在层次之前路径上的最短延时加上当前节点与下一层次连接的节点之间的输出边的延时,所述最短延时是指取当前层次上所有节点的输入延时的最小值,输入延时也就是上一节点到当前节点的输出延时;

18、步骤5.2:最短路径为从最后一个层次开始从后往前依次取当前层次上所有节点的输入延时最小值所在的节点所形成的路径。

19、进一步地,当不同节点覆盖的候选区域重叠时,确定覆盖范围内的坐标位置属于哪个节点的候选位置的方法是:

20、对于关键路径p的每个节点n,在为其划分的覆盖范围内判断每个坐标位置的资源类型,如果当前坐标位置r的资源类型与当前节点n的资源类型相同,将节点n加入到位置r的邻接列表中;

21、计算覆盖范围内的每个坐标位置r与邻近的关键路径节点n之间的距离,并将该距离信息记录到坐标位置r的邻接列表中;

22、将每个坐标位置r邻接列表中的关键路径节点,按照坐标位置r与关键路径节点之间的距离从小到大的顺序进行排序;

23、遍历每个坐标位置r其邻接列表中的每个关键路径节点,首先找到距离最近的第一个关键路径节点n1,将坐标位置r加入到节点n1的候选位置集合中,然后找到距离第二近的关键路径节点n2,如果n2与n1在当前关键路径上是相连的,则将坐标位置r也加入到节点n2的候选位置集合中;否则继续寻找坐标位置r的下一个邻近位置,直到坐标位置r的邻接列表遍历完或者坐标位置r已加入到2个节点的候选位置集合中为止。

24、进一步地,步骤3中根据静态时序分析的结果,解析出关键路径集合l的方法是:

25、步骤1)、静态时序分析结果包括电路网表中各条连接的时序裕度和关键度,首先将所有连接按照关键度从大到小的顺序进行排序,排序后的连接保存在连接集合s中;

26、步骤2)、从连接集合s中选择关键度最大的所有连接形成集合s’;

27、步骤3)、从集合s’中的第一条连接开始拼接关键路径p,遍历集合s’中的其他连接c’,如果连接c’的连向点是关键路径p的头结点,则将连接c’加入到关键路径p的头部,连接c’的起始点作为关键路径p新的头节点;如果连接c’的起始点是关键路径p的终节点,连接c’加入到关键路径p的尾部,连接c’的连向点作为关键路径p新的终节点,当关键路径的头节点是时序图的路径起点类型,并且终节点是时序图的路径终点类型时,则关键路径p拼接完成,将p加入都关键路径集合l中;

28、步骤4)、判断当前关键路径集合l中路径的个数是否达到预设的个数n,如果没有达到,返回到步骤2),继续解析下一条关键路径;如果达到n,解析完成。

29、本发明提供了一种fpga详细布局系统,使用了前面所述的一种fpga详细布局方法中的各步骤。

30、采用上述技术方案,本发明具有如下有益效果:

31、本发明提供的一种fpga详细布局方法及系统,通过划分一定区域所覆盖的坐标位置来为关键路径上的每个节点选择候选位置集合,进而根据关键路径的节点走向构建有向层次图,为动态规划搜索最短路径提供了可能。通过使用动态规划搜索最短路径的方法,解决了模拟退火详细布局运行时间长、容易陷入局部最优的问题,并提高了详细布局的质量。

- 还没有人留言评论。精彩留言会获得点赞!