集成电路芯片的时序分析方法、装置、设备及介质与流程

本技术涉及集成电路芯片技术,尤其涉及一种集成电路芯片的时序分析方法、装置、设备及介质。

背景技术:

1、在大规模集成电路物理设计中,为了提高设计效率多采用层次化设计方式,将设计切分成多个模块,对每个模块进行展平设计,完成独立的布局布线过程,对各个电路模块分别进行数据建模,并提供给顶层进行组装设计,最后进行全芯片时序分析,或者还可以进行物理设计规则检查等。

2、在层次化设计中,需要划分电路模块和顶层各自占用的物理空间,通常来说模块占用低层绕线资源进行器件之间的互连,顶层占用高层绕线资源进行特殊信号例如高速时钟线,电源网络的互连。模块之间的边界,模块和顶层的边界上存在相邻的金属连线,这些金属连线之间存在耦合电容,而在各模块独立进行数据建模时,由于缺乏其他模块和顶层的数据,这部分耦合电容无法被建模,其引起的串扰效应会被忽略,造成时序和噪声分析的误差。

3、现有技术方案有两个方向:一是进行展平的数据建模,即将模块的完整数据组装到顶层后进行全芯片的寄生参数提取,这种方法可以准确地进行数据建模和分析,但是这种做法只适用于中等规模芯片,对大规模芯片而言,时间和硬件资源的开销巨大,甚至超出电子设计自动化eda工具的处理极限,并且不利于解耦电路模块和顶层之间的设计依赖。

4、另一个解决思路是减少边界处的信号耦合,例如增加屏蔽线,增大连线之间的距离以减少耦合电容;但随着集成电路工艺尺寸减小,寄生参数的模型越来越复杂,难以从根本上杜绝耦合电容。此外,屏蔽线会占用大量绕线资源,造成其他互连线的拥塞。

技术实现思路

1、本技术提供一种集成电路芯片的时序分析方法、装置、设备及介质,用以解决相关技术中的集成电路芯片的时序分析方法,存在耦合电容,导致时序分析误差的问题,实现对集成电路芯片的层次化时序分析,以提高时序分析的效率和准确性的技术效果。

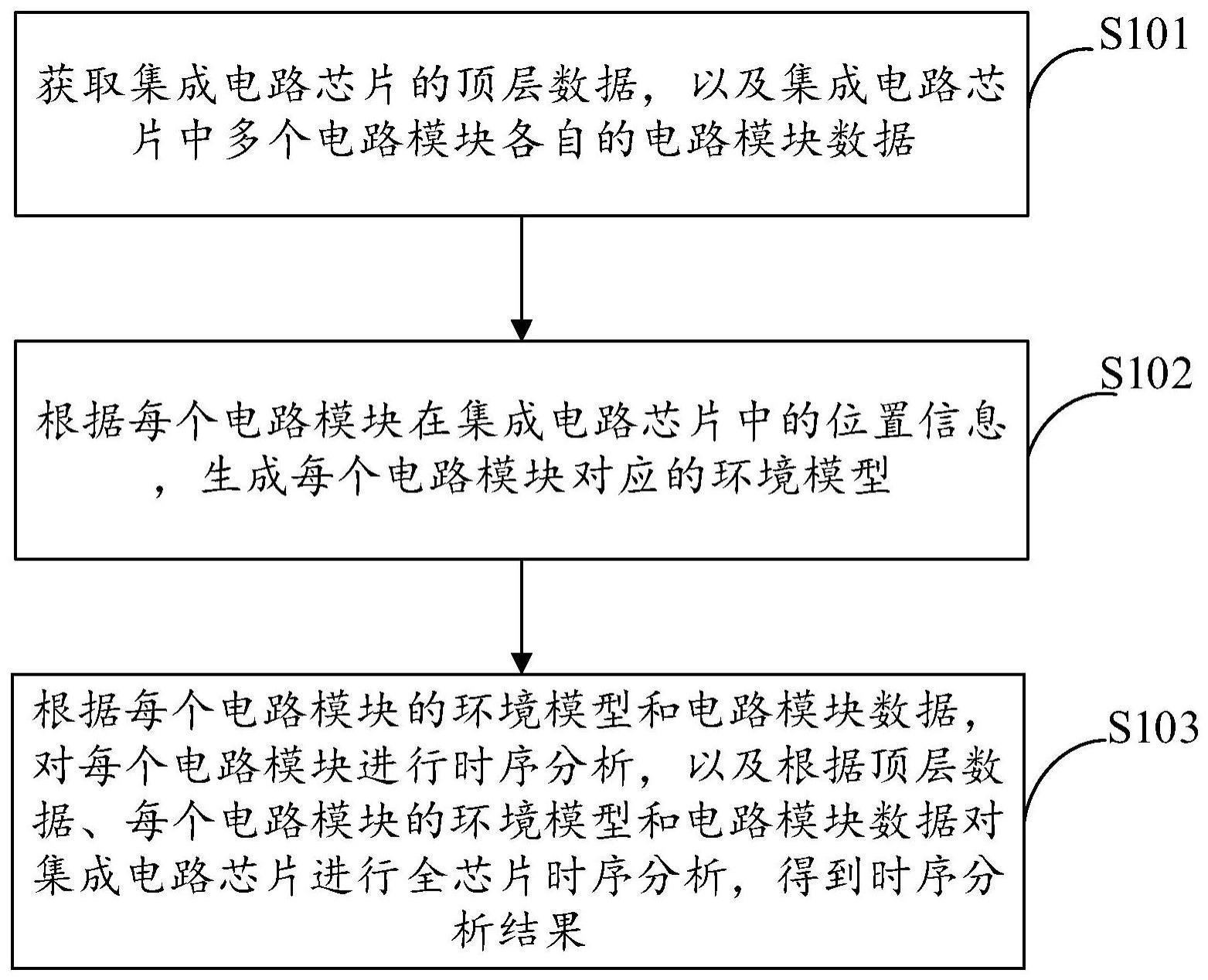

2、一方面,本技术提供一种集成电路芯片的时序分析方法,所述方法包括:

3、获取集成电路芯片的顶层数据,以及所述集成电路芯片中多个电路模块各自的电路模块数据;

4、根据每个所述电路模块在所述集成电路芯片中的位置信息,生成每个所述电路模块对应的环境模型;

5、根据每个所述电路模块的环境模型和电路模块数据,对每个所述电路模块进行时序分析,以及根据所述顶层数据、每个所述电路模块的环境模型和电路模块数据对所述集成电路芯片进行全芯片时序分析,得到时序分析结果。

6、一种可选的实施方式中,根据每个所述电路模块在所述集成电路芯片中的位置信息,生成每个所述电路模块对应的环境模型,包括:

7、根据每个所述电路模块在所述集成电路芯片中的位置信息,从所述顶层数据中抽取出与每个所述电路模块之间存在耦合电容的顶层互连线;

8、根据每个所述电路模块之间存在耦合电容的顶层互连线,生成每个所述电路模块对应的环境模型。

9、一种可选的实施方式中,根据每个所述电路模块的环境模型和电路模块数据,对每个所述电路模块进行时序分析,包括:

10、对每个所述电路模块的环境模型和电路模块数据进行寄生参数提取,得到每个所述电路模块对应的环境寄生参数文件和模块寄生参数文件;

11、根据每个所述电路模块对应的所述环境模型,所述模块寄生参数文件和所述环境寄生参数文件,对每个所述电路模块进行时序分析,得到每个所述电路模块对应的时序分析结果。

12、一种可选的实施方式中,根据所述顶层数据、每个所述电路模块的环境模型和电路模块数据对所述集成电路芯片进行全芯片时序分析,包括:

13、对所述顶层数据进行寄生参数提取得到顶层寄生参数文件;

14、组装所述顶层寄生参数文件、所述模块寄生参数文件和所述环境寄生参数文件,得到全芯片寄生参数文件;

15、基于所述全芯片寄生参数文件对所述集成电路芯片进行全芯片时序分析,得到所述集成电路芯片对应的时序分析结果。

16、一种可选的实施方式中,对每个所述电路模块的环境模型和电路模块数据进行寄生参数提取,得到每个所述电路模块对应的环境寄生参数文件和模块寄生参数文件,包括:

17、根据每个所述电路模块的环境模型和电路模块数据,联合进行寄生参数提取,得到每个所述电路模块对应的环境寄生参数文件和模块寄生参数文件;

18、其中,所述模块寄生参数文件包含:电路模块内部的寄生参数,所述环境寄生参数文件包含:所述环境模型内的互连线和所述电路模块内的互连线之间的耦合电容。

19、另一方面,本技术提供一种集成电路芯片的时序分析装置,上述装置包括:

20、获取模块,用于获取集成电路芯片的顶层数据,以及所述集成电路芯片中多个电路模块各自的电路模块数据;

21、生成模块,用于根据每个所述电路模块在所述集成电路芯片中的位置信息,生成每个所述电路模块对应的环境模型;

22、时序分析模块,用于根据每个所述电路模块的环境模型和电路模块数据,对每个所述电路模块进行时序分析,以及根据所述顶层数据、每个所述电路模块的环境模型和电路模块数据对所述集成电路芯片进行全芯片时序分析,得到时序分析结果。

23、一种可选的实施方式中,所述生成模块,包括:

24、抽取单元,用于根据每个所述电路模块在所述集成电路芯片中的位置信息,从所述顶层数据中抽取出与每个所述电路模块之间存在耦合电容的顶层互连线;

25、生成单元,用于根据每个所述电路模块之间存在耦合电容的顶层互连线,生成每个所述电路模块对应的环境模型。

26、一种可选的实施方式中,所述时序分析模块,包括:

27、第一提取单元,用于对每个所述电路模块的环境模型和电路模块数据进行寄生参数提取,得到每个所述电路模块对应的环境寄生参数文件和模块寄生参数文件;

28、第一时序分析单元,用于根据每个所述电路模块对应的所述环境模型,所述模块寄生参数文件和所述环境寄生参数文件,对每个所述电路模块进行时序分析,得到每个所述电路模块对应的时序分析结果。

29、一种可选的实施方式中,所述时序分析模块,还包括:

30、第二提取单元,用于对所述顶层数据进行寄生参数提取得到顶层寄生参数文件;

31、组装单元,用于组装所述顶层寄生参数文件、所述模块寄生参数文件和所述环境寄生参数文件,得到全芯片寄生参数文件;

32、第二时序分析单元,用于基于所述全芯片寄生参数文件对所述集成电路芯片进行全芯片时序分析,得到所述集成电路芯片对应的时序分析结果。

33、另一方面,本技术提供一种电子设备,包括:处理器,以及与上述处理器连接的存储器;上述存储器存储计算机执行指令;上述处理器执行上述存储器存储的计算机执行指令,以实现如任一项上述的方法。

34、另一方面,本技术提供一种计算机可读存储介质,上述计算机可读存储介质中存储有计算机执行指令,上述计算机执行指令被处理器执行时用于实现如任一项上述的方法。

35、另一方面,本技术提供一种计算机程序产品,包括计算机程序,该计算机程序被处理器执行时实现任一项上述的方法。

36、本技术提供的集成电路芯片的时序分析方法、装置、设备及介质,通过获取集成电路芯片的层次化设计数据,其中,层次化设计数据包括顶层数据,多个电路模块各自的电路模块数据;根据每个电路模块在集成电路芯片中的位置信息,生成每个电路模块对应的环境模型;根据每个电路模块的环境模型和电路模块数据,对每个电路模块进行时序分析,以及根据顶层数据、每个电路模块的环境模型和电路模块数据对集成电路芯片进行全芯片时序分析,得到时序分析结果。

37、采用本技术提供的集成电路芯片的时序分析方案,可以解决相关技术中的集成电路芯片的时序分析方法,存在耦合电容,导致时序分析误差的问题,实现对集成电路芯片的层次化时序分析,以提高时序分析的效率和准确性的技术效果。

- 还没有人留言评论。精彩留言会获得点赞!