一种RS485/RS422接口驱动器输出电路及其控制方法与流程

本发明属于集成电路设计领域,具体涉及一种rs485/rs422接口驱动器输出电路及其控制方法。

背景技术:

1、rs485协议是美国电子工业协会(electronic industry association,eia)制定的一种串行物理接口标准,其是在rs-422基础上制定的标准,rs-485接口标准采用平衡式发送,差分式接收的数据收发器来驱动总线,其具有远距离传输、多节点(32个)以及传输线成本低的特性。

2、但rs485接口输出共模电压达到-7v~+12v的宽范围,以降低在长线传输,因驱动器与接收器不共地带来的共模偏差;并且rs485驱动器输出短路至-7~12v时,短路电流应小于250ma,就对rs485驱动器设计带来巨大的挑战,已满足在高压与低压共模出现时对输出驱动管造成的影响,如pmos与nmos与输出端形成pn节的正向导通,产生大电流对后级电路以及负载端造成严重影响。

3、本方面设计了一种rs485/rs422接口驱动器输出电路与控制方法,从较低的输出共模电压(例如采集-7v的输出共模电压)到较高的电压(例如采集高达12v的输出共模电压),逻辑控制电路根据输入的判决阈值,输出不同的控制信号,在不同状态下对nmos驱动管与pmos驱动管进行控制,通过在不同的共模电压下不同的电压嵌位,将pn结正向导通通路阻断,从而实现了在宽共模环境下的数据输出,该电路与控制方法可以被广泛应用rs485/rs422电路中。

技术实现思路

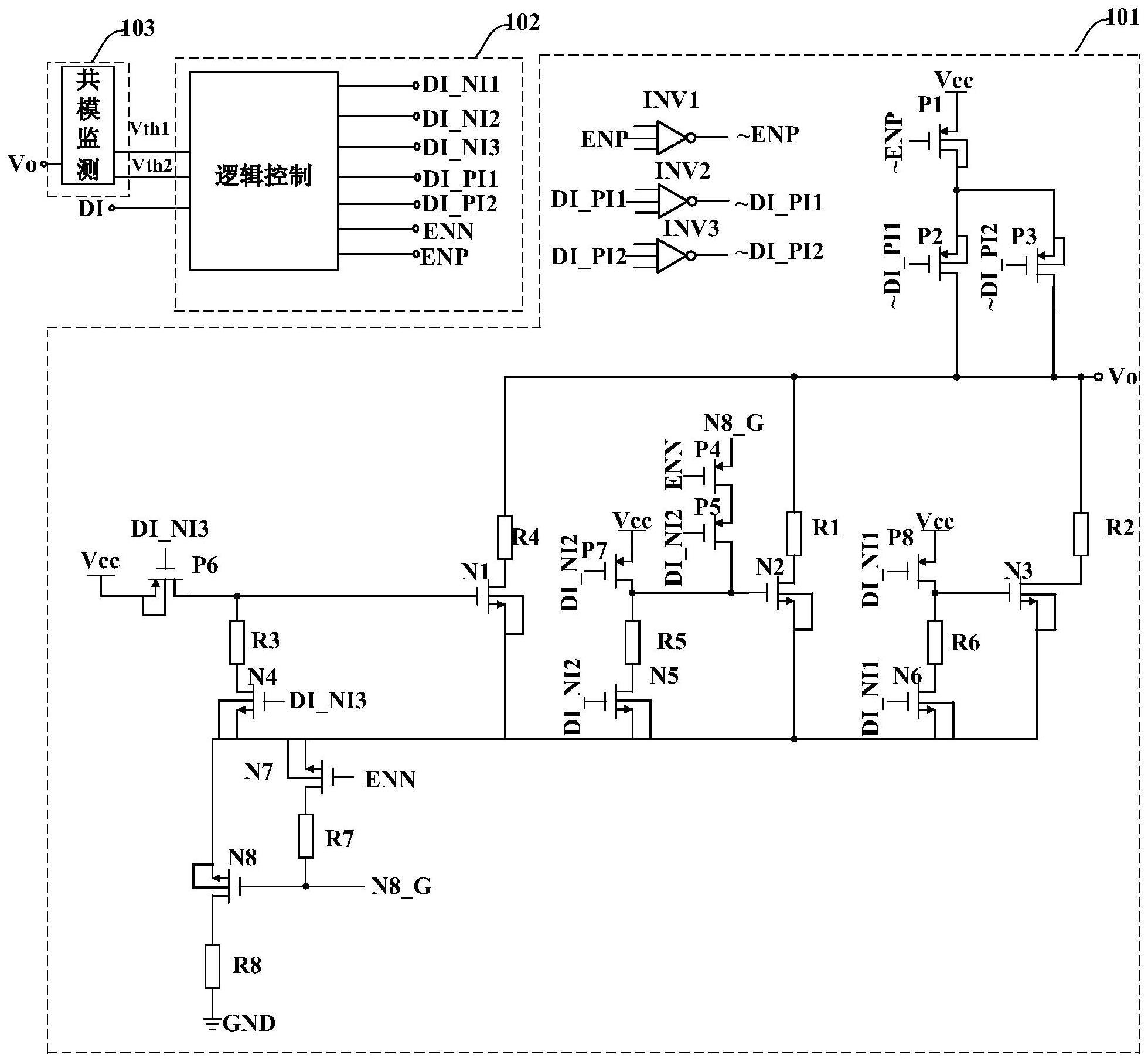

1、为了不同状态下的输出共模电平对nmos驱动管与pmos驱动管进行控制,实现不同的电压嵌位,防止高低压下驱动管pn节导通后产生大电流,实现数据的宽共模电压传输,本发明提出一种rs485/rs422接口驱动器输出电路,包括逻辑控制单元、共模检测单元和主体电路单元,其中:

2、逻辑控制单元包括第一pmos开关控制端、第二pmos开关控制端、第一nmos开关控制端、第二nmos开关控制端、第三nmos开关控制端、第一使能端、第二使能端;

3、共模监测单元根据电路的输出端输出两个阈值电压,逻辑控制单元根据阈值电压设置第一使能端和第二使能端的电压值;

4、主体电路单元包括第一~第八p型mos管、第一~第八n型mos管、第一~第三反相器、第一~第八电阻,第一反相器的输入端与逻辑控制单元的第一使能端连接,第二反相器的输入端与逻辑控制单元的第一pmos开关控制端连接,第三反相器的输入端与逻辑控制单元的第二pmos开关控制端连接;

5、第一p型mos管的源极与电源端相连,第一p型mos管的栅极与第一反相器输出端、第一使能端连接在一起,第一p型mos管的衬底与漏极相连,第一p型mos管的漏极与第二p型mos管、第三p型mos管的源极相连;

6、第二p型mos管的栅极与第二反相器的输出端相连,第二p型mos管的衬底与源极相连第二p型mos管的漏极与输出端相连;

7、第三p型mos管的栅极与第三反相器的输出端相连,第三p型mos管的衬底与源极相连,第三p型mos管的漏极与输出端相连;

8、第六p型mos管的栅极与逻辑控制单元的第三nmos开关控制端相连,第六p型mos管的衬底和源极与电源端相连,第六p型mos管的漏极与第三电阻的plus端、第一n型mos管的栅极相连;

9、第四n型mos管的栅极与逻辑控制单元的第三nmos开关控制端相连,第四n型mos管的的漏极与第三电阻的minus端相连,第四n型mos管的的源极、衬底与第一n型mos管、第二n型mos管、第三n型mos管、第五n型mos管、第六n型mos管、第七n型mos管、第八n型mos管的源极相连;

10、第八n型mos管的栅极与第七电阻的minus端相连,第八n型mos管的衬底与源极相连,第八n型mos管的漏极与第八电阻的plus端相连;

11、第八电阻的minus端接地;

12、第七n型mos管的栅极与逻辑控制单元的第二使能端相连,第七n型mos管的衬底与源极相连,第七n型mos管的漏极与第七电阻的plus端相连;

13、第一n型mos管的衬底与源极相连,第一n型mos管的漏极与第四电阻的minus端相连;

14、第四电阻的plus端与输出端相连;

15、第七p型mos管的栅极与逻辑控制单元的第二pmos开关控制端(di_pi2)相连,第七p型mos管的源极与电源端相连,第七p型mos管的漏极与第五电阻的plus端相连;

16、第五n型mos管的栅极与逻辑控制单元的第二pmos开关控制端(di_pi2)相连,第五n型mos管的漏极与第五电阻的minus端相连,第五n型mos管的衬底与源极相连;

17、第四p型mos管的栅极与逻辑控制单元的第二使能端相连,第四p型mos管的源极与第八n型mos管的栅极相连,第四p型mos管的漏极与第五p型mos管的源极相连;

18、第五p型mos管的栅极与逻辑控制单元的第二pmos开关控制端(di_pi2)相连,第五p型mos管的漏极与第二n型mos管的栅极相连;

19、第二n型mos管的漏极与第一电阻的minus端相连,第二n型mos管的衬底与源极相连;

20、第一电阻的plus端与输出端相连;

21、第八p型mos管的栅极与逻辑控制单元的第一pmos开关控制端(di_pi1)相连,第八p型mos管的源极与电源端相连,第八p型mos管的漏极与第六电阻的plus端相连;

22、第六n型mos管的栅极与逻辑控制单元的第一pmos开关控制端(di_pi1)相连,第六n型mos管的漏极与第六电阻的minus端相连,第六n型mos管的衬底与源极相连;

23、第三n型mos管的栅极与第八p型mos管的漏极相连,第三n型mos管的衬底与源极相连,第三n型mos管的漏极与第二电阻的minus端相连;

24、第二电阻的plus端与输出端相连。

25、本发明还提出一种rs485/rs422接口驱动器输出电路的控制方法,利用一种rs485/rs422接口驱动器输出电路进行控制,具体包括以下步骤:

26、当一种rs485/rs422接口驱动器输出电路的输出端工作在设置的低电压共模范围内时,共模监测单元输出的第一阈值电压为高电压、第二阈值单元为高电压,逻辑控制单元输出的第一使能电压为高电压、第二使能电压为高电压;

27、当一种rs485/rs422接口驱动器输出电路的输出端工作在设置的正常共模范围内时,共模监测单元输出的第一阈值电压为低电压、第二阈值单元为高电压,逻辑控制单元输出的第一使能电压为低电压、第二使能电压为高电压;

28、当一种rs485/rs422接口驱动器输出电路的输出端工作在设置的高电压共模范围内时,共模监测单元输出的第一阈值电压为低电压、第二阈值单元为低电压,逻辑控制单元输出的第一使能电压为低电压、第二使能电压为低电压。

29、本发明可以通过监测输出共模电压的值调节逻辑控制来调节输出驱动管的导通与嵌位,防止电压过高或者过低后将输出驱动管的pn结正向导通,对电路造成严重影响。

- 还没有人留言评论。精彩留言会获得点赞!