一种神经网络电路结构、存算模块、组件、系统及运行方法与流程

本发明涉及电子电路,尤其涉及一种神经网络电路及系统。

背景技术:

1、人工智能芯片算力的提升是实现人工智能的“基础保障”。能否开发出具有超高运算能力、符合市场需求的芯片,已成为人工智能领域可持续发展的重要因素。而决定人工智能芯片质量的主要因素,是神经网络算法和硬件性能。新型非易失存储器由于其实时响应、关键成本和能耗方面的特性被普遍运用于智能设备和物联网边缘设备。特别是具有高容量、高速度和小待机功耗的新型非易失性存储器,是未来人工智能硬件设备性能提升的关键。

2、处理深度学习中的神经网络算法,处理器将使用大量的乘加累积运算,用于卷积神经网络或全连通神经网络,因此在此过程中会产生大量的中间数据。采用传统的冯·诺依曼结构,数据必须通过总线移动到存储器中。为了克服传统冯·诺依曼结构带来的计算限制,存内计算(cim)的概念被提出,不必像传统的冯·诺伊曼结构通过内存总线访问外部存储器。这不仅减少了中间数据的传输,还减轻了处理器的运算量。存内计算的另一个显著的优势是能够实现多行读取,从而减少了存储访问的次数,增加了数据吞吐量。但sram的存算单元面积较大,且是掉电易失性的,大量的存算单元将很大程度地增加功耗,因此在掉电后仍能进行数据保存的高密度非易失性存储器是未来发展的必然趋势。

3、近年来对深度学习的研究表明,二值化神经网络在精度损失较小的情况下,能够显著降低计算和存储开销,且在硬件电路中得到了很好的实现,极大加速了神经网络的推断过程。但二值化会不可避免地导致信息损失,其量化函数不连续性也给深度网络的优化带来了困难,同时如何选择合适的电元件和电路结构达到不同的效果也亟需研究解决。

技术实现思路

1、鉴于上述现有存在的问题,提出了本发明。

2、因此,本发明提供了一种神经网络电路解决目前相关电路二值化会不可避免地导致信息损失,其量化函数不连续性也给深度网络的优化带来了困难,以及目前采用的一些方法如磁性隧道节计算结果不够精确,生产成本高的问题。

3、为解决上述技术问题,本发明提供如下技术方案:

4、第一方面,本发明提供了一种神经网络电路结构,包括:

5、储电放电元件,所述储电放电元件设置至少一个;

6、开关元件,所述开关元件设置有一对,一对开关元件的其中一极分别连接于所述储电放电元件上,其中源极分别连接至位线。

7、作为本发明所述的神经网络电路结构的一种优选方案,其中:所述储电放电元件为自发极化电容。

8、作为本发明所述的神经网络电路结构的一种优选方案,其中:一对开关元件分别为第一开关元件和第二开关元件;

9、所述第一开关元件的源极连接至第一位线;所述第二开关元件的源极连接至第二位线;所述第一位线与第二位线为相邻的位线。

10、作为本发明所述的神经网络电路结构的一种优选方案,其中:一对开关元件分别为第一开关元件和第二开关元件;

11、所述的第一开关元件和第二开关元件的源极均连接至同一条位线上。

12、作为本发明所述的神经网络电路结构的一种优选方案,其中:所述储电放电元件与所述开关元件串联;

13、作为本发明所述的神经网络电路结构的一种优选方案,其中:若储电放电元件存在多个,则储电放电元件彼此之间并联,且储电放电元件的其中一极均连接第一板线。

14、作为本发明所述的神经网络电路结构的一种优选方案,其中:若储电放电元件存在多个,则储电放电元件彼此之间串联,且其中一个储电放电元件的其中一极连接第一板线。

15、第二方面,本发明提供了一种神经网络电路存算模块,包括:

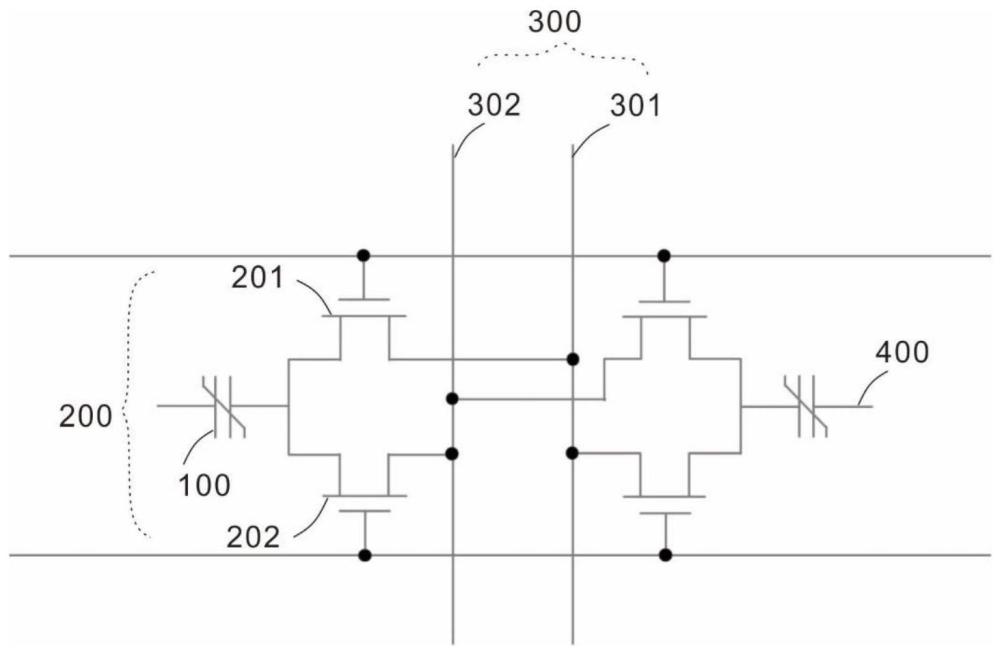

16、所述神经网络电路结构,一对所述神经网络电路结构分别为第一神经网络电路结构和第二神经网络电路结构。

17、作为本发明所述的神经网络电路存算模块的一种优选方案,其中:

18、所述第一神经网络电路结构的第一开关元件的源极连接至第一位线,所述第二开关元件的源极连接至第二位线;

19、所述第二神经网络电路结构的第一开关元件的源极连接至第二位线,所述第二开关元件的源极连接至第一位线;

20、所述第一位线与第二位线为相邻的位线。

21、作为本发明所述的神经网络电路存算模块的一种优选方案,其中:

22、所述第一神经网络电路结构的第一开关元件和第二开关元件的源极均连接至第二位线上;

23、所述第二神经网络电路结构的第一开关元件和第二开关元件的源极均连接至第一位线上;

24、所述第一位线与第二位线为相邻的位线。

25、第三方面,本发明提供了另一种神经网络电路组件,包括:所述神经网络电路存算模块,还包括,行地址译码器、字线驱动器、板线驱动器、列地址译码器和位线驱动器;

26、所述行地址译码器的输出端连接字线驱动器输入端;

27、所述列地址译码器的输出端连接位线驱动器输入端;

28、所述字线驱动器通过字线与由多个存算模块构成的神经网络区块连接;

29、所述位线驱动器通过位线与由多个存算模块构成的神经网络区块连接;

30、所述板线驱动器通过板线与由多个存算模块构成的神经网络区块连接。

31、作为本发明所述的神经网络电路组件的一种优选方案,其中:还包括感应放大器组;

32、所述感应放大器组通过位线与存算模块阵列连接;

33、所述感应放大器组包括多个感应放大器;

34、每个感应放大器对应至少一列存算模块。

35、第四方面,本发明提供了一种神经网络电路系统,包括所述的神经网络电路组件,其特征在于,还包括,

36、计算阵列输入编码器,用于接收二值化神经网络输入数据,并对输入数据进行编码以匹配行地址译码器的输入要求;

37、寄存器,用于保存卷积计算的二值化结果。

38、累加器,用于在全连接运算时,能够将单步运算结果进行累加。

39、第五方面,本发明提供了一种神经网络电路运行方法,方法应用于在神经网络电路系统;

40、所述方法包括,

41、在进行二值化卷积运算时,若多组按位对齐共用位线的存算模块同时被选通,所述多组经过编码的字线输入为卷积输入,存算模块为卷积核,每一组存算模块的运算结果反应于两条位线的电压差异。

42、作为本发明所述的神经网络电路运行方法的一种优选方案,其中:在进行全连接运算时,行地址译码器通过字线驱动器逐行激活字线,逐行选通权重存算模块,对比位线上电压大小读取出运算结果,单步运算结果进行加和。

43、作为本发明所述的神经网络电路运行方法的一种优选方案,其中:所述自发极化电容进行写操作时,先在两条相邻字线中选择一条字线将电压升高,根据字线的不同电压,存算模块中不同的开关元件导通,列地址译码器通过位线驱动器根据所需要写入的权重给相邻两条加相应电压,再将板线电压升高后降低。

44、作为本发明所述的神经网络电路运行方法的一种优选方案,其中:所述自发极化电容进行读操作时,先将板线电压升高,再将输入数据加至字线上,根据字线的不同输入,存算模块中不同的开关元件导通,高电平板线通过自发极化电容和开关元件放电到位线,依据自发极化电容不同放电量,得到两条位线上大小不同的输出电压。

45、与现有技术相比,本发明的有益效果:本发明提供的神经网络电路结构,包括,储电放电元件,储电放电元件设置至少一个;开关元件,开关元件设置有一对,一对开关元件的其中一极分别连接于所述储电放电元件上,其中源极分别连接至位线。两组电路结构可构成存算模块,多组按位对齐的存算模块同时工作可以一步完成存内二值化神经网络卷积操作,感应放大器输出端接累加器,串行逐行工作可以完成二值神经网络全连接运算。由于自发极化电容具有非易失、超低待机功耗的特性,存内计算可克服“内存墙”数据传输延迟高,功耗大的困难,与传统存内二值化神经网络计算方式相比,该电路将有效提升二值化神经网络的计算速度和能效,减小芯片面积,自发极化电容极化强度越高计算结果精确。

- 还没有人留言评论。精彩留言会获得点赞!