基于数据流的计算电路、方法、人工智能芯片和电子设备与流程

本公开涉及人工智能,尤其涉及一种基于数据流的计算电路、方法、人工智能芯片和电子设备。

背景技术:

1、目前,各种人工智能算法已经被大量应用于各个领域。例如,神经网络算法已被广泛应用在诸如图像识别、图像分类等的机器视觉领域。

2、针对人工智能算法计算量大、计算复杂、计算时间长等问题,可以利用人工智能芯片(即ai芯片)来加速人工智能算法的运行。

3、相关技术中,存在两种主流的人工智能芯片,一种是基于指令集的人工智能芯片,另一种是基于数据流的人工智能芯片。

4、由于基于指令集的人工智能芯片的架构相对成熟、且生态比较完善,故,目前大多数的人工智能芯片基于指令集架构。

5、数据流架构是近年来基于领域专用架构(domain special architecture,dsa)理论建立的创新型架构,它结合人工智能算法的任务特点进行针对性的优化,按照数据流的方式对输入数据进行流水式的处理,从而在性能和计算效率方面均有大幅提升。

技术实现思路

1、发明人注意到,基于数据流的人工智能芯片在某些场景下的计算效率仍然较低。

2、通过分析发现,这种人工智能芯片中的多个计算单元可以具有不同的计算并行度。在某些场景下,计算并行度较低的计算单元先执行计算,而计算并行度较高的计算单元后执行计算。这种情况下,输入至计算并行度较高的计算单元的待计算数据的数据量小于计算单元的计算并行度,从而导致计算单元中的部分运算器空闲,进而导致计算效率降低。

3、为了解决上述问题,本公开实施例提供了如下技术方案。

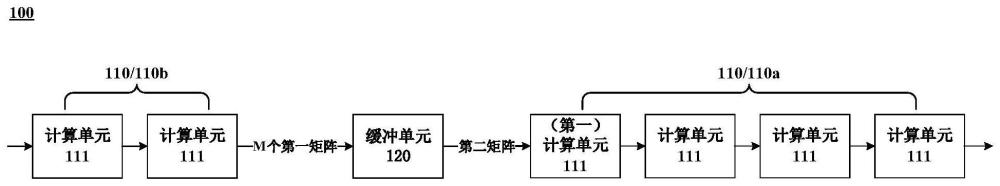

4、根据本公开实施例的一方面,提供一种基于数据流的计算电路,包括:多组计算单元,每组计算单元包括一个或多个计算单元,所述多组计算单元包括第一组计算单元和第二组计算单元,所述第二组计算单元被配置为在每次计算后输出第一矩阵;以及缓冲单元,被配置为执行一次或多次第一操作,所述第一操作包括:缓存所述第二组计算单元连续m次输出的m个第一矩阵,m为大于等于2的整数,将所述m个第一矩阵拼接成第二矩阵,所述第二矩阵中元素的数量不大于所述第一组计算单元中第一计算单元的计算并行度,和将所述第二矩阵连续n次输出至所述第一计算单元执行n次计算,n为大于等于2的整数。

5、在一些实施例中,所述第二矩阵中元素的数量等于所述计算并行度。

6、在一些实施例中,n为不小于m的整数。

7、在一些实施例中,n等于m。

8、在一些实施例中,所述缓冲单元还被配置为执行第二操作,所述第二操作包括:将接收到的第三矩阵直接输出至所述第一计算单元执行计算,其中,所述第三矩阵中元素的数量等于所述计算并行度。

9、在一些实施例中,所述缓冲单元包括:第一缓冲器,被配置为执行所述第一操作;和第二缓冲器,被配置为在所述第一缓冲器每次将所述第二矩阵输出至所述第一计算单元执行一次计算时,将所述一次计算所需的第四矩阵输出至所述第一计算单元。

10、在一些实施例中,所述计算电路还包括:第一选择单元,包括第一输入端、第二输入端、第一输出端和第二输出端,其中:所述第一输入端被配置为与所述第一输出端和所述第二输出端中的任意一个连接,所述第二输入端被配置为与所述第一输出端连接,所述第一输出端被配置为与所述缓冲单元的输入端连接;第二选择单元,包括第三输入端、第四输入端、第三输出端和第四输出端,其中:所述第三输入端被配置为与所述第一组计算单元的输出端连接,并且还被配置为与所述第三输出端和所述第四输出端中的任意一个连接,所述第四输入端被配置为与所述第二输出端连接,并且还被配置为与所述第三输出端连接,所述第三输出端被配置为与所述第二组计算单元的输入端连接;和第三选择单元,包括第五输入端、第五输出端和第六输出端,其中:第五输入端,被配置为与所述第二组计算单元的输出端连接,并且还被配置为与所述第五输出端和所述第六输出端中的任意一个连接,所述第五输出端被配置为与所述第二输入端连接。

11、在一些实施例中,所述第一选择单元包括:第一分发器,包括所述第一输入端、所述第二输出端和第一中间输出端,所述第一输入端被配置为与所述第二输出端和所述第一中间输出端中的任意一个连接,和第一选择器,包括第一中间输入端、所述第二输入端和所述第一输出端,所述第一中间输入端被配置为与所述第一中间输出端连接,所述第一输出端被配置为与所述第一中间输入端和所述第二输入端中的任意一个连接;所述第二选择单元包括:第二分发器,包括所述第三输入端、第二中间输出端和所述第四输出端,所述第三输入端被配置为与所述第二中间输出端和所述第四输出端中的任意一个连接,和第二选择器,包括所述第四输入端、第二中间输入端和所述第三输出端,所述第二中间输入端被配置为与所述第二中间输出端连接,所述第三输出端被配置为与所述第四输入端和所述第二中间输入端中的任意一个连接;所述第三选择单元包括第三分发器,所述第三分发器包括所述第五输入端、所述第五输出端和所述第六输出端。

12、在一些实施例中,所述第一组计算单元和所述第二组计算单元包括被配置为执行相同类型的人工智能计算的计算单元,并且还包括被配置为执行不同类型的人工智能计算的计算单元。

13、在一些实施例中,所述相同类型的人工智能计算包括线性计算。

14、在一些实施例中,所述第一组计算单元包括:所述第一计算单元,被配置为执行核函数计算;第二计算单元,被配置为执行激活函数计算;第三计算单元,被配置为执行线性计算;和第四计算单元,被配置为执行池化计算。

15、在一些实施例中,所述第二组计算单元包括:第五计算单元,被配置为执行线性计算;和第六计算单元,被配置为执行规约函数计算。

16、在一些实施例中,所述第二矩阵的列数是所述第一矩阵的列数的k倍,k为大于等于2的整数,所述第二矩阵中任意一行元素是所述第一矩阵的k行元素。

17、根据本公开实施例的另一方面,提供一种基于数据流的计算方法,包括:缓存基于数据流的计算电路中第二组计算单元连续m次输出的m个第一矩阵,m为大于等于2的整数;将所述m个第一矩阵拼接成第二矩阵,所述第二矩阵中元素的数量不大于所述计算电路的第一组计算单元中第一计算单元的计算并行度;以及将所述第二矩阵连续n次输出至所述第一计算单元执行n次计算,n为大于等于2的整数;其中,所述第一组计算单元和所述第二组计算单元均包括一个或多个计算单元。

18、在一些实施例中,所述第二矩阵中元素的数量等于所述计算并行度。

19、在一些实施例中,n为不小于m的整数。

20、在一些实施例中,n等于m。

21、根据本公开实施例的又一方面,提供一种人工智能芯片,包括:上述任意一个实施例所述的基于数据流的计算电路。

22、根据本公开实施例的还一方面,提供一种电子设备,包括:上述任意一个实施例所述的人工智能芯片。

23、本公开实施例提供的基于数据流的计算电路中,将计算并行度较小的第二组计算单元连续m次输出的m个第一矩阵拼接成元素数量小于或等于一计算单元所具有的计算并行度的第二矩阵。然后,将拼接得到的第二矩阵连续n次输出至第一计算单元执行n次计算。一方面,将由m个第一矩阵拼接得到的第二矩阵输出至第一计算单元执行计算,而不是直接将第二组计算单元每次输出的一个第一矩阵输出至第一计算单元执行计算,这可以提高第一计算单元中运算器的利用率。另一方面,将第二矩阵连续n次输出至第一计算单元执行n次计算,而不是仅将第二矩阵输出至第一计算单元执行一次计算,这可以在将第二矩阵连续n次输出至第一计算单元期间继续接收下一次第一操作中的m个第一矩阵中的至少部分第一矩阵,以便在将前一次第一操作中的第二矩阵连续n次输出至第一计算单元后,可以更快开始将下一次第一操作中的第二矩阵输出至第一计算单元执行计算。如此,可以提高计算效率。

24、通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征、方面及其优点将会变得清楚。

- 还没有人留言评论。精彩留言会获得点赞!