一种延长DDS芯片扫描时长的控制方法和控制电路与流程

本发明涉及信号处理应用,特别是涉及一种延长dds芯片扫描时长的控制方法和控制电路。

背景技术:

1、直接数值合成(direct digital synthesis,简写为dds)的信号处理技术,通过一个数字模拟转换器(digital to analog convertor,简写为dac)将数字信号转换为模拟信号,能够准确快速输出各种频率、幅度和相位的波形,在很多领域都得到了广泛的应用。例如,幅频特性测试中,只需要按照设定好的规律配置dds芯片(又称,直接数字频率合成器)的输出,就能够得到一个频率、幅度或相位随时间按照该规律在一定频率范围内的扫描信号,如此,即可通过扫描信号对被测器件进行快速、定性或定量的动态测试。

2、在实际应用中,对被测器件进行扫描时,需要在特定的目标扫描范围内进行扫描,且测试时需要将扫描结果传输给后续测试操作的功能模块,该目标扫描范围需要不大于由dds芯片内置dac的精度决定的芯片扫描范围。如果需要输出的扫描信号的频率较高,则总扫描时长较短。总扫描时长过短时,总扫描时长极有可能小于扫描结果传输所需的最小传输时间,导致需要获取扫描结果的功能模块来不及响应,无法获取扫描结果,以致于无法进行后续测试操作。

3、鉴于此,克服该现有技术所存在的缺陷是本技术领域亟待解决的问题。

技术实现思路

1、本发明要解决的技术问题是提供一种延长dds芯片扫描时长的控制方法和控制电路,解决dds芯片输出的扫描信号频率较高时,总扫描时长过短,导致需要获取扫描结果的功能模块来不及响应,无法进行后续测试操作的问题。

2、本发明采用如下技术方案:

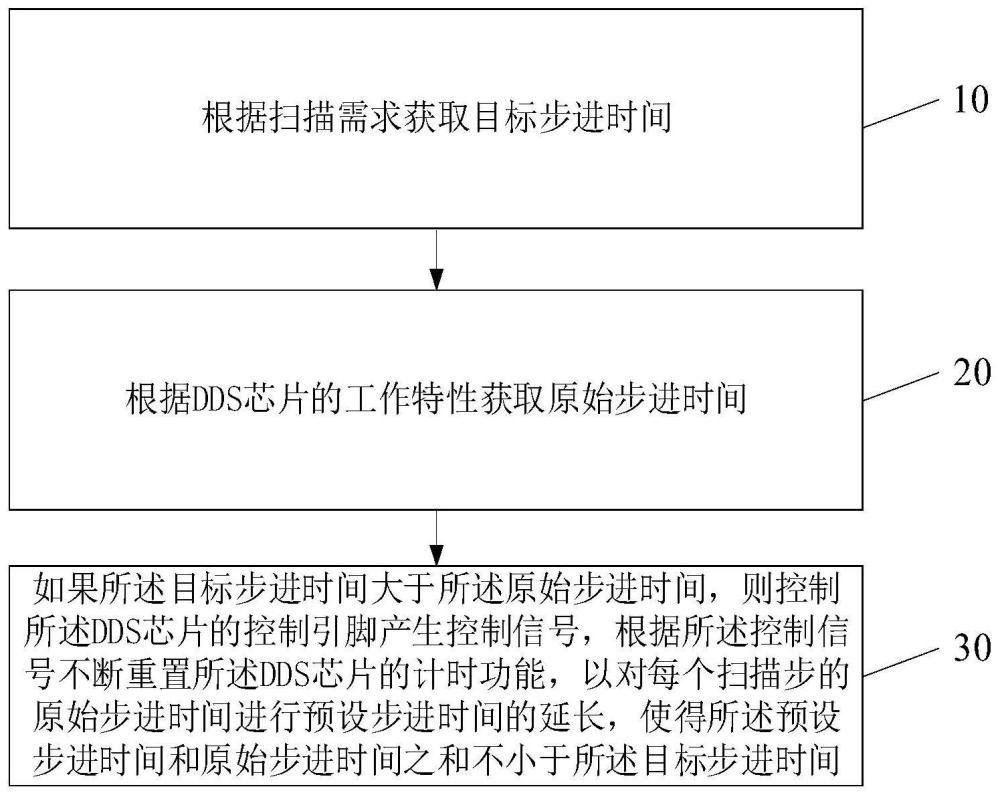

3、第一方面,本发明提供了一种延长dds芯片扫描时长的控制方法,包括:

4、根据扫描需求获取目标步进时间;

5、根据dds芯片的工作特性获取原始步进时间;

6、如果所述目标步进时间大于所述原始步进时间,则控制所述dds芯片的控制引脚产生控制信号,根据所述控制信号不断重置所述dds芯片的计时功能,以对每个扫描步的原始步进时间进行预设步进时间的延长,在经过一次或多次预设步进时间的延长后,使得所述预设步进时间、原始步进时间之和与所述目标步进时间相差小于等于预设时间。

7、进一步地,所述控制所述dds芯片的控制引脚产生控制信号,根据所述控制信号不断重置所述dds芯片的计时功能,以对每个扫描步的原始步进时间进行预设步进时间的延长,使得所述预设步进时间和原始步进时间之和不小于所述目标步进时间包括:

8、获取所述目标步进时间和所述原始步进时间之间的第一差值,基于所述第一差值设置所述预设步进时间;

9、在每个扫描步开始时,按照所述预设步进时间控制所述dds芯片的控制引脚产生pwm形式的控制信号,以不断重置所述dds芯片的计时功能;

10、在每个所述扫描步经历所述预设步进时间后,停止所述控制信号的输出,控制所述控制引脚的输出电平维持在稳定的预设稳定电平,以使所述dds芯片完成原始步进时间的扫描。

11、进一步地,所述在每个扫描步开始时,按照所述预设步进时间控制所述dds芯片的控制引脚产生pwm形式的控制信号,以不断重置所述dds芯片的计时功能包括:

12、获取pwm形式的控制信号的周期时间;

13、将所述预设步进时间除以所述周期时间,得到脉冲个数;

14、控制所述dds芯片的控制引脚输出m个pwm方波,其中,m等于所述脉冲个数。

15、进一步地,所述在每个扫描步开始时,按照所述预设步进时间控制所述dds芯片的控制引脚产生pwm形式的控制信号,以不断重置所述dds芯片的计时功能还包括:

16、在所述扫描步开始时,每次通过控制所述控制引脚的输出电平,产生在预设高电平与预设低电平之间的一次电平变化;

17、所述电平变化每次触发所述计时功能从零开始,进行一个周期时间的计时;

18、直至所述输出电平产生第m次电平变化,以产生所述pwm形式的控制信号。

19、进一步地,所述在每个所述扫描步经历所述预设步进时间后,停止所述控制信号的输出,控制所述控制引脚的输出电平维持在稳定的预设稳定电平,以使所述dds芯片完成原始步进时间的扫描包括:

20、在所述扫描步中,当进行计时的多个周期时间之和达到所述预设步进时间时,所述输出电平产生第m次电平变化,所述第m次电平变化触发所述计时功能从零开始,进行所述原始步进时间的计时;

21、控制所述输出电平维持在稳定的所述预设稳定电平,以停止所述控制信号的输出;

22、当达到所述原始步进时间时,所述计时功能停止计时,所述dds芯片跳转至下一个扫描步。

23、进一步地,所述根据扫描需求获取目标步进时间包括:

24、根据扫描需求获取目标总扫描时长和目标扫描范围,根据所述目标总扫描时长和所述目标扫描范围得到所述目标步进时间。

25、进一步地,所述根据dds芯片的工作特性获取原始步进时间包括:

26、根据所述dds芯片的目标输出频率,得到所述dds芯片的系统时钟值;

27、根据所述dds芯片的内部时钟比值和所述系统时钟值,得到所述dds芯片的内部时钟值;

28、将所述dds芯片的配置值与所述内部时钟值之比确定为原始步进时间。

29、进一步地,所述控制方法还包括:

30、如果所述目标步进时间小于等于所述原始步进时间,则按照所述dds芯片的原始步进时间进行扫描。

31、第二方面,本发明还提供了一种控制电路,所述控制电路为基于dds芯片的控制电路,所述控制电路用于实现如第一方面所述的延长dds芯片扫描时长的控制方法,包括获取模块和控制模块,其中:

32、所述获取模块,用于根据扫描需求获取目标步进时间;

33、所述控制模块,用于根据dds芯片的工作特性获取原始步进时间,判断所述目标步进时间是否大于所述原始步进时间;当所述目标步进时间大于所述原始步进时间时,还用于控制所述dds芯片的控制引脚产生控制信号,根据所述控制信号不断重置所述dds芯片的计时功能,以对每个扫描步的原始步进时间进行预设步进时间的延长,在经过一次或多次预设步进时间的延长后,使得所述预设步进时间、原始步进时间之和与所述目标步进时间相差小于等于预设时间;当所述目标步进时间小于等于所述原始步进时间时,控制所述dds芯片的控制引脚产生控制信号,以按照所述原始步进时间进行扫描。

34、进一步地,所述控制电路还包括信号输出模块,用于输出扫描信号,以便于所述扫描信号按照所述dds芯片的原始步进时间或目标步进时间进行扫描。

35、第三方面,本发明还提供了一种控制电路,用于实现第一方面所述的延长dds芯片扫描时长的控制方法,所述控制电路包括:

36、至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述处理器执行,用于执行第一方面所述的延长dds芯片扫描时长的控制方法。

37、第四方面,本发明还提供了一种非易失性计算机存储介质,所述计算机存储介质存储有计算机可执行指令,该计算机可执行指令被一个或多个处理器执行,用于完成第一方面所述的延长dds芯片扫描时长的控制方法。

38、区别于现有技术,本发明至少具有以下有益效果:

39、本发明根据扫描需求获取目标步进时间,根据dds芯片的工作特性获取原始步进时间,通过在目标步进时间大于原始步进时间时,控制所述dds芯片的控制引脚产生控制信号,根据所述控制信号不断重置所述dds芯片的计时功能,以对每个扫描步的原始步进时间进行预设步进时间的延长,使得所述预设步进时间和原始步进时间之和不小于所述目标步进时间,实现了延长dds芯片的总扫描时长,极大的扩展了dds芯片扫描输出的时间范围,解决了扫描时dds芯片输出的扫描信号频率较高时,总扫描时长过短,导致需要获取扫描结果的功能模块来不及响应,无法进行后续测试操作的问题。

- 还没有人留言评论。精彩留言会获得点赞!