一种存储器系统的训练方法及系统与流程

本技术涉及存储器,特别涉及一种存储器系统的训练方法及系统。

背景技术:

1、存储器系统一般包括存储控制器和动态随机存取存储器(dynamic randomaccess memory,dram)。存储控制器可以通过物理层接口(physical,phy)向dram中写入数据也可以从dram中读取数据,即phy与dram之间进行通信。双倍速率同步动态随机存取存储器(double data rate dynamic random access memory,ddr dram)是目前一种比较常见的存储器。

2、为了保证phy和dram之间传输的信号的延时符合固态技术协会标准的要求,存储器系统一般会进行调整在ddr和phy之间传输的信号的延时的工作,这个过程也被称之为训练,以确保所传输的信号能被顺利采样到,以保证存储器系统能够准确、可靠地进行的读写操作。随着存储器工作频率提高,目前对存储器系统进行训练的准确性和精度不再能够支持存储器系统能够在较高的频率下稳定可靠地工作。

3、因此,希望提供一种存储器系统的训练方法,能够提高存储器系统的训练的准确性和精度以确保存储器系统能够在较高频率下稳定可靠地工作。

技术实现思路

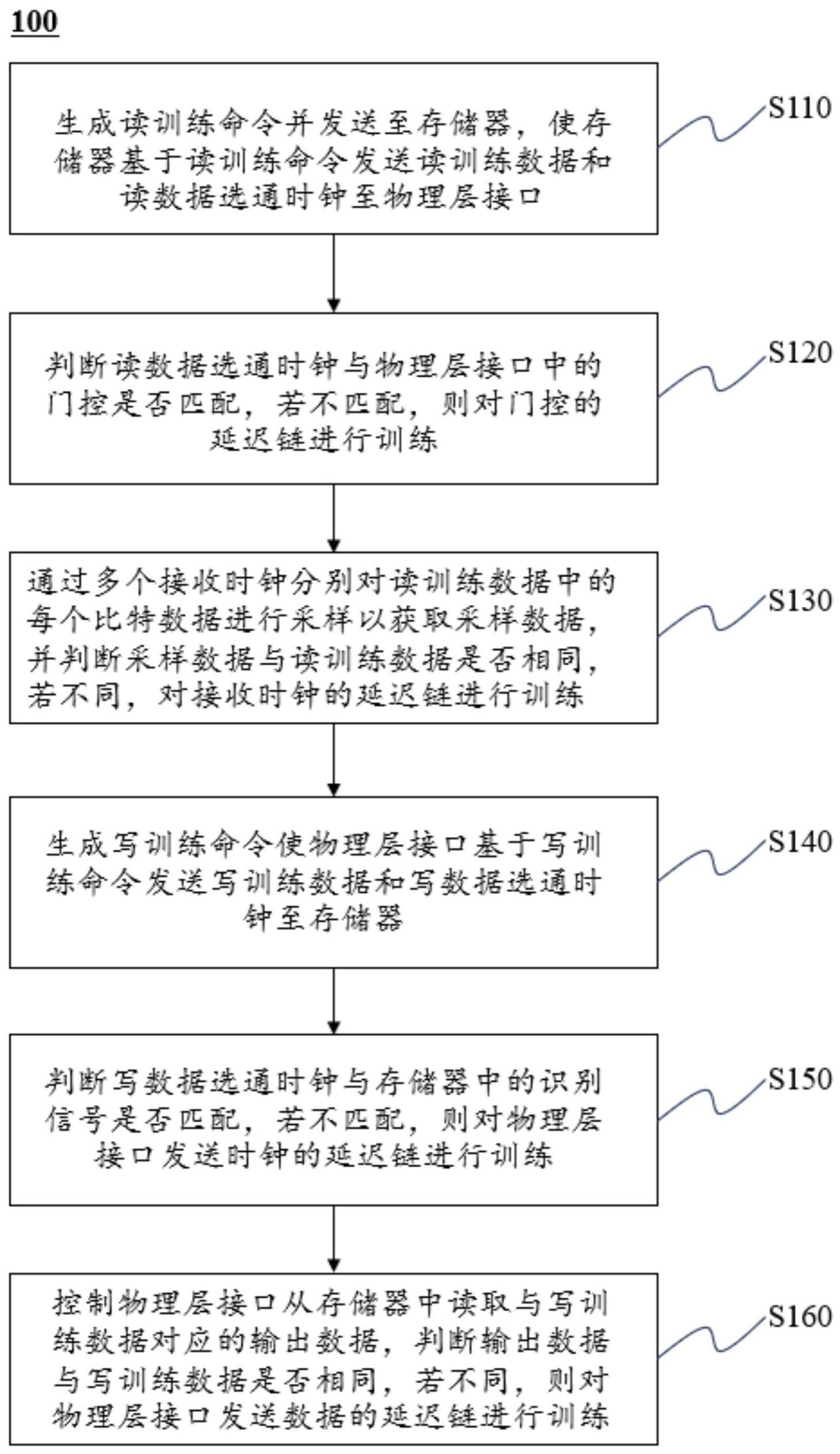

1、本技术实施例之一提供一种存储器系统的训练方法,所述存储器系统包括存储控制器、存储器和连接所述存储控制器和所述存储器的物理层接口,所述训练方法由所述物理层接口中的固件实现,所述训练方法包括:生成读训练命令并发送至所述存储器,使所述存储器基于所述读训练命令发送读训练数据和读数据选通时钟至所述物理层接口;其中,所述读训练数据被分成多个比特数据,所述读数据选通时钟基于所述读训练数据的比特数量被分成多个接收时钟;判断所述读数据选通时钟与所述物理层接口中的门控是否匹配,若不匹配,则对所述门控的延迟链进行训练;通过所述多个接收时钟分别对所述读训练数据的每个比特数据进行采样以获取采样数据,并判断所述采样数据与所述读训练数据是否相同,若不同,对所述接收时钟的延迟链进行训练; 生成写训练命令使所述物理层接口基于所述写训练命令发送写训练数据和写数据选通时钟至所述存储器;判断所述写数据选通时钟与所述存储器中的识别信号是否匹配,若不匹配,则对所述物理层接口发送时钟的延迟链进行训练;控制所述物理层接口从所述存储器中读取与所述写训练数据对应的输出数据,判断所述输出数据与所述写训练数据是否相同,若不同,则对所述物理层接口发送数据的延迟链进行训练。

2、在一些实施例中,所述对所述门控的延迟链进行训练,包括:每次按照第一预定步长调整所述门控的延迟链,在所述门控的延迟链的每次调整后,所述读数据选通时钟的开始边沿会对所述门控进行采样;若在第n次和第n+1次按照第一预定步长调整所述门控的延迟链后,所述读数据选通时钟的开始边沿对所述门控进行采样得到的结果分别为低电平信号和高电平信号,则确定所述读数据选通时钟与所述门控匹配,所述门控的延迟链在第n+1次按照第一预定步长调整后便不再调整;其中,n为大于0的整数。

3、在一些实施例中,所述对所述接收时钟的延迟链进行训练,包括:每次按照第二预定步长调整所述接收时钟的延迟链,在所述接收时钟的延迟链的每次调整后,所述多个接收时钟会分别对所述读训练数据的每个比特数据重新进行采样以重新获取采样数据;若在第n次按照第二预定步长调整所述接收时钟的延迟链后,所述多个接收时钟分别对所述读训练数据的每个比特数据重新进行采样得到的采样数据与所述读训练数据相同,所述接收时钟的延迟链在第n次按照第二预定步长调整后便不再调整;其中,n为大于0的整数。

4、在一些实施例中,所述对所述物理层接口发送时钟的延迟链进行训练,包括:每次按照第三预定步长调整所述物理层接口发送时钟的延迟链,在所述物理层接口发送时钟的延迟链每次调整后,物理层接口所述写数据选通时钟的开始边沿会移动一个第三预定步长并被重新发送到所述存储器中,所述写数据选通时钟的开始边沿会对所述识别信号进行采样;若在第n次和第n+1次按照第三预定步长调整所述物理层接口发送时钟的延迟链,所述写数据选通时钟的开始边沿对所述识别信号进行采样得到的结果分别为低电平信号和高电平信号,则确定所述写数据选通时钟与所述识别信号匹配,所述物理层接口发送时钟的延迟链在第n+1次按照第三预定步长调整后便不再调整;其中,n为不小于0的整数。

5、在一些实施例中,所述对所述物理层接口发送数据的延迟链进行训练,包括:每次按照第四预定步长调整所述物理层接口发送数据的延迟链,在所述物理层接口发送数据的延迟链每次调整后,所述物理层接口重新发送写训练数据到所述存储器中并从所述存储器中读取与所述写训练数据对应的输出数据;若在第n次按照第四预定步长调整所述物理层接口发送数据的延迟链后,所述输出数据与所述写训练数据相同,所述物理层接口发送数据的延迟链在第n次按照第四预定步长调整后便不再调整;其中,n为大于0的整数。

6、在一些实施例中,在生成读训练命令之前,所述训练方法还包括:控制所述物理层接口发送测试命令到所述存储器;判断所述测试命令是否与所述存储器的内部时钟匹配,若不匹配,则对所述物理层接口发送命令的延迟链进行训练。

7、在一些实施例中,所述对所述物理层接口发送命令的延迟链进行训练,包括:通过n次按照第五预定步长调整所述物理层接口发送命令的延迟链,使发送到所述存储器中的测试命令的开始边沿与所述内部时钟的开始边沿对齐;其中,在每次按照第五预定步长调整所述物理层接口发送命令的延迟链后,物理层接口会重新发送测试命令到所述存储器中并由所述内部时钟的开始边沿对测试命令进行采样,所述内部时钟对第n次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为高电平信号,而所述内部时钟对第n-1次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为低电平信号,n为大于1的整数;在发送到所述存储器中的测试命令的开始边沿与所述内部时钟的开始边沿对齐后,再通过m次按照第五预定步长调整所述物理层接口发送命令的延迟链,使发送到所述存储器中的测试命令的结束边沿与所述内部时钟的开始边沿对齐;其中,所述内部时钟对第m次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为低电平信号,而所述内部时钟对第m-1次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为高电平信号,m为大于1的整数;在发送到所述存储器中的测试命令的结束边沿与所述内部时钟的开始边沿对齐后,再基于m/2个第五预定步长调整所述物理层接口发送命令的延迟链,使物理层接口重新发送到所述存储器中的测试命令的中间沿与所述内部时钟的开始边沿对齐。

8、在一些实施例中,在对所述物理层接口发送数据的延迟链进行训练之后,所述训练方法还包括:控制所述物理层接口先后向所述存储器写入数据和读取数据;判断所述物理层接口写入的数据和读取到的数据是否相同,若不同,则对所述存储器系统配置的参考电压进行训练。

9、在一些实施例中,所述对所述存储器系统配置的参考电压进行训练,包括:每次按照预定调节幅度调整所述存储器系统配置的参考电压,在存储器系统配置的参考电压的每次调整后,所述物理层接口会先后向所述存储器写入数据和读取数据;若在第n次按照预定调节幅度调整所述存储器系统配置的参考电压后,所述物理层接口写入到所述存储器中的数据和从所述存储器读取到的数据相同,所述存储器系统配置的参考电压在第n次按照预定调节幅度调整后便不再调整;其中,n为大于0的整数。

10、本技术实施例之一提供一种存储器系统的训练系统,所述存储器系统包括存储控制器、存储器和连接所述存储控制器和所述存储器的物理层接口,所述训练系统集成在所述物理层接口中,所述训练系统包括:读训练命令生成模块,所述读训练命令生成模块用于生成读训练命令并发送至所述存储器,使所述存储器基于所述读训练命令发送读训练数据和读数据选通时钟至所述物理层接口;其中,所述读训练数据被分成多个比特数据,所述读数据选通时钟基于所述读训练数据的比特数量被分成多个接收时钟;第一训练模块,所述第一训练模块用于判断所述读数据选通时钟与所述物理层接口中的门控是否匹配,若不匹配,则对所述门控的延迟链进行训练;第二训练模块,所述第二训练模块用于通过所述多个接收时钟分别对所述读训练数据的每个比特数据进行采样以获取采样数据,并判断所述采样数据与所述读训练数据是否相同,若不同,对所述接收时钟的延迟链进行训练;写训练命令生成模块,所述写训练命令生成模块用于生成写训练命令使所述物理层接口基于所述写训练命令发送写训练数据和写数据选通时钟至所述存储器;第三训练模块,所述第三训练模块用于判断所述写数据选通时钟与所述存储器中的识别信号是否匹配,若不匹配,则对所述物理层接口发送时钟的延迟链进行训练;第四训练模块,所述第四训练模块用于控制所述物理层接口从所述存储器中读取与所述写训练数据对应的输出数据,判断所述输出数据与所述写训练数据是否相同,若不同,则对所述物理层接口发送数据的延迟链进行训练。

11、在一些实施例中,所述第一训练模块用于:每次按照第一预定步长调整所述门控的延迟链,在所述门控的延迟链的每次调整后,所述读数据选通时钟的开始边沿会对所述门控进行采样;若在第n次和第n+1次按照第一预定步长调整所述门控的延迟链后,所述读数据选通时钟的开始边沿对所述门控进行采样得到的结果分别为低电平信号和高电平信号,则确定所述读数据选通时钟与所述门控匹配,所述门控的延迟链在第n+1次按照第一预定步长调整后便不再调整;其中,n为大于0的整数。

12、在一些实施例中,所述第二训练模块用于:每次按照第二预定步长调整所述接收时钟的延迟链,在所述接收时钟的延迟链的每次调整后,所述多个接收时钟会分别对所述读训练数据的每个比特数据重新进行采样以重新获取采样数据;若在第n次按照第二预定步长调整所述接收时钟的延迟链后,所述多个接收时钟分别对所述读训练数据的每个比特数据重新进行采样得到的采样数据与所述读训练数据相同,所述接收时钟的延迟链在第n次按照第二预定步长调整后便不再调整;其中,n为大于0的整数。

13、在一些实施例中,所述第三训练模块用于:每次按照第三预定步长调整所述物理层接口发送时钟的延迟链,在所述物理层接口发送时钟的延迟链每次调整后,物理层接口所述写数据选通时钟的开始边沿会移动一个第三预定步长并被重新发送到所述存储器中,所述写数据选通时钟的开始边沿会对所述识别信号进行采样;若在第n次和第n+1次按照第三预定步长调整所述物理层接口发送时钟的延迟链,所述写数据选通时钟的开始边沿对所述识别信号进行采样得到的结果分别为低电平信号和高电平信号,则确定所述写数据选通时钟与所述识别信号匹配,所述物理层接口发送时钟的延迟链在第n+1次按照第三预定步长调整后便不再调整;其中,n为不小于0的整数。

14、在一些实施例中,所述第四训练模块用于:每次按照第四预定步长调整所述物理层接口发送数据的延迟链,在所述物理层接口发送数据的延迟链每次调整后,所述物理层接口重新发送写训练数据到所述存储器中并从所述存储器中读取与所述写训练数据对应的输出数据;若在第n次按照第四预定步长调整所述物理层接口发送数据的延迟链后,所述输出数据与所述写训练数据相同,所述物理层接口发送数据的延迟链在第n次按照第四预定步长调整后便不再调整;其中,n为大于0的整数。

15、在一些实施例中,所述训练系统还包括第五训练模块,所述第五训练模块用于在生成读训练命令之前控制所述物理层接口发送测试命令到所述存储器,并判断所述测试命令是否与所述存储器的内部时钟匹配,若不匹配,则对所述物理层接口发送命令的延迟链进行训练。

16、在一些实施例中,所述第五训练模块用于:通过n次按照第五预定步长调整所述物理层接口发送命令的延迟链,使发送到所述存储器中的测试命令的开始边沿与所述内部时钟的开始边沿对齐;其中,在每次按照第五预定步长调整所述物理层接口发送命令的延迟链后,物理层接口会重新发送测试命令到所述存储器中并由所述内部时钟的开始边沿对测试命令进行采样,所述内部时钟对第n次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为高电平信号,而所述内部时钟对第n-1次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为低电平信号,n为大于1的整数;在发送到所述存储器中的测试命令的开始边沿与所述内部时钟的开始边沿对齐后,再通过m次按照第五预定步长调整所述物理层接口发送命令的延迟链,使发送到所述存储器中的测试命令的结束边沿与所述内部时钟的开始边沿对齐;其中,所述内部时钟对第m次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为低电平信号,而所述内部时钟对第m-1次按照第五预定步长调整所述物理层接口发送命令的延迟链后物理层接口发送到所述存储器中的测试命令进行采样的结果为高电平信号,m为大于1的整数;在发送到所述存储器中的测试命令的结束边沿与所述内部时钟的开始边沿对齐后,再基于m/2个第五预定步长调整所述物理层接口发送命令的延迟链,使物理层接口重新发送到所述存储器中的测试命令的中间沿与所述内部时钟的开始边沿对齐。

17、在一些实施例中,所述训练系统还包括第六训练模块,所述第六训练模块用于在对所述物理层接口发送数据的延迟链进行训练之后控制所述物理层接口先后向所述存储器写入数据和读取数据,并判断所述物理层接口写入的数据和读取到的数据是否相同,若不同,则对所述存储器系统配置的参考电压进行训练。

18、在一些实施例中,所述第六训练模块用于:每次按照预定调节幅度调整所述存储器系统配置的参考电压,在存储器系统配置的参考电压的每次调整后,所述物理层接口会先后向所述存储器写入数据和读取数据;若在第n次按照预定调节幅度调整所述存储器系统配置的参考电压后,所述物理层接口写入到所述存储器中的数据和从所述存储器读取到的数据相同,所述存储器系统配置的参考电压在第n次按照预定调节幅度调整后便不再调整;其中,n为大于0的整数。

19、本技术实施例提供的训练方法及训练系统通过依次对存储器系统进行与读操作相关的训练(包括先后对在物理层接口处读数据选通时钟的门控的延迟链、接收时钟的延迟链进行调整)、与写操作相关的训练(包括先后对物理层接口发送时钟的延迟链、发送数据的延迟链进行调整),使得对存储器系统的训练可以按照特定的时序进行,能够提高对存储器系统训练的准确性和精度,从而能够保证存储器系统能够在较高的工作频率下稳定可靠地工作。除此之外,本技术实施例提供的训练方法由物理层接口中的固件实现,具体地,固件可以通过驱动物理层接口中相应的硬件电路来实现本技术实施例提供的训练方法,采用软硬件结合的方式,可以实现更多的功能,以应对更复杂的训练环境,并且具有更多的调试手段,便于进行故障定位,同时具有较低的功耗以及较高的性能。除此之外通过本技术实施例提供的训练方法在对存储器系统进行训练时,无需存储控制器参与,可以避免训练结果发生扭曲或需要花费更多的后期数据处理,并且也避免了存储控制器参与训练而导致自身的启动效率降低。

- 还没有人留言评论。精彩留言会获得点赞!