一种基于HSM的层次化时序模型提取方法

本发明申请属于数字芯片设计领域,尤其涉及一种基于hsm的层次化时序模型提取方法。

背景技术:

1、在芯片制造过程中,每个晶圆的每块晶片的电气特性参数不同会导致门单元和金属线的延迟有所区别,这种偏差导致了芯片各参数的理论值与实际值的结果之间的存在差异。工艺偏差可以分为系统偏差和非系统偏差。系统偏差来源于或化学机械或光学接近校正,所述的偏差在制造的各环节中均会引入,可通过工艺、电压和温度(pvt)的线性变化关系准确的预测和修正;而非系统偏差在制造的各个步骤中随机产生,由于它在统计学上呈现完全随机、独立,缺乏明显的相关性,因此无法轻松进行建模。非系统偏差可分为全局偏差(片间偏差)和局部偏差(片内偏差),其中片间偏差是由于制造过程中的工艺变化、设备不均匀性等因素引起的。而片内偏差源自于工艺方面的随机掺杂剂波动、线边缘粗糙度、氧化物厚度变化,以及电压方面的内部压降和温度方面的结温变化。如果在设计的过程中忽视片内偏差,可能会引发后期的硅故障。所述的偏差的来源显然会使数字电路设计的分析及模拟更为困难,因此必须在时序分析期间将所述的偏差多加精确考虑。

2、综上所述,随着芯片设计的复杂性和规模的增加,时序分析成为了一个关键的挑战。先进的工艺设计提升了后端设计难度,传统的时序分析方法往往面临着计算复杂度高、分析效率低下的问题,所述的时序问题可能导致性能下降、功耗增加、电路故障等。因此,为了缩短设计周期,提高性能、降低功耗、减少电路故障和提高产品竞争力,需要一个有效的解决方案来提高时序分析的准确性和效率。

3、现有的分层设计模型主要采用以下几种:提取时序模型(extracted timingmodels,etm)技术;快速时序模型quick timing model(qtm)技术;超大规模时序模型(hyperscales models,hsm)技术。

4、etm是直接从较低层块网表(例如,单个ip设计元件(intellectual propertydesign,ip design))提取的块时序模型。该模型由该块的时钟、输入和输出引脚之间的一组时序弧组成。该模型可以用来代替完整的块网表,可根据每个etm依照其片上偏差进行减免系数(derating)的增减,以便在下一个更高层次上进行分析。etm是可移植的并且可以轻松导出到其他工具,因此它们通常用于表示ip design元件的时序。由于etm仅由时序弧组成,因此可以对块的内部逻辑进行保密。从外来看,一个etm就像一个黑盒子,只能看到模型的端口。它保留输入到输出路径组的建立时间与保持时间等信息。etm模型类似的单元的库,可通过查看端口和引脚的信息,所得到的延迟信息。而除了输入到输出之外的路径组内部具体的延迟都是被隐藏的。这种etm模型的优点就是抽取速度快,但是缺点是不太准。相比etm来说,qtm多保留了端口到第一级寄存器的信息,包含了输入到输出、输入到寄存器和寄存器到输出的所有线延迟信息及单元信息。qtm抽取的速度相比etm更慢,准确度更高,一般可以到99%左右。

5、上述方法主要借助于在底层进行分析,在芯片各模块完成时刻,难以减少顶层工作量,无法准确地处理顶层和较低层块之间的时序接口问题。对于大型芯片设计,从层次结构的顶层执行平面时序分析可能会消耗内存资源或使用过多的运行时间。因此,为了适应大型设计,超大规模集成电路时序模型(hyperscales models,hsm)是一种先进的方法,它使用单独的运行来分析块级和顶层部分,并准确地处理顶层和较低层块之间的时序接口。该技术提供了完全平面分析的准确性,同时利用分层块级分析减少的运行时间和内存占用,可以帮助解决芯片行业中的提高时序分析的准确性和效率的问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本技术适用于芯片层次化设计领域,提出一种基于hsm的层次化时序模型提取方法,通过计算并提取模块时序,划分时序接口并集成一个时序库模块。其路径延时计算方法为式(1)所示:

2、slackori-deraterequired_time+deratearrival_time-deratecppr=slacknew 式(1)

3、式中,slackori为未进行片上偏差分析的初始裕量;slacknew为进行片上偏差分析后的时序结果;deraterequired_time为驱动路径的减免系数值,deratearrival_time为捕获路径的减免系数值;deratecppr为共同路径的悲观度补偿值。通过计算其时序延迟并集成为一个时序库,在超大规模流程中,为每个较低级别的块创建一个准确的结构块模型。该模型允许单独分析每个块级设计,同时考虑到更高级别设计的约束和时序特征。处理顶层和块级分析运行之间的接口数据传输,包括输入延迟、输出延迟和跨界效应,例如时序异常、串扰和crpr。集成的时序库具备着与平坦级分析相同的高精度,提供了分层分析的更短的周转时间和更低的内存占用。

4、在分层分析中,提取出来的独立于顶层分析的较低层块的时序,可供予顶层使用,hyperscale模型用来表示层次级别较低的块级设计。每个模型其时序都包括块边界的接口逻辑、顶层精确时序分析所需的所有逻辑,同时排除与顶层时序分析无关的内部逻辑。因此,该模型尽可能快速且紧凑,具有扁平式的分析精度,可减少的运行时间和内存占用,可以帮助解决芯片行业中的提高时序分析的准确性和效率的问题。

5、本发明的目的在于提出一种基于hsm的层次化时序模型提取方法,通过对单个块级设计的时序库,提取出共同类型的时序模型,从而减少布线工具所输入的时序模型文件的数量,减少了工具的运行时间和内存占用、提高布线工具的静态时序分析的准确性和效率、提高布线工具的时序模型设计集成度、减少数字集成电路的设计周期,同时此设计方法适合于大多数大规模静态时序分析的设计中,具有普遍适用性。

6、本发明提出一种基于hsm的层次化时序模型提取方法,其包括下列步骤:

7、在流程设计中采用层次化的设计方法,

8、优选地,所述流程设计中采用层次化的设计方法,全芯片设计可被切分为顶层设计和多个块级设计,块级设计可进行切割提取,实现二级块级设计的形式,可嵌套式结构切割提取,实现多级设计。

9、根据获取数字集成电路设计的关键数据并进行识别,完成信息识别后将信息存储到数据文件;提取出描述数字集成电路的各电路元件相互之间连接关系网表文件、描述数字集成电路设计时序约束的约束文件、描述数字集成电路的各时序路径的信息(例如实例、端口、引脚等);

10、通过脚本获取所述的数字集成电路设计的关键数据,并生成数字集成电路的分析环境;由于布线工具必须在内建自我测试(memory built-in self-test,简称mbist)、低速测试模式(scan mode,简称scan)或功能模式(function mode,简称func)等多个阶段考虑此电路设计的时序验证是否符合使用者需求。根据所述分析环境,提取出描述芯片在布局布线之后实际电路中互连线的标准寄生参数文件并反标到所述数字集成电路中,为所述数字集成电路的所有端口逻辑打上标签;

11、提取出超大规模时序模型,提取出描述约束或者特殊处理的路径的时序模型;超大规模时序模型(hsm),根据此数字集成电路设计的多个工作模式,分别生成多个超大规模时序模型。其中,每个模型中包含了约束信息、非偏差信息、偏差信息、io结构信息。

12、对提取的所述模型的数据文件进行同类型整合。进行文件信息分类合并优化,上述所提取的超大规模时序模型信息可根据是否具有相同特征属性作为参考进行合并,多个时序模型信息可合并为一个完整的时序信息。根据所述的工作模式下提取出的超大规模时序模型的这三大类信息,整合输入输出结构信息、约束文件信息以及超大规模时序模型信息为一个完整的超大规模时序模型。

13、优选地,所述数字集成电路的所有端口逻辑打上标签,将其划分为四个组分别为输入端口到寄存器、输入端口到输出端口、寄存器到寄存器、寄存器到输出端口,提取出影响延时的所有网表、端口和引脚;忽略掉理想化的端口,忽略扇出过高的输入端口,提取出超大规模时序模型。

14、根据所述提取出的超大规模时序模型具备同一类型的信息特性,进行融合为统一信息。详细地,约束文件优化,修订约束文件中不符合提取出的时序信息进行时序约束和修订,新产生的时序端口重映射。

15、优选地,所述提取的文件进行同类型整合,根据三个工作环境所设计提取出hsm模型可分为hsm1、hsm2、hsm3,每个hsm模型里包含了四个文件,分别为sdc文件、contex文件、nocv文件以及ocv文件。

16、优选地,提取出的12个文件合并为3个模型文件,以hsm_n作为一维检索标签,以mode作为二维检索标签,分别为以sdc、context、nocv&ocv作为三维子检索分别合并为三个文件,合并后的可检索关键电路时序信息。

17、通过使用所述的超大规模时序模型来模拟该数字集成电路设计的时序验证。

18、本技术提供的一种基于hsm的层次化时序模型提取方法,通过简单的分类合并,将各信息的相同属性进行融合,实现了大量文件向少量高集成度文件的转换。随着此流程的执行,使得所述的模型尽可能快速且紧凑,可减少的运行时间和内存占用。高集成度的时序模型,提高布线工具的静态时序分析的准确性和效率。集成后的时序模型,易于管理方便使用,可减少数字集成电路的设计周期。如上所述,本发明的一种基于hsm的层次化时序模型提取方法,具有以下有益效果:

19、目前大多数大规模数字集成电路在设计中,当芯片的规模过大时,考虑到软件的承受能力和运行时间,我们不得不使用层次化流程。直接进行全芯片级的sta,那么不仅需要大量的分析时间,而且分析的复杂程度也将十分巨大。每一个层次都从具有可移植性和未来泛用性的角度出发,对各个层次的电路块级设计进行时序分析,当各块级电路时序验证通过后,再对整个芯片进行全面的静态时序分析,可实现降低静态分析的复杂度,并行运行避免耗费过多的验证时间。

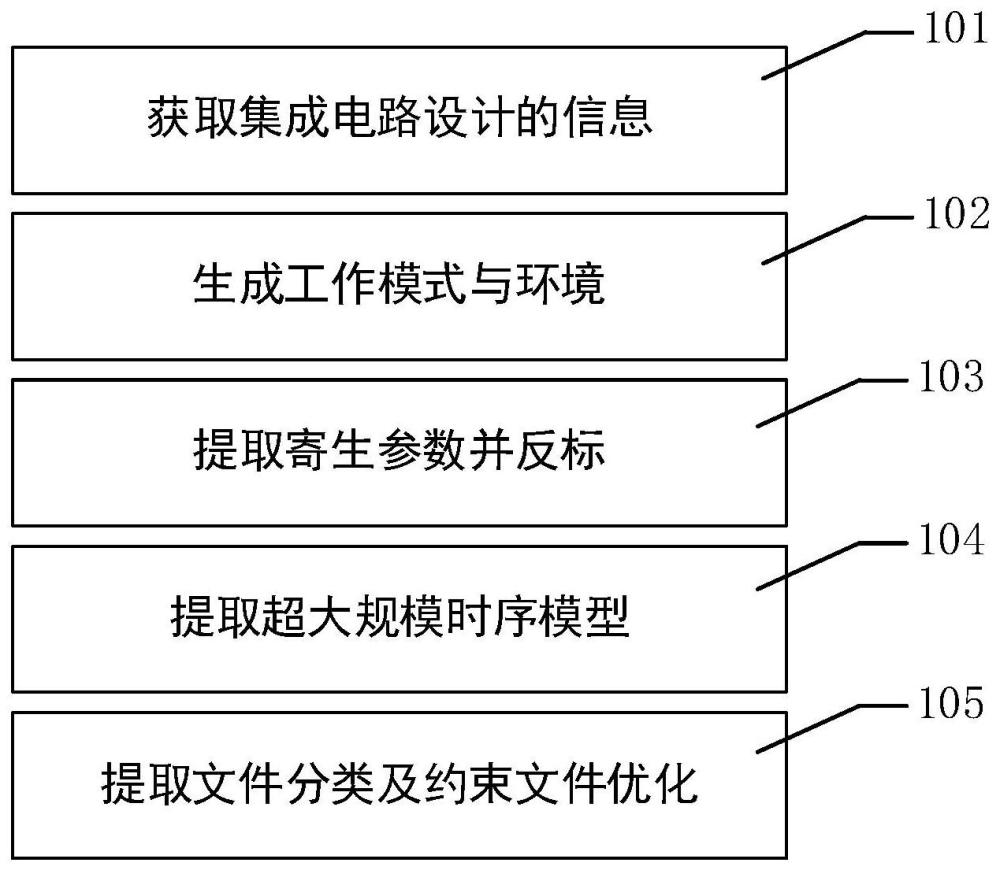

20、所述的超大规模时序模型与标准的扁平化流程或者旧版的层次化流程相比,本技术提出的一种基于hsm的层次化时序模型提取方法,可实现如图1的模型提取流程结合文件合并,在后端布线工具在进行时序模型提取时,通过将约束文件信息、时延信息以及输入输出结构信息集成为一个以单个超大规模时序模型为单位的时序库文件。

21、如图一,通过文件整合与优化,提取出以工作模式、提取时序模型的序列号为标签的一个完整的超大规模的时序库文件。合并共同拥有的条件、环境与特征,突出差异不同的部分,

22、以所述的时序库文件由布线工具所读取,可减少工具的运行时间和内存占用、提高布线工具的静态时序分析的准确性和效率。这样做的好处是能够降低静态分析的复杂度,并行运行避免耗费过多的验证时间。

- 还没有人留言评论。精彩留言会获得点赞!