多芯粒的软件程序配置方法、装置、电子设备及存储介质与流程

本技术涉及半导体,特别是涉及一种多芯粒的软件程序配置方法、装置、电子设备及存储介质。

背景技术:

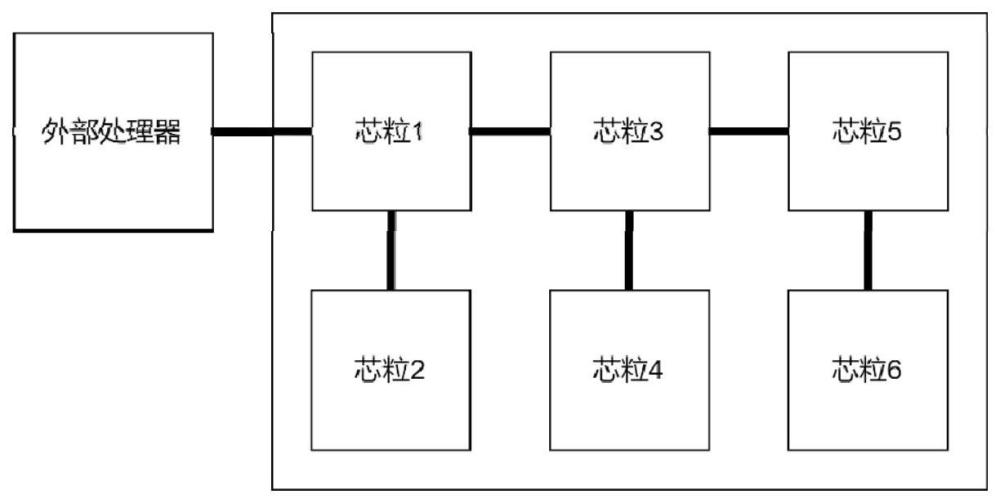

1、在使用芯粒(或小芯片)技术提高整体协处理器芯片计算能力(如人工智能加速)的应用中,经常需要把多颗相同的协处理器芯粒(或小芯片)集成在一个封装内来实现,这些协处理器芯粒在封装内以某种拓扑结构相互连接。如图1所示,单一封装内集成了6颗完全一样的协处理器芯粒,并通过黑色粗线的总线(可以为ucie或者专有的die2die等协议)拓扑进行连接,这些连接一般是通过封装内基板(substrate)来实现。同时,协处理器本身会通过某些高速总线(可以为ucie,pcie或者专有的chip2chip等协议)与外部处理器进行连接,这个连接一般是通过印刷线路板(pcb)来实现。

2、在很多时候,在如图1所示的6颗协处理器芯粒组成的系统中,因为拓扑连接关系的差异,每个协处理器芯粒执行不同的计算任务,也运行着不同的软件程序。这里把这种由物理上完全相同但执行不同任务的协处理器芯粒组成的芯片系统称为同源异构多芯粒协处理器芯片。在实际应用中,在整个同源异构多芯粒系统开始执行正常的计算任务之前,必须为系统中的每个芯粒配置相应的软件程序。由于整个多芯粒系统的计算任务时刻在发生变化,因此这些软件程序需要存储在动态存储器(ram)中,可以是片上的ram,或者是片外的dram。这些软件程序在整个系统启动时或者进行计算任务准备时由片外的主处理器通过外部总线进行配置并传输到各个芯粒节点。

3、在实际应用中,组成芯片的各个芯粒在物理上完全相同(或者仅有每个芯粒的唯一id标识符的差异),因此需要在系统启动或者计算准备的过程中,需要准确识别和定位出整个芯粒连接拓扑结构中各个节点的芯粒,并通过合适的机制从外部处理器传输到各个芯粒节点。

4、在同源异构的多芯粒芯片系统中,因为在晶圆生产过程中所有的处理器芯粒都是一样的,并且通过封装层面的拓扑连接以及系统运行时的动态配置来区分不同芯粒的功能,因此需要一个低成本的机制来给多芯粒芯片中的各个芯粒组件配置所需要的软件程序等。

技术实现思路

1、本技术实施例所要解决的技术问题是提供一种多芯粒的软件程序配置方法、装置、电子设备及存储介质,以实现便捷的芯片软件程序配置,降低了软件程序配置的成本。

2、第一方面,本技术实施例提供了一种多芯粒的软件程序配置方法,所述方法包括:

3、基于两根同步串行总线,将外部处理器与多芯粒芯片系统中多个芯粒串行连接,形成闭合链路;

4、通过所述外部处理器根据所述多芯粒芯片系统中各所述芯粒的两线总线连接拓扑顺序,组成数据帧,并将所述数据帧发送给所述多芯粒芯片系统;所述数据帧包括:帧头和各所述芯粒的数据包,每个所述数据包中包含对应芯粒的软件程序数据;

5、依次由各所述芯粒处理所述数据帧中的各所述芯粒对应的数据包,以完成软件程序的配置。

6、可选地,所述依次由各所述芯粒处理所述数据帧中的各所述芯粒对应的数据包,以完成软件程序的配置,包括:

7、通过第一个芯粒接收所述数据帧中的第一个数据包,并处理所述第一个数据包,以完成软件程序的配置;

8、由所述第一个芯粒将所述数据帧中除所述第一个数据包外的其它数据包按照原始顺序与所述帧头拼合,并在拼合的数据帧的最后端添加与所述第一个数据包长度相同的回传数据包;

9、依次将所述多个芯粒中除所述第一个芯粒外的其它芯粒作为第一个芯粒,执行所述通过第一个芯粒接收所述数据帧中的第一个数据包,至在拼合的数据帧的最后端添加与所述第一个数据包长度相同的回传数据包的步骤,直至所有的芯粒完成软件程序的配置。

10、可选地,在所述依次由各所述芯粒处理所述数据帧中的各所述芯粒对应的数据包,以完成软件程序的配置之后,还包括:

11、通过所述外部处理器接收所述芯粒中最后一个芯粒发送的回传数据帧;

12、通过所述外部处理器根据所述回传数据帧中的回传数据包,确定所述多芯粒芯片系统中的所有芯粒是否完成软件程序配置;

13、在所述所有芯粒中存在未完成软件程序配置的芯粒的情况下,通过所述外部处理器向所述多芯粒芯片系统重新传输数据帧。

14、可选地,在每个所述芯粒内均设置有两线总线中继模块,所述两线总线中继模块包括:状态机,

15、所述依次由各所述芯粒处理所述数据帧中的各所述芯粒对应的数据包,包括:

16、通过所述两线总线中继模块对接收的所述数据帧进行串行转并行处理,并将处理后的数据帧的数据依次缓存于输入fifo队列;

17、通过所述状态机从所述输入fifo队列中读取并处理数据帧中的第一个数据包,并将所述数据帧中除所述第一个数据包外的其它数据包按照原始顺序与所述帧头拼合,在拼合的数据帧的最后端添加与所述第一个数据包长度相同的回传数据包,得到新的数据帧;

18、将所述新的数据帧的数据依次缓存于输出fifo队列;

19、读取所述输出fifo队列中的数据,并进行并行转串行处理,然后发送给下一个芯粒。

20、可选地,所述基于两根同步串行总线,将外部处理器与多芯粒芯片系统中多个芯粒串行连接,形成闭合链路,包括:

21、基于封装内基板,将所述多芯粒芯片系统中的多个芯粒通过所述两根同步串行总线串联连接;

22、基于印刷电路板,将所述外部处理器与所述多个芯粒中串联链路外侧的两个芯粒连接,以形成闭合链路。

23、可选地,所述两根同步串行总线为:时钟信号的spi总线和数据信号的spi总线。

24、第二方面,本技术实施例提供了一种多芯粒的软件程序配置装置,所述装置包括:

25、闭合链路形成模块,用于基于两根同步串行总线,将外部处理器与多芯粒芯片系统中多个芯粒串行连接,形成闭合链路;

26、数据帧发送模块,用于通过所述外部处理器根据所述多芯粒芯片系统中各所述芯粒的两线总线连接拓扑顺序,组成数据帧,并将所述数据帧发送给所述多芯粒芯片系统;所述数据帧包括:帧头和各所述芯粒的数据包,每个所述数据包中包含对应芯粒的软件程序数据;

27、软件程序配置模块,用于依次由各所述芯粒处理所述数据帧中的各所述芯粒对应的数据包,以完成软件程序的配置。

28、可选地,所述软件程序配置模块包括:

29、软件程序配置单元,用于通过第一个芯粒接收所述数据帧中的第一个数据包,并处理所述第一个数据包,以完成软件程序的配置;

30、数据帧处理单元,用于由所述第一个芯粒将所述数据帧中除所述第一个数据包外的其它数据包按照原始顺序与所述帧头拼合,并在拼合的数据帧的最后端添加与所述第一个数据包长度相同的回传数据包;

31、所有芯粒配置单元,用于依次将所述多个芯粒中除所述第一个芯粒外的其它芯粒作为第一个芯粒,执行所述软件程序配置单元和所述数据帧处理单元,直至所有的芯粒完成软件程序的配置。

32、可选地,所述装置还包括:

33、回传数据帧接收模块,用于通过所述外部处理器接收所述芯粒中最后一个芯粒发送的回传数据帧;

34、程序配置确定模块,用于通过所述外部处理器根据所述回传数据帧中的回传数据包,确定所述多芯粒芯片系统中的所有芯粒是否完成软件程序配置;

35、数据帧重传模块,用于在所述所有芯粒中存在未完成软件程序配置的芯粒的情况下,通过所述外部处理器向所述多芯粒芯片系统重新传输数据帧。

36、可选地,在每个所述芯粒内均设置有两线总线中继模块,所述两线总线中继模块包括:状态机,

37、所述数据帧发送模块包括:

38、数据帧处理单元,用于通过所述两线总线中继模块对接收的所述数据帧进行串行转并行处理,并将处理后的数据帧的数据依次缓存于输入fifo队列;

39、数据包处理单元,用于通过所述状态机从所述输入fifo队列中读取并处理数据帧中的第一个数据包,并将所述数据帧中除所述第一个数据包外的其它数据包按照原始顺序与所述帧头拼合,在拼合的数据帧的最后端添加与所述第一个数据包长度相同的回传数据包,得到新的数据帧;

40、数据缓存单元,用于将所述新的数据帧的数据依次缓存于输出fifo队列;

41、数据发送单元,用于读取所述输出fifo队列中的数据,并进行并行转串行处理,然后发送给下一个芯粒。

42、可选地,所述闭合链路形成模块包括:

43、串联连接单元,用于基于封装内基板,将所述多芯粒芯片系统中的多个芯粒通过所述两根同步串行总线串联连接;

44、闭合链路形成单元,用于基于印刷电路板,将所述外部处理器与所述多个芯粒中串联链路外侧的两个芯粒连接,以形成闭合链路。

45、可选地,所述两根同步串行总线为:时钟信号的spi总线和数据信号的spi总线。

46、第三方面,本技术实施例提供了一种电子设备,包括:

47、处理器、存储器以及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述程序时实现上述任一项所述的多芯粒的软件程序配置方法。

48、第四方面,本技术实施例提供了一种计算机可读存储介质,当所述存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行上述任一项所述的多芯粒的软件程序配置方法。

49、与现有技术相比,本技术实施例包括以下优点:

50、本技术实施例中,通过基于两根同步串行总线,将外部处理器与多芯粒芯片系统中多个芯粒串行连接,形成闭合链路。通过外部处理器根据多芯粒芯片系统中各芯粒的两线总线连接拓扑顺序,组成数据帧,并将数据帧发送给多芯粒芯片系统,数据帧包括:帧头和各芯粒的数据包,每个数据包中包含对应芯粒的软件程序数据。依次由各芯粒处理所述数据帧中的各芯粒对应的数据包,以完成软件程序的配置。本技术实施例通过将外部处理器与多芯粒芯片系统中多个芯粒串行连接,形成闭合链路,并按照多芯粒芯片系统中各芯粒的两线总线连接拓扑顺序,组成数据帧,发送给多芯粒芯片系统以进行软件程序配置,从而可以实现便捷的芯片软件程序配置,同时,可以降低软件程序配置的成本。

51、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

- 还没有人留言评论。精彩留言会获得点赞!