缓冲器和反相器的布局方法、装置和电子设备与流程

本技术涉及数字集成电路,具体而言,涉及一种缓冲器和反相器的布局方法、装置和电子设备。

背景技术:

1、在数字集成电路布局布线后,待优化驱动门的总负载电容包括驱动的导线电容和负载门的输入端电容之和,通常需要插入缓冲器,以放大信号,从而驱动大电容导线和负载门,从而减小待优化驱动门的逻辑门延迟和互连导线延迟。

2、目前,通常是基于van ginneken dynamic programing(vgdp)算法,在使用缓冲器进行优化的情况下,使用动态规划快速求得最优缓冲器插入解,并通过对vgdp算法进行改进提高算法速度。

3、然而,上述优化方式只能插入非反向型的缓冲器,无法进一步改进电路延时。

技术实现思路

1、有鉴于此,本技术实施例提供了一种缓冲器和反相器的布局方法、装置和电子设备,以进一步改进电路延时。

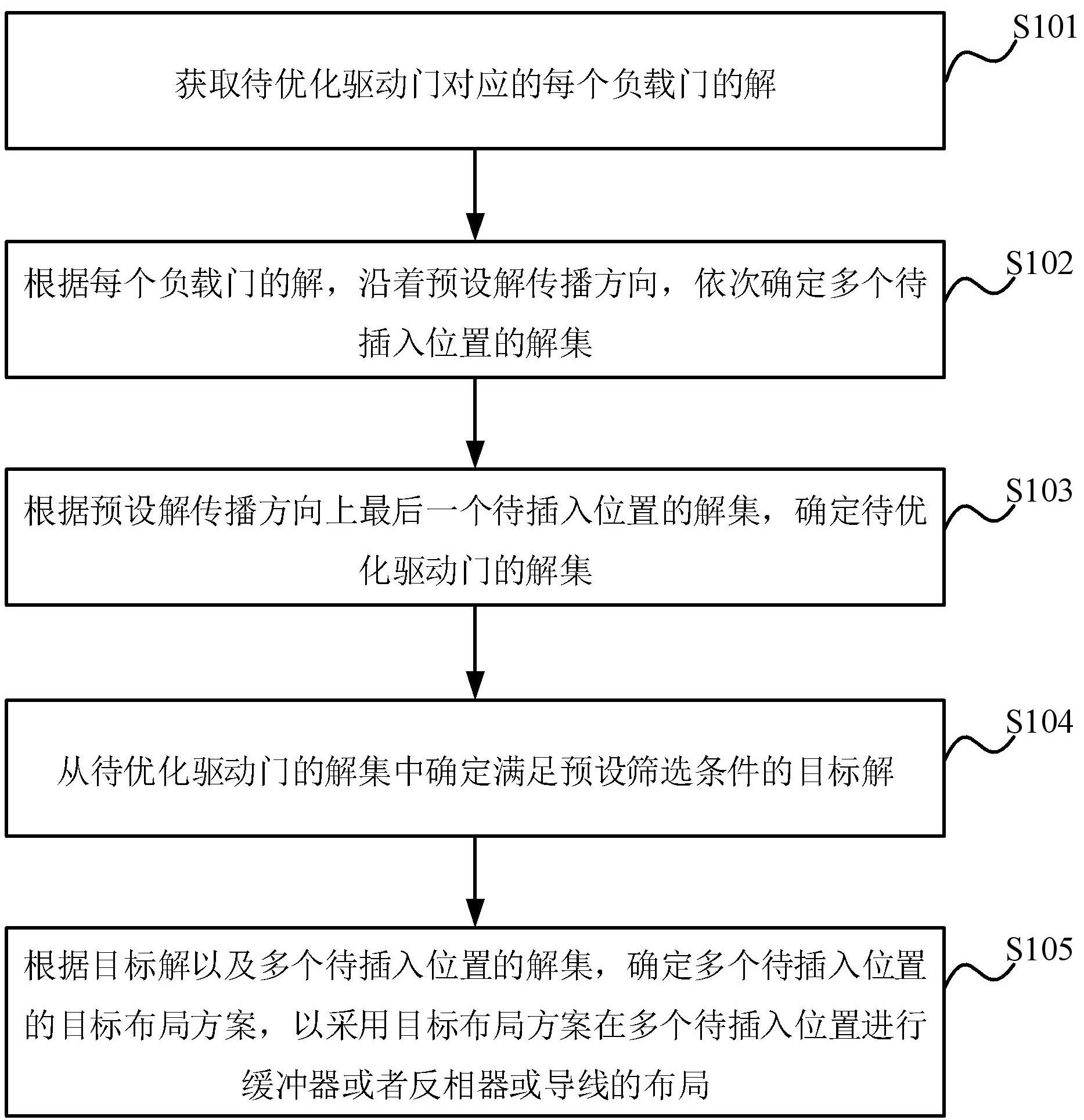

2、第一方面,本技术实施例提供了一种缓冲器和反相器的布局方法,包括:

3、获取待优化驱动门对应的每个负载门的解,所述每个负载门的解包括:所述每个负载门的输入电容、所述每个负载门的信号所需时间以及所述每个负载门的相位指示信息,所述每个负载门的信号所需时间为在满足预设时序约束时,所述每个负载门之后的电路要求所述每个负载门的最迟信号到达时间,所述每个负载门的相位指示信息用于指示传输至所述每个负载门的信号相位与待优化驱动门的信号相位是否一致;

4、根据所述每个负载门的解,沿着预设解传播方向,依次确定多个待插入位置的解集,每个待插入位置的解集中的每个解包括:所述每个待插入位置的输入电容、所述每个待插入位置的信号所需时间以及所述每个待插入位置的相位指示信息,所述每个待插入位置的解集中的每个解对应所述每个待插入位置的一个布局方案,所述一个布局方案用于指示在所述每个待插入位置布局缓冲器或反相器或导线,所述预设解传播方向为所述每个负载门到所述待优化驱动门的方向;

5、根据所述预设解传播方向上最后一个待插入位置的解集,确定所述待优化驱动门的解集,所述待优化驱动门的解集中每个解包括:所述待优化驱动门的输入电容、所述待优化驱动门的信号所需时间以及所述待优化驱动门的相位指示信息;

6、从所述待优化驱动门的解集中确定满足预设筛选条件的目标解;

7、根据所述目标解以及所述多个待插入位置的解集,分别确定所述多个待插入位置的目标布局方案,以采用所述目标布局方案在所述多个待插入位置进行缓冲器或反相器或导线的布局。

8、在一可选的实施方式中,所述根据所述每个负载门的解,沿着预设解传播方向,依次确定多个待插入位置的解集,包括:

9、根据所述每个待插入位置的多种布局方案,以及所述预设解传播方向上所述每个待插入位置的前一位置的解,确定所述每个待插入位置的解集,所述多种布局方案包括:多种缓冲器布局方案、多种反相器布局方案以及导线布局方案;

10、其中,所述预设解传播方向上第一个待插入位置的前一位置的解为:所述每个负载门的解,所述预设解传播方向上其它待插入位置的前一位置的解为:所述其它待插入位置的前一待插入位置的解。

11、在一可选的实施方式中,若目标待插入位置的多种布局方案包括:至少两级布局单元的多种布局方案;

12、所述根据所述每个待插入位置的多种布局方案,以及所述预设解传播方向上所述每个待插入位置的前一位置的解,确定所述每个待插入位置的解集,包括:

13、根据所述目标待插入位置的最后一级布局单元的多种布局方案,以及所述目标待插入位置的前一位置的解,确定所述目标待插入位置的最后一级布局单元的解集;

14、根据所述最后一级布局单元的解集以及所述目标待插入位置的其它级布局单元的多种布局方案,逐级确定所述其它级布局单元的解集;

15、根据所述最后一级布局单元的解集以及所述其它级布局单元的解集,确定所述目标待插入位置的解集,所述目标待插入位置的解集包括:所述最后一级布局单元的解集以及所述其它级布局单元的解集。

16、在一可选的实施方式中,所述根据所述每个待插入位置的多种布局方案,以及所述预设解传播方向上所述每个待插入位置的前一位置的解,确定所述每个待插入位置的解集,包括:

17、根据所述多种布局方案,以及所述前一位置的解集中的每个解,确定所述每个待插入位置的正相位解集和负相位解集。

18、在一可选的实施方式中,所述根据所述多种布局方案,以及所述前一位置的解集中的每个解,确定所述每个待插入位置的正相位解集和负相位解集,包括:

19、根据所述预设筛选条件,分别对所述前一位置的正相位解集中的每个解和负相位解集中的每个解进行筛选,得到所述前一位置的筛选后的正相位解集和筛选后的负相位解集;

20、根据所述多种布局方案、所述筛选后的正相位解集中的每个解以及所述筛选后的负相位解集中的每个解,确定所述每个待插入位置的正相位解集和负相位解集。

21、在一可选的实施方式中,所述根据所述预设解传播方向上最后一个待插入位置的解集,确定所述待优化驱动门的解集,包括:

22、根据所述最后一个待插入位置的解集,确定所述待优化驱动门的扇出端的解集,所述扇出端的解集包括:所述扇出端的正相位解集;

23、获取在所述扇出端的正相位解集中每个解下所述待优化驱动门的延迟;

24、根据所述扇出端的正相位解集、所述待优化驱动门的电容以及所述待优化驱动门的延迟,确定所述待优化驱动门的扇入端的解集。

25、在一可选的实施方式中,所述根据所述扇出端的正相位解集、所述待优化驱动门的电容以及所述待优化驱动门的延迟,确定所述待优化驱动门的扇入端的解集,包括:

26、获取所述扇出端对应的导线延迟;

27、根据所述扇出端的正相位解集、所述待优化驱动门的电容、所述待优化驱动门的延迟以及所述每个解对应的导线延迟,确定所述待优化驱动门的扇入端的解集。

28、在一可选的实施方式中,所述根据所述每个待插入位置的多种布局方案,以及所述预设解传播方向上所述每个待插入位置的前一位置的解,确定所述每个待插入位置的解集,包括:

29、获取所述每个待插入位置对应的导线延迟;

30、根据所述每个待插入位置的多种布局方案、所述前一位置的解,以及所述每个待插入位置对应的导线延迟,确定所述每个待插入位置的解集。

31、第二方面,本技术实施例还提供了一种缓冲器和反相器的布局装置,包括:

32、获取模块,用于获取待优化驱动门对应的每个负载门的解,所述每个负载门的解包括:所述每个负载门的输入电容、所述每个负载门的信号所需时间以及所述每个负载门的相位指示信息,所述每个负载门的信号所需时间为在满足预设时序约束时,所述每个负载门之后的电路要求所述每个负载门的最迟信号到达时间,所述每个负载门的相位指示信息用于指示传输至所述每个负载门的信号相位与待优化驱动门的信号相位是否一致;

33、确定模块,用于根据所述每个负载门的解,沿着预设解传播方向,依次确定多个待插入位置的解集,每个待插入位置的解集中的每个解包括:所述每个待插入位置的输入电容、信号传输至所述每个待插入位置的信号所需时间以及所述每个待插入位置的相位指示信息,所述每个待插入位置的解集中的每个解对应所述每个待插入位置的一个缓冲器布局方案或者一个反相器布局方案,所述预设解传播方向为所述每个负载门到所述待优化驱动门的方向;

34、所述确定模块,还用于根据所述预设解传播方向上最后一个待插入位置的解集,确定所述待优化驱动门的解集,所述待优化驱动门的解集中每个解包括:所述待优化驱动门的输入电容、所述待优化驱动门的信号所需时间以及所述待优化驱动门的相位指示信息;

35、所述确定模块,还用于从所述待优化驱动门的解集中确定满足预设筛选条件的目标解;

36、所述确定模块,还用于根据所述目标解以及所述多个待插入位置的解集,分别确定所述多个待插入位置的目标布局方案,以采用所述目标布局方案在所述多个待插入位置进行缓冲器或反相器的布局。

37、在一可选的实施方式中,所述确定模块,具体用于:

38、根据所述每个待插入位置的多种布局方案,以及所述预设解传播方向上所述每个待插入位置的前一位置的解,确定所述每个待插入位置的解集,所述多种布局方案包括:多种缓冲器布局方案、多种反相器布局方案以及导线布局方案;

39、其中,所述预设解传播方向上第一个待插入位置的前一位置的解为:所述每个负载门的解,所述预设解传播方向上其它待插入位置的前一位置的解为:所述其它待插入位置的前一待插入位置的解。

40、在一可选的实施方式中,若目标待插入位置的多种布局方案包括:至少两级布局单元的多种布局方案;所述确定模块,具体用于:

41、根据所述目标待插入位置的最后一级布局单元的多种布局方案,以及所述目标待插入位置的前一位置的解,确定所述目标待插入位置的最后一级布局单元的解集;

42、根据所述最后一级布局单元的解集以及所述目标待插入位置的其它级布局单元的多种布局方案,逐级确定所述其它级布局单元的解集;

43、根据所述最后一级布局单元的解集以及所述其它级布局单元的解集,确定所述目标待插入位置的解集,所述目标待插入位置的解集包括:所述最后一级布局单元的解集以及所述其它级布局单元的解集。

44、在一可选的实施方式中,所述确定模块,具体用于:

45、根据所述多种布局方案,以及所述前一位置的解集中的每个解,确定所述每个待插入位置的正相位解集和负相位解集。

46、在一可选的实施方式中,所述确定模块,具体用于:

47、根据所述预设筛选条件,分别对所述前一位置的正相位解集中的每个解和负相位解集中的每个解进行筛选,得到所述前一位置的筛选后的正相位解集和筛选后的负相位解集;

48、根据所述多种布局方案、所述筛选后的正相位解集中的每个解以及所述筛选后的负相位解集中的每个解,确定所述每个待插入位置的正相位解集和负相位解集。

49、在一可选的实施方式中,所述确定模块,具体用于:

50、根据所述最后一个待插入位置的解集,确定所述待优化驱动门的扇出端的解集,所述扇出端的解集包括:所述扇出端的正相位解集;

51、获取在所述扇出端的正相位解集中每个解下所述待优化驱动门的延迟;

52、根据所述扇出端的正相位解集、所述待优化驱动门的电容以及所述待优化驱动门的延迟,确定所述待优化驱动门的扇入端的解集。

53、在一可选的实施方式中,所述确定模块,具体用于:

54、获取所述扇出端对应的导线延迟;

55、根据所述扇出端的正相位解集、所述待优化驱动门的电容、所述待优化驱动门的延迟以及所述每个解对应的导线延迟,确定所述待优化驱动门的解集。

56、在一可选的实施方式中,所述确定模块,具体用于:

57、获取所述每个待插入位置对应的导线延迟;

58、根据所述每个待插入位置的多种布局方案、所述预设解传播方向上所述每个待插入位置的前一位置的解,以及所述每个待插入位置对应的导线延迟,确定所述每个待插入位置的解集。

59、第三方面,本技术实施例还提供了一种电子设备,包括:处理器、存储器和总线,所述存储器存储有所述处理器可执行的机器可读指令,当电子设备运行时,所述处理器与所述存储器之间通过总线通信,所述处理器执行所述机器可读指令,以执行第一方面任一项所述的缓冲器和反相器的布局方法。

60、第四方面,本技术实施例还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器运行时执行第一方面任一项所述的缓冲器和反相器的布局方法。

61、本技术提供了一种缓冲器和反相器的布局方法、装置和电子设备,其中,该方法包括:获取待优化驱动门对应的每个负载门的解,根据每个负载门的解,沿着预设解传播方向,依次确定多个待插入位置的解集,根据预设解传播方向上最后一个待插入位置的解集,确定待优化驱动门的解集,从待优化驱动门的解集中确定满足预设筛选条件的目标解,根据目标解以及多个待插入位置的解集,分别确定多个待插入位置的目标布局方案,以采用目标布局方案在多个待插入位置进行缓冲器或反相器或导线的布局。本方案通过在待插入位置进行缓冲器或者反相器的布局,进一步提高了电路延迟优化效果。

- 还没有人留言评论。精彩留言会获得点赞!