一种数据预取方法、数据预取模块及预取器与流程

本发明涉及芯片,尤其涉及一种数据预取方法、数据预取模块及预取器。

背景技术:

1、预取技术通过所处的缓存层次的不同,可以分为l1缓存预取技术、l2缓存预取技术以及l3缓存预取技术等,而l1、l2和l3分别对应于一级缓存、二级缓存和三级缓存。一级缓存的预取功能,是每家cpu公司产品都具有的功,但是每家的预取算法、实现方式、功能配置,都不相同,通过采用跑分测试、仿真验证、性能分析等手段,以及大量的实验测试,选择出一种适合自己的产品的预取实现方式和算法。

2、目前,随着芯片技术的发展,现有的预取技术逐渐落后,无法高效的实现数据的预取,以及无法提供更好的预取数据范围,预取数据的命中率低,从而增加向内存或l3缓存拿数据的延迟,无法达到更快速高效完成数据读取的目的。

3、因此,目前亟需一种能够提高预取数据命中率、减少数据延迟、快速高效地实现数据读取的方法。

技术实现思路

1、本发明提供了一种数据预取方法、数据预取模块及预取器,以解决现有技术中预取数据命中率低、数据延迟高、无法快速高效地实现数据读取的技术问题。

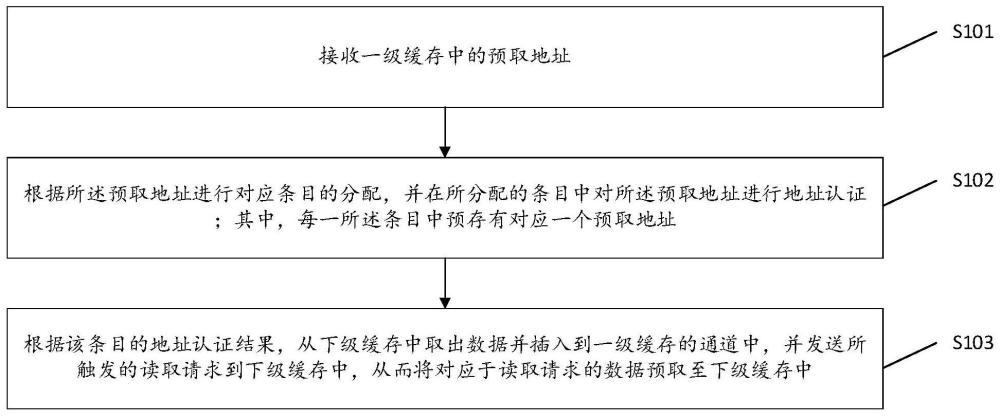

2、为了解决上述技术问题,本发明实施例提供了一种数据预取方法,用于预取器,包括:

3、接收一级缓存中的预取地址;

4、根据所述预取地址进行对应条目的分配,并在所分配的条目中对所述预取地址进行地址认证;其中,每一所述条目中预存有对应一个预取地址;

5、根据该条目的地址认证结果,从下级缓存中取出数据并插入到一级缓存的通道中,并发送所触发的读取请求到下级缓存中,从而将对应于读取请求的数据预取至下级缓存中。

6、作为优选方案,还包括:

7、当所述预取地址在所有条目中均不存在时,则将该预取地址作为初始预取地址,并对所述初始预取地址进行更新,并为更新后的预取地址分配一个空闲的条目,以使得对该条目进行初始化操作;

8、响应于指令流中出现与该条目中的当前预取地址相匹配的访问,将该条目中的当前预取地址更新为下一个预取地址,并触发更新后的预取地址之后预设个数的预取地址的读取请求,以使得将该读取请求对应的数据读回三级缓存中,进而将更新后的预取地址或其之后对应的数据放进一级缓存和二级缓存中;其中,所述下级缓存包括二级缓存和三级缓存。

9、作为优选方案,所述对所述初始预取地址进行更新,并对更新后的预取地址分配一个空闲的条目,以使得对该条目进行初始化操作,具体为:

10、将所述初始预取地址更新为下一个预取地址,从而对更新后的预取地址分配一个空闲的条目,以使得把更新后的预取地址的读取请求对应的数据读回至三级缓存中。

11、相应地,本发明还提供一种数据预取模块,设置于预取器中,包括:地址获取子模块、地址认证子模块和预取子模块;

12、所述地址获取子模块,用于接收一级缓存中的预取地址;

13、所述地址认证子模块,用于根据所述预取地址进行对应条目的分配,并在所分配的条目中对所述预取地址进行地址认证;其中,每一所述条目中预存有对应一个预取地址;

14、所述预取子模块,用于根据该条目的地址认证结果,从下级缓存中取出数据并插入到一级缓存的通道中,并发送所触发的读取请求到下级缓存中,从而将对应于读取请求的数据预取至下级缓存中。

15、作为优选方案,所述地址认证子模块,还用于:根据所述预取地址进行对应条目的分配,并在所分配的条目中对所述预取地址进行地址认证;其中,每一所述条目中预存有对应一个预取地址;

16、所述预取子模块,还用于:响应于指令流中出现与该条目中的当前预取地址相匹配的访问,将该条目中的当前预取地址更新为下一个预取地址,并触发更新后的预取地址之后预设个数的预取地址的读取请求,以使得将该读取请求对应的数据读回三级缓存中,进而将更新后的预取地址或其之后对应的数据放进一级缓存和二级缓存中;其中,所述下级缓存包括二级缓存和三级缓存。

17、作为优选方案,所述对所述初始预取地址进行更新,并对更新后的预取地址分配一个空闲的条目,以使得对该条目进行初始化操作,具体为:

18、将所述初始预取地址更新为下一个预取地址,从而对更新后的预取地址分配一个空闲的条目,以使得把更新后的预取地址的读取请求对应的数据读回至三级缓存中。

19、作为优选方案,所述触发更新后的预取地址之后预设个数的预取地址的读取请求,具体包括:

20、触发更新后的预取地址及其之后三个预取地址的读取请求;其中,所述预设个数包括3,更新后的预取地址为n,之后三个预取地址包括:n+1、n+2和n+3,n为自然数。

21、作为优选方案,所述触发更新后的预取地址之后预设个数的预取地址的读取请求,具体还包括:

22、根据前一次触发的读取请求,触发前一次读取请求中最后一个预取地址之后预设个数的预取地址对应的读取请求;其中,所述预设个数为一个或多个。

23、作为优选方案,所述将更新后的预取地址或其之后对应的数据放进一级缓存和二级缓存中,具体还包括:

24、将更新后的预取地址及其下一个的预取地址对应的数据放进一级缓存和二级缓存中;其中,更新后的预取地址为n,更新后的预取地址的下一个的预取地址为n+1。

25、作为优选方案,所述触发更新后的预取地址之后预设个数的预取地址的读取请求,以使得将该读取请求对应的数据读回三级缓存中,将更新后的预取地址或其之后对应的数据放进一级缓存和二级缓存中,具体还包括:

26、根据前一次触发的读取请求,触发前一次读取请求中的最后一个预取地址之后一个预取地址对应的读取请求,以使得将该读取请求对应的数据读回三级缓存中,并将更新后的预取地址之后的第二个预取地址对应的数据放进一级缓存和二级缓存中,从而数据预取达到稳定态。

27、作为优选方案,在所述响应于指令流中出现与该条目中的当前预取地址相匹配的访问之后,还包括:

28、获取与当前预取地址相匹配的条目;其中,条目的数量为若干个,每一个条目均有一个编号;

29、将编号最低的条目用于执行预取地址匹配、更新和数据预取,并取消其他重复匹配的条目。

30、相应地,本发明还提供一种预取器,包括如上任意一项所述的数据预取模块、处理器、存储器以及存储在所述存储器中且被配置为由所述处理器执行的计算机程序,所述处理器执行所述计算机程序时实现如上任意一项所述的数据预取方法。

31、相比于现有技术,本发明实施例具有如下有益效果:

32、本发明的技术方案通过接收一级缓存中的预取地址,进而对预取地址进行条目分配,从而在所分配的条目中进行预取地址的地址认证,能够确保预取地址认证过后从下级缓存中取出数据至一级缓存的通道之中,并且发送所触发的读取请求到下级缓存,以使得下级缓存能够高效的实现数据的预取,使得一级缓存在读到对应地址时能够直接从下级缓存中读取到数据,减少了向内存或缓存拿数据的延迟,同时通过条目对地址的认证也能够提供更好的数据预取范围,提高了数据的命中率。

33、进一步地,通过接收初始预取地址,进而对初始预取地址进行空闲条目的分配,进而对该条目进行初始化操作,从而更新该条目的预取地址,降低边界效应,减小尾部读取地址数量,并在后续响应于指令流中出现与该条目中的当前预取地址相匹配的访问,依次更新预取地址,并将预取地址之后对应的读取请求对应的数据读回三级缓存,提前实现对三级缓存的数据的读取,进而减少二级缓存或一级缓存向内存或三级缓存拉取数据的延迟,并将更新后的预取地址或其之后对应的数据放进一级缓存和二级缓存,提高了预取数据的命中率,从而实现更加快速且高效地完成一级缓存数据预取以及数据读取的目的。

- 还没有人留言评论。精彩留言会获得点赞!