长短程记忆神经网络控制电路及方法

本技术涉及神经网络,特别涉及一种长短程记忆神经网络控制电路及方法。

背景技术:

1、随着各种网络架构及算法的涌现,人工神经网络在当前的信息处理中展现出了令人瞩目的成就。由于传统的存储和计算分离的信息处理硬件平台与具有并行处理数据功能的人工神经网络不能很好的兼容,truenoth、loihi、tianjic等人工神经网络专用加速芯片以及tpu(tensor processing unit,张量处理单元芯片)、gpu(graphics processingunit,图形处理器)等运行平台也应运而生,进一步促进了人工神经网络的应用和发展。

2、长短程记忆(long short term memory,简称lstm)人工神经网络是一种专门处理时序信息的网络模型。由于当前输入数据需要跟前一时刻的处理结果进行交互计算,长短程记忆人工神经网络在目前通用平台上运行,数据的反复缓存、读出和叠加所产生的延迟和功耗也急剧增加。

3、因此,目前针对上述处理复杂信息神经网络设计专用的硬件电路和运行平台显得颇为亟需。

技术实现思路

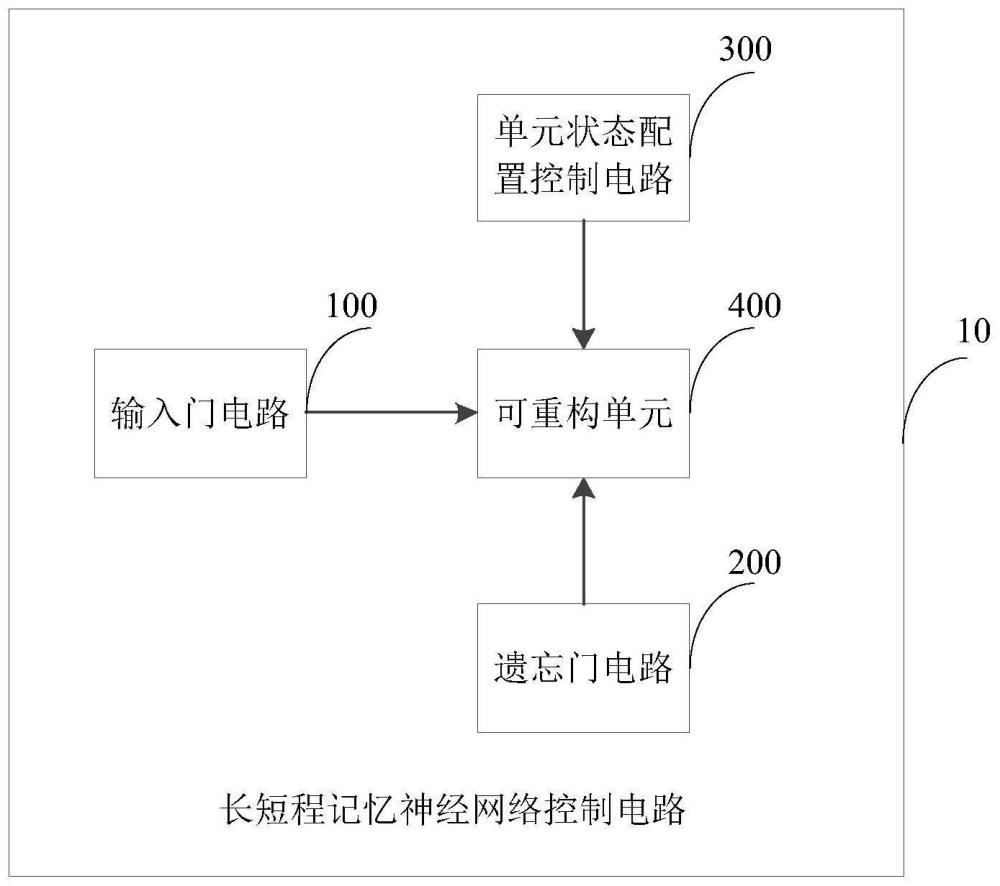

1、本技术提供一种长短程记忆神经网络控制电路及方法,以解决当前通用硬件平台运行长短程人工神经网络延时大、功耗高等问题,提出一种单元状态可调节和可重构配置的长短程记忆神经网络硬件电路架构,有效地加速信息的处理速度并降低系统功耗。

2、本技术第一方面实施例提供一种长短程记忆神经网络控制电路,包括:输入门电路、遗忘门电路、单元状态配置控制电路和可重构单元,其中,

3、所述输入门电路用于利用输入门忆阻器阵列对编码后的至少一个输入信号进行处理后输出第一电流信号至所述可重构单元,以通过所述可重构单元将所述第一电流信号转换成第一电压信号;

4、所述遗忘门电路用于在闭合所述遗忘门电路与所述可重构单元之间的第一开关闭合后,利用遗忘门忆阻器阵列对所述至少一个输入信号进行处理后输出第二电流信号,并利用电流-电压转换电路将所述第二电流信号转换成第二电压信号后加载到晶体管,以通过调节流过所述晶体管的电流对所述可重构单元的电容进行放电;

5、所述单元状态配置控制电路用于根据当前任务需求确定所述可重构单元模块的重构参数;以及

6、所述可重构单元用于基于所述当前任务需求,根据所述第一电压信号和所述重构参数进行重构后得到当前时刻输出参数和当前时刻单元状态参数。

7、可选地,在一些实施例中,所述遗忘门电路,包括:所述第一开关、所述遗忘门忆阻器阵列、第一运算放大器和所述晶体管,其中,

8、所述遗忘门忆阻器阵列由多个遗忘门忆阻器并联得到,所述遗忘门忆阻器阵列的输入端用于输入所述至少一个输入信号,所述遗忘门忆阻器阵列的输出端与所述第一运算放大器的同相输入端相连;

9、所述第一运算放大器的反相输入端与第一电源相连,其中,所述第一电源用于提供第一参考电压,所述第一运算放大器的输出端与所述晶体管的基极相连;

10、所述晶体管的发射极接地,所述晶体管的集电极通过所述第一开关与所述可重构单元相连。

11、可选地,在一些实施例中,所述单元状态配置控制电路,包括:配置忆阻器阵列和第二运算放大器,其中,

12、所述配置忆阻器阵列由多个配置忆阻器并联得到,所述配置忆阻器阵列的输入端用于输入所述至少一个输入信号,所述配置忆阻器阵列的输出端与所述第二运算放大器的同相输入端相连;

13、所述第二运算放大器反相输入端与第二电源相连,其中,所述第二电源用于提供第二参考电压,所述第二运算放大器的输出端与所述可重构单元相连。

14、可选地,在一些实施例中,所述可重构单元,包括:

15、由多个电容并列得到的电容阵列;

16、由多个开关并联得到的开关电路;

17、第三运算放大器,所述第三运算放大器的同相输入端分别与所述电容阵列的一端和所述输入门电路的输出端相连,所述第三运算放大器的反相输入端与第三电源相连,所述第三运算放大器的输出端和所述开关电路的一端相连后作为所述可重构单元的输出端;

18、其中,所述第三电源用于提供第三参考电压。

19、可选地,在一些实施例中,所述电容阵列的电容与所述开关电路的开关一一对应连接。

20、可选地,在一些实施例中,所述输入门忆阻器阵列由多个并联的输入门忆阻器,所述输入门忆阻器阵列用于输入所述编码后的至少一个输入信号。

21、可选地,在一些实施例中,所述可重构单元还用于存储所述当前时刻输出参数和所述当前时刻状态参数。

22、可选地,在一些实施例中,输入信号包括当前时刻输入参数、上一时刻的输出参数和上一时刻可重构单元的状态参数中的至少一种。

23、本技术第二方面实施例提供一种长短程记忆神经网络控制方法,采用如上任一项实施例所述的长短程记忆神经网络控制电路,其中,所述方法包括以下步骤:

24、通过所述输入门电路利用输入门忆阻器阵列对编码后的至少一个输入信号进行处理后输出第一电流信号至所述可重构单元,以通过所述可重构单元将所述第一电流信号转换成第一电压信号;

25、在闭合所述遗忘门电路与所述可重构单元之间的第一开关闭合后,利用遗忘门忆阻器阵列对所述至少一个输入信号进行处理后输出第二电流信号,并利用电流-电压转换电路将所述第二电流信号转换成第二电压信号后加载到晶体管,以通过调节流过所述晶体管的电流对所述可重构单元的电容进行放电;

26、通过所述单元状态配置控制电路根据当前任务需求确定所述可重构单元模块的重构参数;

27、通过所述可重构单元基于所述当前任务需求,根据所述第一电压信号和所述重构参数进行重构后得到当前时刻输出参数和当前时刻单元状态参数。

28、可选地,在一些实施例中,在基于所述当前任务需求,根据所述第一电压信号、第三电压信号和所述重构参数进行重构后得到当前时刻输出参数和当前时刻单元状态参数之后,还包括:存储所述当前时刻输出参数和所述当前时刻状态参数。

29、由此,本技术可以利用输入门电路的忆阻器阵列对编码后的输入信号进行处理后输出第一电流信号至可重构单元,可重构单元将第一电流信号转换成第一电压信号,在遗忘门电路与可重构单元之间的第一开关闭合后,通过遗忘门电路的忆阻器阵列对输入信号进行处理后输出第二电流信号,并利用电流-电压转换电路将第二电流信号转换成第二电压信号后加载到晶体管,以通过调节流过所述晶体管的电流对所述可重构单元的电容进行放电,通过单元状态配置控制电路根据当前任务需求确定可重构单元模块的重构参数,通过可重构单元基于当前任务需求,根据第一电压信号和重构参数进行重构后得到当前时刻输出参数和当前时刻单元状态参数。由此,解决了当前通用硬件平台运行长短程人工神经网络延时大、功耗高等问题,提出一种单元状态可调节和可重构配置的长短程记忆神经网络硬件电路架构,有效地加速信息的处理速度并降低系统功耗。

30、本技术附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!