时钟切换电路、实时时钟芯片和电子设备的制作方法

本发明涉及时钟切换,尤其涉及一种时钟切换电路、实时时钟芯片和电子设备。

背景技术:

1、随着芯片设计的复杂度以及芯片的低功耗要求的日益增加,芯片内部的时钟日益复杂,芯片中存在多个用于驱动芯片的时钟源的设计已经成为必然。芯片工作过程中大部分会涉及时钟的切换,由于时钟是芯片的核心部分,时钟稳定才能保证芯片稳定,因此时钟切换需要保证没有毛刺的。

2、在现有技术中的无毛刺时钟切换电路虽然实现了消除毛刺的功能,但是对时钟频率差距较大的时钟进行时钟切换的时间较长。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种时钟切换电路、实时时钟芯片和电子设备,能够加快时钟切换的速度。

2、本发明实施例采用的技术方案如下:

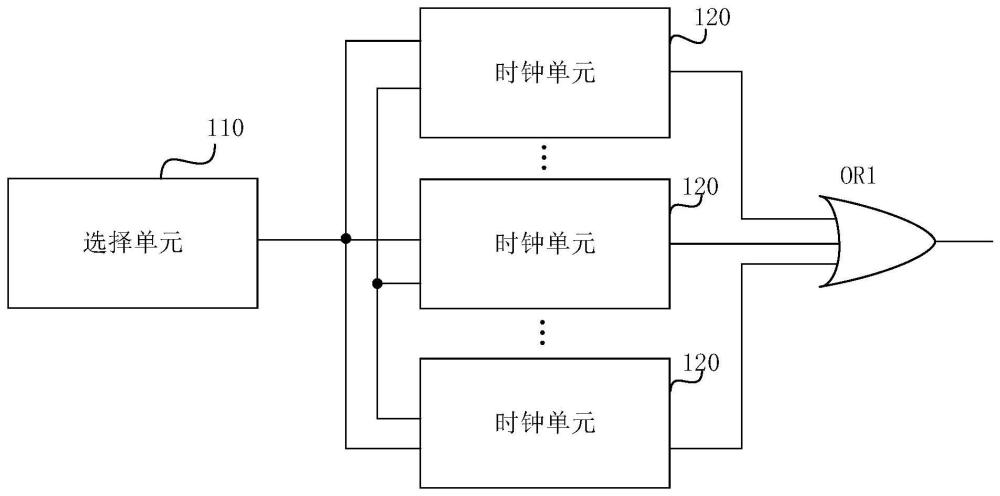

3、第一方面,本发明提供一种时钟切换电路,所述时钟切换电路包括选择单元、多个时钟单元以及第一或门,所述选择单元与多个所述时钟单元均电连接,所述第一或门与多个所述时钟单元均电连接,各所述时钟单元相互电连接;多个所述时钟单元中包括至少一个第一时钟单元,不同的所述第一时钟单元对应接收不同的第一时钟以及所述第一时钟对应的源时钟,所述第一时钟由所述源时钟分频得到;

4、所述选择单元用于选取多个所述时钟单元中的其中一个作为目标时钟单元;

5、每个所述时钟单元用于接收其他时钟单元输出的反馈信号;所述反馈信号表征对应的时钟单元是否停止输出时钟;

6、所述第一时钟单元用于在被选取为所述目标时钟单元且接收到的各所述反馈信号表征其他时钟单元已停止输出时钟的情况下,在所述源时钟的控制下输出所述第一时钟;

7、所述第一或门用于输出所述目标时钟单元输出的时钟。

8、在可选的实施方式中,多个所述时钟单元中还包括至少一个第二时钟单元,不同的所述第二时钟单元对应接收不同的第二时钟;

9、所述第二时钟单元用于在被选取为所述目标时钟单元且接收到的各所述反馈信号表征其他时钟单元已停止输出时钟的情况下,在所述第二时钟的控制下输出所述第二时钟。

10、在可选的实施方式中,每个所述时钟单元包括第一与门、第二与门、第三与门、第一触发器以及第二触发器;所述选择单元以及其他时钟单元的第二与门的输出端分别与所述第一与门的不同输入端电连接,所述第一与门的输出端与所述第一触发器的数据输入端电连接;

11、所述第一触发器的第一输出端与所述第二触发器的数据输入端电连接,所述第一触发器的第二输出端与所述第二与门的第一输入端电连接,所述第二触发器的第二输出端与所述第二与门的第二输入端电连接,所述第二与门的输出端与其他时钟单元的第一与门的输入端均电连接,所述第二与门的输出端用于输出所述反馈信号;所述第二触发器的第一输出端与所述第三与门的第一输入端电连接,所述第一或门的多个输入端与多个所述时钟单元的第三与门的输出端一一对应电连接;所述第一触发器的第一输出端和第二输出端输出的信号反相,所述第二触发器的第一输出端和第二输出端输出的信号反相;

12、在所述时钟单元为所述第一时钟单元的情况下,所述时钟单元的第一触发器的时钟输入端和第二触发器的时钟输入端均用于接收所述源时钟,所述时钟单元的第三与门的第二输入端用于接收所述第一时钟;

13、在所述时钟单元为所述第二时钟单元的情况下,所述时钟单元的第一触发器的时钟输入端、第二触发器的时钟输入端以及第三与门的第二输入端均用于接收所述第二时钟。

14、在可选的实施方式中,每个所述时钟单元还包括第一非门、第二或门以及第四与门,所述第一非门的输入端与所述第三与门的第二输入端电连接,所述第一非门的输出端与所述第二或门的第一输入端电连接,所述第二或门的第二输入端与所述第二触发器的第一输出端电连接,所述第二或门的输出端与所述第四与门的第一输入端电连接,所述第四与门的第二输入端与所述第一触发器的第一输出端电连接,所述第四与门的输出端与所述第二触发器的数据输入端电连接。

15、在可选的实施方式中,所述选择单元用于根据接收的选择信号所对应的数值选取多个所述时钟单元中的其中一个作为目标时钟单元;其中,不同时钟单元对应不同编号,所述选择信号所对应的数值为所述目标时钟单元的编号,所述选择信号的位宽根据所述时钟单元的个数设置。

16、在可选的实施方式中,在所述时钟单元为2个的情况下,所述选择单元包括第二非门,所述第二非门的输入端与其中一个所述时钟单元电连接,所述第二非门的输出端与另一个所述时钟单元电连接;所述第二非门的输入端用于接收所述选择信号。

17、在可选的实施方式中,在所述时钟单元大于2个的情况下,所述选择单元包括多个选择子单元,多个所述选择子单元与多个所述时钟单元一一对应电连接;

18、每个所述选择子单元用于接收所述选择信号,并根据所述选择信号输出对应的选择结果信号;所述选择结果信号为第一选择结果信号或第二选择结果信号,其中,所述第一选择结果信号表征所述选择信号对应的数值与所述选择子单元对应的时钟单元的编号一致;所述第二选择结果信号表征所述选择信号对应的数值与所述选择子单元对应的时钟单元的编号不一致。

19、在可选的实施方式中,在所述时钟单元为3个的情况下,多个所述选择子单元包括第一选择子单元、第二选择子单元以及第三选择子单元;所述第一选择子单元包括第五与门、第三非门以及第四非门,所述第二选择子单元包括第六与门以及第五非门,所述第三选择子单元包括第七与门以及第六非门;

20、所述第五与门的第一输入端与所述第三非门的输出端电连接,所述第五与门的第二输入端与所述第四非门的输出端电连接,所述第五与门的输出端与对应的所述时钟单元电连接;所述第三非门和所述第四非门的输入端共同用于接收所述选择信号;

21、所述第六与门的第一输入端与所述第五非门的输出端电连接,所述第六与门的输出端与对应的所述时钟单元电连接;所述第五非门的输入端和所述第六与门的第二输入端共同用于接收所述选择信号;

22、所述第七与门的第二输入端与所述第六非门的输出端电连接,所述第七与门的输出端与对应的所述时钟单元电连接;所述第六非门的输入端与所述第七与门的第一输入端共同用于接收所述选择信号。

23、第二方面,本发明提供一种实时时钟芯片,包括前述实施方式任一项所述的时钟切换电路。

24、第三方面,本发明提供一种电子设备,包括主控芯片和前述实施方式所述的实时时钟芯片,所述实时时钟芯片与所述主控芯片电连接。

25、本发明实施例提供的时钟切换电路、实时时钟芯片和电子设备,时钟切换电路包括:选择单元、多个时钟单元以及第一或门,选择单元与多个时钟单元均电连接,第一或门与多个时钟单元均电连接,各时钟单元相互电连接,选择单元用于选取多个时钟单元中的其中一个作为目标时钟单元,每个时钟单元用于接收其他时钟单元输出的反馈信号,第一时钟单元用于在被选取为目标时钟单元且接收到的各反馈信号表征其他时钟单元已停止输出时钟的情况下,在源时钟的控制下输出第一时钟,第一或门用于输出目标时钟单元输出的时钟。由于第一时钟由源时钟分频得到,源时钟相对于第一时钟为高频率的时钟,故通过源时钟控制时钟切换,可以加快时钟切换的速度。

26、为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

- 还没有人留言评论。精彩留言会获得点赞!