一种数据传输系统及延迟值自动获取方法与流程

本技术涉及通信,特别是涉及一种数据传输系统及延迟值自动获取方法。

背景技术:

1、在串行同步通信的场景下,通信总线的时钟线相对于数据线存在延迟,以上升沿采集为例:在上升沿采集中包括有建立时间(tsu)和保持时间(thd),如图1所示,图1中clk1为时钟信号,d1为数据信号,bit0为实际传输的数据,其中:

2、tsu为:时钟上升沿到来之前,输入端的数据已经到来并稳定持续的时间间隔;

3、thd为:时钟上升沿到来之后,输入端的数据继续保持稳定并持续的时间间隔。

4、简单来说,建立时间表示“预先准备”,保持时间表示“事后不变”。

5、在接收端,当数据在时钟上升沿到来之前和之后的一段时间内都能保持稳定,则认为该数据在当前上升沿能被正确采集到。数据接收端时钟上升沿位置相对于数据中心点位置的延迟就是通信接口中时钟线相对于数据线的延迟,称之为clkdelay,clkdelay值会影响到接收端采集数据的准确性,如果上升沿位置与被采集数据中心点位置偏差过大,则可能采集到的错误的数据。

6、现有技术在设备出厂前测试一个clkdelay值,并将测试好的clkdelay值设定为该设备的唯一的且不可调整的clkdelay值,而在设备出厂后如果设备线路发生改变,设备出厂前设定的clkdelay值有可能是不合理的,若继续以这个clkdelay值作为所有主板的最终值是是会造成数据传输错误的。

7、因此,如何确定clkdelay值成为亟需解决的问题。

技术实现思路

1、本技术实施例的目的在于提供一种数据传输系统及延迟值自动获取方法,以实现在使用设备时,自动确定时钟线相对于数据线的延迟值。具体技术方案如下:

2、第一方面,本技术实施例提供了一种数据传输系统,所述系统包括:

3、ad芯片,soc芯片,数据通信总线;所述ad芯片包括延迟锁相环模块;所述ad芯片包括至少一个接口,针对每一个接口对应一个数据通信总线;其中,所述数据通信总线包括时钟线和数据线,所述ad芯片通过所述接口及所述数据通信总线与所述soc芯片进行通信连接;

4、所述ad芯片用于:针对待测试接口,从预设延迟区间选择一个延迟值,作为所述待测试接口的第一延迟值,所述第一延迟值表示时钟线相对于所述数据线的通信延迟;

5、所述ad芯片用于通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,利用所述延迟锁相环模块基于所述第一延迟值生成时钟信号,通过所述时钟线发送所述时钟信号至所述soc芯片;

6、所述soc芯片用于基于接收到的时钟信号接收所述ad芯片发送的第一测试数据,得到第二测试数据,并通过所述数据线将所述第二测试数据经由所述待测试接口返回给所述ad芯片,通过所述时钟线发送所述时钟信号至所述ad芯片;

7、所述ad芯片用于基于接收到的时钟信号接收所述soc芯片返回的第二测试数据,得到第三测试数据,并将所述第三测试数据与所述第一测试数据进行比对,在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值,在所述第三测试数据与所述第一测试数据不相同的情况下,确定所述第一延迟值不是所述待测试接口的目标延迟值。

8、在一种可能的实施方式中,所述ad芯片还用于:

9、在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值的步骤之后,从所述预设延迟区间选择另一个延迟值,作为所述待测试接口的第一延迟值,并返回步骤所述ad芯片通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,通过所述时钟线发送时钟信号至所述soc芯片继续执行,直至遍历完所述预设延迟区间,得到一个或多个所述目标延迟值;

10、所述ad芯片基于预设第一规则从多个所述目标延迟值确定最优目标延迟值,将所述最优目标延迟值作为所述待测试接口的时钟线相对于数据线的目标延迟值,以使所述ad芯片基于所述目标延迟值通过所述待测试接口发送待发送数据。

11、在一种可能的实施方式中,所述ad芯片具体用于:

12、将多个所述目标延迟值的中位数作为最优目标延迟值。

13、在一种可能的实施方式中,在所述ad芯片上电启动,且未通过所述数据线发送第一测试数据至所述soc芯片之前,所述ad芯片用于从预设延迟区间选择一个延迟值,作为所述待测试接口的第一延迟值。

14、在一种可能的实施方式中,在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值之后;

15、所述ad芯片还用于:从所述预设延迟区间选择另一个延迟值,作为所述待测试接口的第一延迟值,并返回步骤所述ad芯片通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,通过所述时钟线发送时钟信号至所述soc芯片继续执行,直至遍历完所述预设延迟区间,得到一组目标延迟值;

16、重复执行上述遍历过程,得到预设数量组目标延迟值;

17、所述ad芯片基于预设第二规则从所述预设数量组目标延迟值中确定最优目标延迟值,将所述最优目标延迟值作为所述时钟线相对于所述数据线的目标延迟值,以使所述ad芯片基于所述目标延迟值通过所述待测试接口发送待发送数据。

18、在一种可能的实施方式中,所述ad芯片具体用于:

19、对所述预设数量组目标延迟值取交集;

20、从所述交集中选择一个目标延迟值作为最优目标延迟值。

21、在一种可能的实施方式中,所述ad芯片包括至少一个高清信号接口,至少1个超高清信号接口。

22、第二方面,本技术实施例提供了一种延迟值自动获取方法,应用于数据传输系统,所述数据传输系统包括ad芯片,soc芯片,数据通信总线,所述ad芯片包括至少一个接口,针对每一个接口对应一个数据通信总线;其中,所述数据通信总线包括时钟线和数据线,所述ad芯片通过所述接口和所述soc芯片通过所述数据通信总线进行通信连接,所述ad芯片包括延迟锁相环模块;所述方法包括:

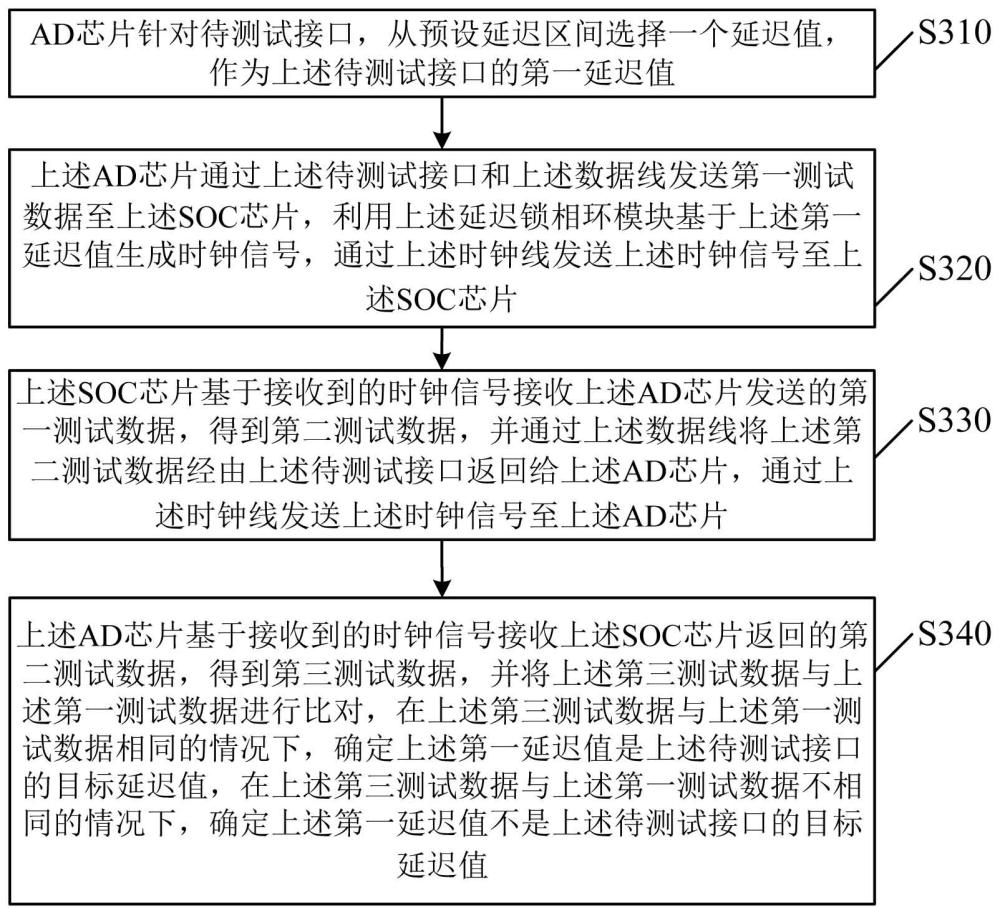

23、所述ad芯片针对待测试接口,从预设延迟区间选择一个延迟值,作为所述待测试接口的第一延迟值,所述第一延迟值表示时钟线相对于所述数据线的通信延迟;

24、所述ad芯片通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,利用所述延迟锁相环模块基于所述第一延迟值生成时钟信号,通过所述时钟线发送所述时钟信号至所述soc芯片;

25、所述soc芯片基于接收到的时钟信号接收所述ad芯片发送的第一测试数据,得到第二测试数据,并通过所述数据线将所述第二测试数据经由所述待测试接口返回给所述ad芯片,通过所述时钟线发送所述时钟信号至所述ad芯片;

26、所述ad芯片基于接收到的时钟信号接收所述soc芯片返回的第二测试数据,得到第三测试数据,并将所述第三测试数据与所述第一测试数据进行比对,在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值,在所述第三测试数据与所述第一测试数据不相同的情况下,确定所述第一延迟值不是所述待测试接口的目标延迟值。

27、在一种可能的实施方式中,所述方法还包括:

28、所述ad芯片在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值的步骤之后,从所述预设延迟区间选择另一个延迟值,作为所述待测试接口的第一延迟值,并返回步骤所述ad芯片通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,通过所述时钟线发送时钟信号至所述soc芯片继续执行,直至遍历完所述预设延迟区间,得到一个或多个所述目标延迟值;

29、所述ad芯片基于预设第一规则从多个所述目标延迟值确定最优目标延迟值,将所述最优目标延迟值作为所述待测试接口的时钟线相对于数据线的目标延迟值,以使所述ad芯片基于所述目标延迟值通过所述待测试接口发送待发送数据。

30、在一种可能的实施方式中,所述ad芯片基于预设第一规则从多个所述目标延迟值确定最优目标延迟值,包括:

31、将多个所述目标延迟值的中位数作为最优目标延迟值。

32、在一种可能的实施方式中,所述ad芯片针对待测试接口,从预设延迟区间选择一个延迟值,作为所述待测试接口的第一延迟值,包括:

33、所述ad芯片在所述ad芯片上电启动,且未通过所述数据线发送第一测试数据至所述soc芯片之前,从预设延迟区间选择一个延迟值,作为所述待测试接口的第一延迟值。

34、在一种可能的实施方式中,所述方法还包括:

35、所述ad芯片在所述第三测试数据与所述第一测试数据相同的情况下,确定所述第一延迟值是所述待测试接口的目标延迟值的步骤之后;

36、从所述预设延迟区间选择另一个延迟值,作为所述待测试接口的第一延迟值,并返回步骤所述ad芯片通过所述待测试接口和所述数据线发送第一测试数据至所述soc芯片,通过所述时钟线发送时钟信号至所述soc芯片继续执行,直至遍历完所述预设延迟区间,得到一组目标延迟值;

37、重复执行上述遍历过程,得到预设数量组目标延迟值;

38、所述ad芯片基于预设第二规则从所述预设数量组目标延迟值中确定最优目标延迟值,将所述最优目标延迟值作为所述时钟线相对于所述数据线的目标延迟值,以使所述ad芯片基于所述目标延迟值通过所述待测试接口发送待发送数据。

39、在一种可能的实施方式中,所述ad芯片基于预设第二规则从所述预设数量组目标延迟值中确定最优目标延迟值,包括:

40、对所述预设数量组目标延迟值取交集;

41、从所述交集中选择一个目标延迟值作为最优目标延迟值。

42、本技术实施例有益效果:

43、本技术实施例提供的一种延迟值自动获取方法及数据传输系统,针对待测试接口,ad芯片基于预设延迟区间确定时钟线相对于数据线的第一延迟值,然后ad芯片通过数据线发送第一测试数据至soc芯片,利用延迟锁相环模块基于第一延迟值生成时钟信号,通过时钟线发送时钟信号至soc芯片,soc芯片基于接收到的时钟信号接收ad芯片发送的第一测试数据,得到第二测试数据,并通过数据线将第二测试数据返回给ad芯片,ad芯片将接收到的测试数据与自身发出的第一测试数据进行比对,在两者相同的情况下,确定第一延迟值是目标延迟值,如此在使用ad芯片时,可以自动确定待测试接口的时钟线相对于数据线的延迟值,而且因为是设备自动进行测试得到的延迟值,不仅大大提高测试效率,省去人工测试的繁琐步骤,准确性更高。基于此目标延迟值可以抵消硬件走线等原因导致的时钟线与数据线之间的延迟,提高采集数据的准确性。

44、当然,实施本技术的任一产品或方法并不一定需要同时达到以上所述的所有优点。

- 还没有人留言评论。精彩留言会获得点赞!