一种基于标签缓存的标签式存储结构及方法

本发明涉及处理器芯片,更具体的说是涉及一种基于标签缓存的标签式存储结构及方法。

背景技术:

1、标签技术,指的是处理器架构中一种用于操作和管理内存中数据的辅助机制。这些标签用于标识内存中的数据,以确保数据被正确加载、存储和访问,同时也可以用于实现多任务处理、内存保护和安全性。其具体有如下用途,1.内存保护,处理器使用标签技术来确保不同的进程无法访问彼此的内存,从而保护数据的隐私和安全性。每个内存页可以带有访问权限标签,如只读、读写、执行等,以控制对数据的访问。当进程试图访问没有适当权限的内存区域时,处理器会触发异常,操作系统可以捕获并处理异常。2.硬件安全,一些处理器架构会使用标签技术来实现硬件安全性功能,如执行数据执行保护(data executionprevention,dep)和地址空间随机化(address space layout randomization,aslr)。dep使用标签技术分离内存区域,来防止执行内存中的恶意代码。aslr使用标签技术来随机化内存地址,使攻击者更难以利用已知的漏洞。在侧信道攻击领域,利用标签技术将访问授权信息存储在标记中,用于标记数据所处的安全域,cpu进行不同安全域的隔离,以便在存储器访问过程中验证程序是否具有访问权限并进行不同安全域的安全操作。

2、缓存技术,处理器的缓存技术是计算机体系结构中的重要组成部分,用于提高内存访问速度,减少处理器等待内存的时间。这些缓存通常是高速、容量较小的存储器,用于存储最常用的数据和指令。处理器通常包括多级缓存,如l1、l2、l3等,按照从最接近处理器核心到最远的顺序排列。l1缓存是最接近处理器核心的,速度最快但容量最小。l2和l3缓存则更大但相对较慢。缓存存储有限,因此需要一种策略来确定哪些数据被保留在缓存中。常见的替换策略包括最近最少使用(lru)、随机替换和先进先出(fifo)。lru是一种较为常见的策略,它选择最长时间没有被访问的数据进行替换。处理器缓存可以采用写回(write-back)或写直通(write-through)策略。写回策略只在缓存行替换时才写回主存,而写直通策略在写操作后立即将数据写回主存。写回策略可以减少内存写入操作,但需要处理脏数据(即已被修改但尚未写回主存的数据)。处理器的缓存技术是计算机体系结构中的关键设计元素,对于提高计算机性能至关重要。通过合理的缓存层次结构、替换策略、写策略和缓存一致性,处理器能够更有效地管理内存访问,提高程序执行速度。不同的处理器架构可能采用不同的缓存设计,以满足特定的性能需求。

3、标签式存储结构(tagged memory hierarchy),是一种计算机存储器结构,将标记与每个存储单元相关联。标记通常包含有关存储单元内容的元数据信息,例如存储单元所属的数据类型、访问授权、存储单元的地址范围等。一般而言,标签通常以额外的比特形式存储在存储单元中,与存储单元的一般数据一起存储和访问。

4、现有的标签存储方案有如下几种,以每32位的数据附加2位的标签为例:

5、①直接拓展存储器位宽,针对原先32位的存储器位宽拓展位34位,即在硬件结构上对存储器的位宽拓宽2位用于存储标签。这种方法直接且高效,硬件开销低且存取效率高,但也存在一定的问题,因其对存储器的硬件进行了修改,因此兼容性差,需要针对该系统专门设计新的存储器结构。

6、②借用存储器的部分空间,将存储器的部分空间留用存储标签,该方案需要对存储器按照一定的比例进行分割,其比值为数据与标签的位宽之比。该方案的优点是兼容现有的存储器结构,但存在如下两个问题,首先,大部分情况下数据与标签的比例需求无法做到使内存空间完美分割,因此会使内存产生一定的冗余,以每32位数据附加2位标签为例,其16:1的比例会使内存至多产生15个字节的冗余空间,冗余空间的大小仅与数据标签比例大小有关,而与内存的总大小无关,因此一个大容量内存中这种冗余所占比例较小,且在可以接受的范围之内。其次,由于数据和标签共用同一个存储区,其在访存的时候需要多次进行存取操作,一次读取需要分别读取数据与标签,即需要对主存进行两次完整的读操作。与此同时,标签的位数不足一个字节,为最大化利用内存空间,需要将多个标签打包对齐放入内存中,即一个地址空间内存在多个标签。在标签写入的过程中,为防止旧有标签被覆盖,需要将目标地址中的数据读出后修改再重新写入该地址空间内,因此执行一次写指令,需要对主存储器进行一次“写入、读取、写入”操作,如此将消耗大量的存取时间以及占用总线资源。

7、③添加一个标签专用存储区,在原有的存储器之外,于总线上挂载一个位宽为2的存储器,仅用于存储标签,其可以视为存储器的影子空间,与存储器共用同一组地址总线,但不共用数据总线。该方案的优点是存储效率比较高,但存在以下问题,其一,与方案一以类似,虽不需要对原先32位位宽的存储器做出改变,但需要额外挂载一个2位的存储器,其不能兼容现有的存储器结构。其二,两块存储器分别都需要有独立的接口电路以及控制逻辑,相较于方案一,平添了一笔额外的电路开销。

8、④分块存储不同标签的数据,根据不同的标签将存储器划分为多个区域,每个区域只存储对应标签的数据,以2位的标签为例,根据标签的值作为编号,将存储器划分为4个区域,每个区域只存储对应标签的数据。该方案的优点是兼容现有存储器结构,存取效率高,但由于无法对每个存储区的大小做出实时的修改,大部分情况下将无法做到写满每一个存储区,因此该方案的存储空间利用率较低,各存储区域维护成本及难度较大。

技术实现思路

1、有鉴于此,本发明提供了一种基于标签缓存的标签式存储结构及方法,对存在读写效率低(多次读写)的问题,通过在cpu总线与主存之间引入一个新的缓存tag cache,用相对较小的电路开销和较小的性能影响,极大地提升了读写效率。

2、为了实现上述目的,本发明采用如下技术方案:

3、一种基于标签缓存的标签式存储结构,包括:数据缓存、主存储器和标签缓存;所述多级缓存位于cpu与总线之间,所述标签缓存位于数据缓存和主存储器之间;

4、所述数据缓存用于对缓存运行中的数据部分拓展出标签位;

5、所述主存储器用于划分出数据存储与标签存储的两个区域。

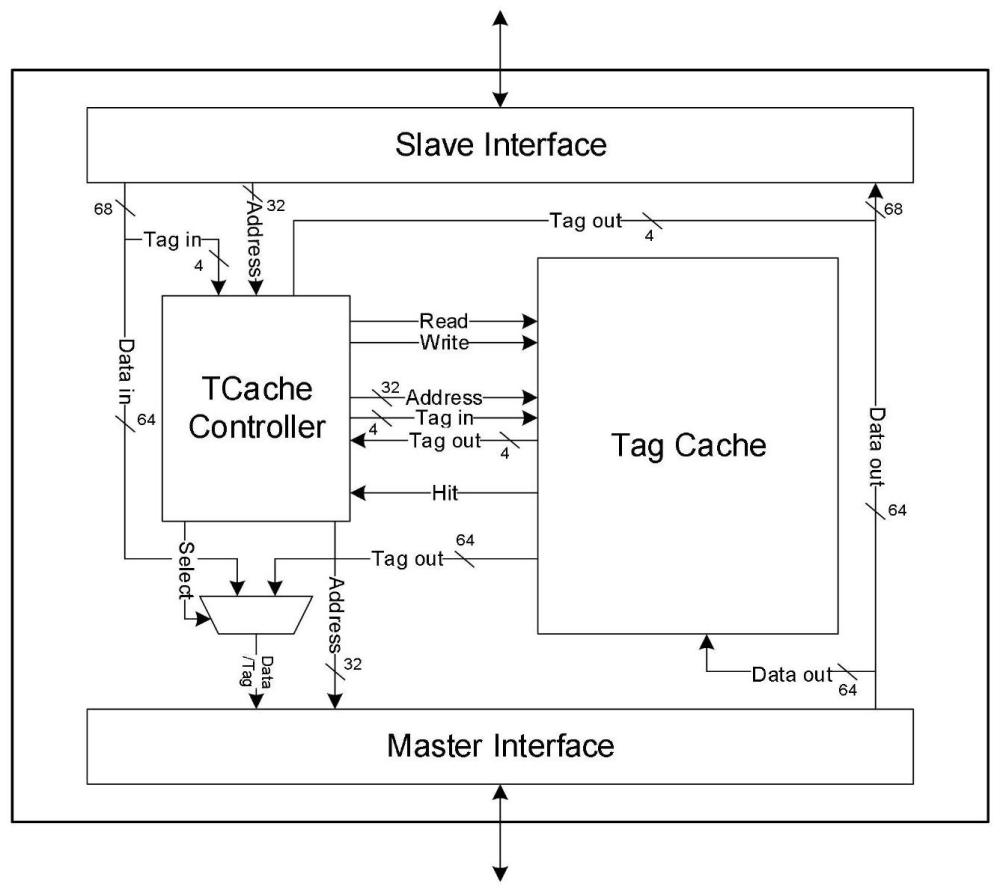

6、可选的,所述标签缓存用于存储标签,包括缓存控制器和tag cache;所述缓存控制器为逻辑控制区域,用于负责前级、后级以及tag cache的访问控制,根据前级发来的访问指令,以及tag cache的命中与否情况生成对后级和主存的访问指令及控制指令。

7、可选的,所述数据存储位于低地址空间,所述标签存储位于高地址空间。

8、可选的,所述标签缓存的前级缓存的数据总线位宽为数据位宽与标签位宽的加和,而后级的主存位宽为数据位宽。

9、可选的,所述主存储器与所述tag cache之间存在一个读写通道。

10、可选的,tag cache设置有实时监控模块,用于对自身的存储情况进行实时监控。

11、一种基于标签缓存的标签式存储方法,利用任意一项所述的一种基于标签缓存的标签式存储结构,包括以下步骤:

12、若前级请求地址命中,则生成标签请求附加前级请求对主存发出请求,获取响应并更新存储区域;

13、若前级请求地址未命中,则生成第一请求和第二请求,将第一请求转发给主存请求,第二请求交由tag cache响应。

14、可选的,tag cache的运行逻辑为:前级的数据进行存储时,其中数据直接交给主存,标签则交给tag cache存储,当tag cache即将溢出时,将存储区域与主存的总线访问挂起,将存储区域的标签数据写回至主存;当主存进行数据写入时,在tag cache缓存命中的前提下,数据同时写入tcache存储区域和主存。

15、经由上述的技术方案可知,与现有技术相比,本发明提供了一种基于标签缓存的标签式存储结构及方法,具有以下有益效果:

16、1、对比旧方案,本发明中的标签式存储结构利用缓存技术,减少了存储器的读写次数,提升了标签处理器-存储器系统的读写效率。

17、2、标签缓存的引入将不同数据位宽的系统进行了适配,更好地兼容现有系统总线和存储器。

- 还没有人留言评论。精彩留言会获得点赞!