一种软硬协同的访存单元EDAC实现方法

本发明主要涉及到微处理器微体系结构设计,特指一种软硬协同的访存单元edac实现方法。

背景技术:

1、随着半导体工艺尺寸的不断缩小,微处理器片上集成的晶体管密度不断增大,片上存储器容量越来越大,存储单元之间的距离不断减小,供电电压不断减少,更容易受到高能粒子撞击和外界环境干扰影响,出现单粒子翻转(single event upset, seu)现象,导致访存单元软错误出现的概率不断增加。片上访存单元的软错误将直接导致访存数据出错,已成为影响微处理器正常运行的主要问题。因此,对微处理器的访存单元进行可靠性设计加固十分必要。

2、由于大容量片上访存单元通常占据了很大比例微处理器面积,访存单元的可靠性加固设计通常采用edac编码技术(error detection and correction, edac)来保护片上存储免受seu的攻击。考虑edac编解码实现的硬件复杂性和延迟,汉明码、hsiao码、sec-ded码等线性分组码常用于片上访存的可靠性设计。支持edac的访存单元的延迟和面积开销是其电路结构设计的主要关注点,需要在不影响微处理器运行性能和满足可靠性要求前提下,尽可能减少访存单元的硬件实现面积,以减少微处理器的整体面积和功耗。

3、微处理器的访存单元通常需要支持多种数据访存粒度,以满足不同应用以及多核架构中不同粒度的数据交互。在控制成本开销的前提下,这增加了edac校验码对多种访存粒度数据进行统一edac保护的难度。对于常用于片上存储器保护的线性分组码来说,数据校验码的位数随被edac保护的数据粒度m(m为正整数)的增加按照o()趋势增长。对于同一数据容量v,其增加的存储校验码的冗余存储空间为:,即对同一数据容量,edac保护的访存粒度m越小,edac电路硬件开销越大。

4、在不关心edac开销的情况下,有从业者提出一种直观可行的对多粒度访存数据实现edac保护的方案为按照最小数据访存粒度进行edac编码,其他粒度的edac编码可通过复用多个最小粒度的edac编码模块实现。因此该方案实施的前提条件是需要所有访存粒度与最小访存粒度呈正整数倍数关系。但该方案主要存在两个问题:

5、1、存储效率低;存储edac校验码信息的冗余存储容量大。以8位作为最小数据访存粒度,128位为最大数据访存粒度为例。采用线性分组中的hsiao码,以8位数据为一组实现纠一检二编解码,即按hsiao码(13,8)实现edac,每8位数据需要额外增加5位edac校验码。用hsiao码(13,8)对128位数据编码需要额外增加80位edac校验码;而按hsiao码(137,128)实现edac,对每128位数据编码仅需额外增加9位edac校验码,即针对同一访存单元设计容量,按前者进行编解码,片上访存单元需要增加原存储容量的5/8用于存储edac校验码,较后者所增加的9/128,前者的冗余存储开销显著,访存单元存储效率低。

6、2、硬件开销大;编解码模块数量多。仍以8位作为最小数据访存粒度、128位为最大数据访存粒度为例,如果按最小数据粒度进行edac,为了满足最大数据粒度访存带宽,需要复用hsiao码(13,8)编解码模块各16个(128/8),而按最大数据访存粒度128位进行edac,只需要hsiao码(137,128)编解码模块各1个。虽然单个最小数据访存粒度的编解码模块硬件实现更简单,硬件开销更小,但相比于按较大数据粒度进行edac,编解码模块的数量大幅增加,edac的整体硬件开销增大。

7、另有从业者提出的自适应edac方案也是一种实现思路,即通过自适应调整edac编码长度实现对多粒度数据的容错。虽然自适应edac方案较上述以最小访存粒度编码edac方案,有效降低了硬件动态功耗,但自适应增加了硬件的控制逻辑开销,用以选择不同edac编解码模块。同时,硬件中的多套edac编解码模块也无法避免edac硬件面积开销大的难题。

技术实现思路

1、本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种原理简单、易实现、能够在降低开销的前提下提高片上存储器的可靠性的软硬协同的访存单元edac实现方法。

2、为解决上述技术问题,本发明采用以下技术方案:

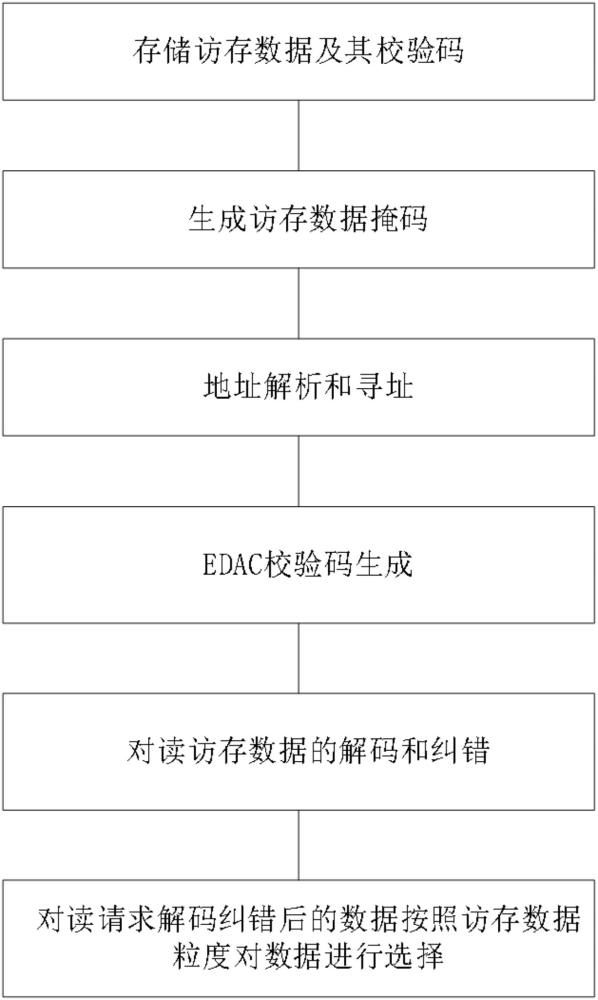

3、一种软硬协同的访存单元edac实现方法,包括:

4、存储访存数据及其校验码;

5、生成访存数据掩码:根据数据访存粒度生成访存数据掩码;

6、地址解析和寻址:对到达的读访存请求或写访存请求进行访存地址解析和寻址冗余存储器;

7、edac校验码生成:在写访存数据写入存储器前实现写数据的edac校验码生成;

8、对读访存数据的解码和纠错:在读访存操作时,根据读访存数据掩码对读请求按照粒度,从冗余存储器中读出数据,并按n位数据粒度对相应数据进行edac解码和纠错;

9、对读请求解码纠错后的数据按照访存数据粒度对数据进行选择。

10、作为本发明方法的进一步改进:在存储访存数据及其校验码过程中,按高位地址交叉或者低位地址交叉进行存储体组织以提高数据访问带宽和实现数据并行性操作,并按访存地址实现读、写访存寻址;访存操作时,访存请求、读写类型、访存地址、数据访存粒度会经由访存流水线进入edac电路中。

11、作为本发明方法的进一步改进:在生成访存数据掩码过程中,对于大访存粒度,每n位数据粒度对应1位掩码;对于小访存粒度,该小访存粒度数据所在的n粒度数据对应1位掩码。

12、作为本发明方法的进一步改进:所述访存数据掩码的每一位控制一组n粒度数据的启用或关闭,其中访存粒度不足n粒度的按1个n粒度算;写访存数据掩码所启用的位写选择位,控制粒度数据及其对应的编码后的k个校验码即位数据写入访存地址寻址的冗余存储器中;读访存数据掩码所启用的位读选择位,控制从冗余存储器中读取位读数据。

13、作为本发明方法的进一步改进:在edac校验码生成过程中,对写请求的写数据按照粒度n进行划分,并对每个n粒度数据进行edac编码,以生成每个n粒度数据对应的edac校验码check_bits以实现读访存时对读出数据的检错纠错保护;根据访存数据掩码选择k个n粒度写访存数据写入冗余存储器目标地址的同时,将生成的k个校验码写入冗余存储器对应地址。

14、作为本发明方法的进一步改进:在地址解析和寻址过程中,具体定位读、写访存请求操作的冗余存储器访问端口。

15、作为本发明方法的进一步改进:针对小粒度写数据采用宏定义技术,将小粒度写请求的小粒度数据拼接成所定义的n粒度数据、再进行edac编码;所述宏定义技术用来实现对小粒度写访存的重新封装。

16、作为本发明方法的进一步改进:针对稀疏小粒度写数据的处理流程包括:

17、步骤s1:将小粒度写请求对应地址中的n粒度数据a及其校验码从冗余存储体中读出,进行edac解码纠错后写入到通用寄存器中;该操作可通过一次读访存操作实现。其中硬件可实现地址自动对齐,不需要修改读请求的地址;

18、步骤s2:根据访存地址偏移和移位操作,将小粒度写数据b与n数据粒度对齐;

19、步骤s3:删去n粒度a中对应小粒度数据b位置中的旧小粒度数据,为小粒度b的写入做准备;

20、步骤s4:完成小粒度b数据与n粒度a数据的完整拼接,生成n粒度要写入的数据a’;

21、步骤s5:将拼接好的新的n粒度数据a’进行edac编码,并写入冗余存储体的相同地址空间内;该操作可通过一次写访存操作实现。

22、作为本发明方法的进一步改进: 所述步骤s1和步骤s5均通过一次写访存操作实现。

23、作为本发明方法的进一步改进:针对高密度的连续小粒度写数据的处理流程包括:

24、步骤s10:根据访存地址偏移和移位操作,对地址连续的p个小粒度写请求的写数据进行对齐操作;其中p为粒度n除以某小粒度大小;

25、步骤s20:利用或操作,将对齐后的p个数据进行拼接,得到完整的一个n粒度数据a’;

26、步骤s30:将p个小粒度写请求合并为一个n粒度写请求,对a’进行edac编码并写入冗余存储体。

27、与现有技术相比,本发明的优点就在于:

28、1、本发明的软硬协同的访存单元edac实现方法,原理简单、易实现、能够在降低开销的前提下提高片上存储器的可靠性;本发明显著减少了微处理器访存单元面积,以有效降低了微处理器整体面积和功耗。即,本发明在显著降低硬件代价基础上,能以较低的开销实现了访存单元常用的访存粒度n的edac功能,还能对所有小粒度数据访存提供同样纠错能力的edac功能,实现了对微处理器片上存储器的多粒度访存数据的全面、一致的可靠性设计与保护。

29、2、本发明的软硬协同的访存单元edac实现方法,实现简单且硬件开销较少。本发明采用微处理器常用的较大数据访存粒度构造edac硬件电路,较现有支持小粒度数据访存的edac方案,不仅显著减少edac校验码容量,大幅减少存储器面积;同时edac编、解码电路模块数少,硬件开销进一步减小;能显著减少访存单元面积和功耗,有效降低微处理器整体面积。

30、3、本发明的软硬协同的访存单元edac实现方法,通过软件宏定义编程方法实现访存单元小粒度写请求的数据保护。软件部分采用宏定义技术,将小粒度写操作重新封装成n粒度数据的先读后写操作,并将小粒度数据拼接到n粒度数据中以实现edac的统一编码。宏定义为用户提供便捷调用接口,用户无需理解宏内部实现方式,按需调用即可,以达到友好的交互体验。

31、提供一种软硬件协同的访存单元edac电路及实现方法,在满足纠错能力的可靠性设计需求基础上,能够

32、4、本发明的软硬协同的访存单元edac实现方法,为一种软硬协同的edac实现方法,整个edac电路实现简单,可移植性好,便于广泛应用在各种微处理器的片上存储器的可靠性设计中。本发明能够实现存储效率高、硬件面积开销小、且支持多粒度访存数据完整保护等效果。

- 还没有人留言评论。精彩留言会获得点赞!