一种计算设备的制作方法

本技术涉及服务器,尤其涉及一种计算设备。

背景技术:

1、当今服务器行业发展迅猛,产品推陈出新速度快,单板硬件的种类越来越多,因此企业需要开发许多单板,通常单板硬件设计需要满足不同客户的多样化需求,为了管理诸多的硬件版本,相应地也要开发繁多的bmc(baseboard management controller,基板管理控制器)软件版本,这样就会造成企业需要花费过多的资源投入到bmc软件版本管理上,在增加了软件版本管理复杂度的同时也会因为软件实例过多而造成一定程度的混乱。因此在自身版本管理上和客户技术支持上,企业需要能够做到采用单一bmc软件版本可以无差别管理不同的单板硬件配置,例如pcb(printed circuit borad,印刷电路板)版本,bom(billof materials,材料清单)版本,配置版本等等。

2、另外,服务器主板设计开发阶段,单板硬件id配置和检测极为重要,假使无法正确的得知目前的硬件id,将会导致无法配合当前的硬件设计,严重将影响系统无法开机或功能不齐全的问题。在相关的服务器主板设计中,一般采用cpld(complex programmablelogic device,复杂可编程逻辑器件)配合bmc采集硬件id配置。

3、其中,服务器行业通过cpld采集硬件id配置时,一般会采用gpio(generalpurpose input/output,通用输入输出)管脚高低电平配置的方式或外部挂接pca9555芯片进行并行转串行的方式。但采用gpio管脚高低电平配置的方式占用i/o管脚多;外部挂接pca9555芯片进行并行转串行的方式会增加系统设计和pcb layout设计复杂度;而且两种方式更改配置麻烦,对bom变动较大,并在需要重工更改外部电阻配置时,会增加较大的工作量。

技术实现思路

1、为了解决上述问题,本技术实施例提供了一种计算设备,可以在减少占用cpld的gpio管脚资源和硬件元件物料的情况下,能够识别不同的单板硬件版本配置信息。

2、本技术实施例提供的一种计算设备,包括:多个单板、控制电路、逻辑器件和rc延时电路,其中,每个所述单板上设置有所述rc延时电路,且不同的所述单板上的所述rc延时电路的延时参数不同;所述逻辑器件与rc延时电路电连接,用以采集rc延时电路在所述单板上电时,rc电平跳变的延时;所述控制电路与所述逻辑器件电连接,以获取所述电平跳变的延时,以识别单板id。

3、该设备中,rc延时电路位于单板上,且不同的单板上的所述rc延时电路的延时参数不同,也就是说每个单板上rc延时电路的延时数值是不同的,通过设定不同的延时参数对应不同的单板硬件id配置,便可以通过逻辑器件对不同单板上输入信号电平跳变的延时采集,实现不同单板硬件id配置之间的区分。

4、本技术实施例中的逻辑器件通过检测由rc延时电路输入信号跳变的用时,经过逻辑器件将时间量转换为寄存器数值,用以判断和识别单板id配置。由此,可以在占用极少的cpld的gpio管脚资源和硬件元件物料的情况下,能够识别不同的单板硬件版本配置信息。

5、在一种可能的实现方式中,所述外部rc延时电路包括开关管和至少一组串联的电阻和电容;其中,逻辑器件连接所述开关管的受控端,用以控制所述开关管的导通;且逻辑器件的输入管脚与电容管脚电连接,用以采样电容管脚的电平和跳变状态。

6、在该实现方式中,rc延时电路由简单的元器件组成,包括开关管、电阻和电容。这些元器件易于获得并且成本较低,这降低了整个电路的成本,也降低了电路的维护需求和故障率。

7、同时,由于逻辑器件的输入管脚与电容管脚电连接,因此rc延时电路可以接受不同类型和幅度的输入信号。这使得rc延时电路非常灵活,并可适用于各种应用场景。

8、逻辑器件检测和识别rc延时电路的延时数值时,可以输出一个使能信号,打开开关管,使得rc延时电路开始运行,此时电容器开始充电,并且rc延时电路的输出端也开始输出电压,逻辑器件的输入管脚能够接收到rc延时电路输出端的输出电压,直至逻辑器件检测到rc延时电路输出端的输出电压产生高电平跳变,记录产生高电平跳变的用时,便是rc延时电路的延迟时间,即电容器充电过程的时间开销;将rc延时电路的延时标记为单板硬件id配置,以此实现区分不同单板硬件id配置。

9、而且,本技术实施例中的rc电路选择范围较大,仅使用一个开关管,然后选配和组合不同数值和量级的电阻和电容,即可产生多种时间长度组合,在复杂场景情况下可以并行使用多个电阻和电容的组合,就可以标识多个单板硬件id配置,以扩大本技术实施例所提供设备的应用场景。本技术实施例通过cpld和外部rc延时电路的互相连通和配合可以实现高效的单板id配置检测和识别。

10、在一种可能的实现方式中,多个所述单板中,各个所述单板上rc延时电路数量不同,单个单板上多个rc延时电路之间相互并联。

11、在一种可能的实现方式中,多个所述单板中,各个所述单板上rc延时电路数量不同,单个单板上多个rc延时电路之间相互串联。

12、在一种可能的实现方式中,多个所述单板中,不同的所述单板上rc延时电路中的电阻r的电阻值和/或电容c的电容值不同。

13、在一种可能的实现方式中,所述rc延时电路中的电阻的阻值范围为1ω-100kω。

14、在一种可能的实现方式中,所述rc延时电路中电容的电容值范围为1μf-100μf。

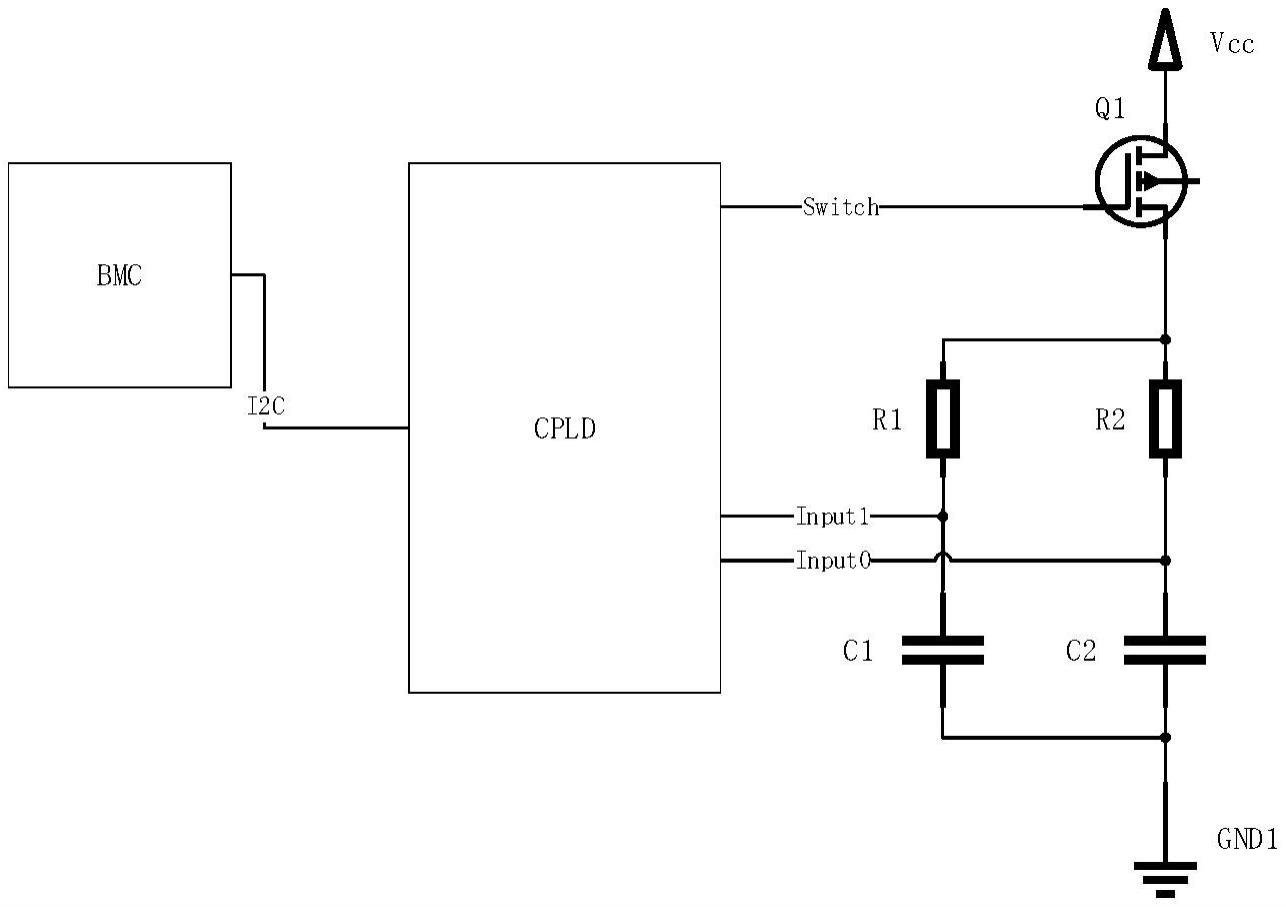

15、在一种可能的实现方式中,所述rc延时电路包括p-mosfet、电阻r1、电容c1、电阻r2和电容c2;其中,所述p-mosfet的受控端与逻辑器件电连接,p-mosfet的输出端与电阻r1、电阻r2的一端电连接,且所述p-mosfet还连接电源vcc;所述电阻r1的另一端与所述电容c1的一端连接;所述电阻r2的另一端与所述电容c2的一端连接;所述电容c1和电容c2的一端还分别与cpld输入管脚电连接,且所述电容c1和电容c2的另一端电连接后接地gnd1。

16、在该实施方式中,rc延时电路的延时参数可由电阻值和电容值进行设定,其计算公式为:

17、t=r×c×ln((u-uc)/u)

18、其中,t表示充电时间,单位为秒;

19、r表示电阻的阻值,单位为欧姆;

20、c表示电容的电容值,单位为法拉;

21、u表示电源电压,单位为伏特;

22、uc表示电容始初电压,即充电开始时电容两极之间的电压,单位为伏特。

23、本技术实施例中,通过调整电阻的电阻值和电容的电容值以及并排或串联多组串联的电阻和电容,以实现配置不同单板上rc延时电路的延时参数,来对应识别不同的硬件版本配置信息。同时,经由延时参数的计算公式我们可以看出,要增大延时参数便可通过增加电阻或电容的值实现,减少延时参数便可通过降低电阻或电容的值实现。电阻或电容的值较小时,会提升电路对延时参数的检测效率,但对于电路的检测精度要求会提升;电阻或电容的值较大时,会降低电路对延时参数的检测效率,但对于电路的检测精度要求会提升,故而在改变电容器或电阻器的值时,若要确保新的延时参数能够满足设计要求,需要考虑到电容器和电阻器的可用范围、精度等因素,然后在实际应用中进行测试和调整,以确保电路的性能和稳定性。

24、在一种可能的实现方式中,所述逻辑器件为复杂可编程逻辑器件cpld,所述控制电路为基板管理控制器bmc;其中,所述cpld将采集的rc电平跳变的延时转换为寄存器数值并存储;所述bmc读取逻辑器件存储的已转换的寄存器数值,以识别单板id。

25、在一种可能的实现方式中,所述逻辑器件为复杂可编程逻辑器件cpld,所述cpld内包括上电复位电路、延时电路、输出控制电路、电平边沿检测电路、计数器电路和数值寄存器;其中,所述延时电路与所述输出控制电路电连接,所述延时电路用以设定固定延时,再触发输出控制电路;所述输出控制电路与所述rc延时电路电连接,所述输出控制电路在经过设定的延时之后,输出使能信号,以使rc延时电路开始工作;所述电平边沿检测电路与所述rc延时电路的输入信号端电连接,用以用于接收rc延时电路的输入信号的电平跳变沿;所述计数器电路与所述电平边沿检测电路电连接,用于记录从rc延时电路开始工作到所述电平边沿检测电路检测到输入信号电平跳变的延时;所述数值寄存器与所述计数器电路电连接,用于将计数器电路记录的输入信号电平跳变延时转换为寄存器数值并储存;所述上电复位电路与上述各个逻辑电路电连接,用以为其它逻辑电路提供寄存器状态复位,使得cpld开始工作时处于初始化状态,以确保cpld的正常工作。

26、在该实现方式中,当cpld芯片完成上电复位并进入正常工作状态时,经过内部延时电路设定的一定延时后,由输出控制电路产生一个switch低电平信号来打开外部的p-mosfet,使外部rc延时电路开始工作,对电容进行充电。当cpld的输入管脚检测到电平由低变为高时,即可触发内部的边沿检测电路,从而将cpld内部计数器电路的数值存入寄存器中,然后再由bmc读取该数值,完成单板id配置检测和识别。

27、在一种可能的实现方式中,所述寄存器数值为bmc可以识别和读取的16进制数字。

28、在该实施方式中,寄存器数值指的是通过计数器电路记录的输入信号电平跳变延时转换后得到的数字量。这个数字量代表了输入信号电平变化所经历的时间长度,通常表示为一个16进制数字,不同的16进制数字设定对应不同的单板硬件版本(id配置)。数值寄存器与计数器电路电连接,可以实现将该数字量保存在寄存器中,方便后续的数据处理和控制。

29、在一种可能的实现方式中,所述输入信号的电平高低跳变满足cpld gpio管脚阈值电压时被识别为有效高低电平变化,用以确定输入信号电平跳变的延时。

30、在一种可能的实现方式中,所述cpld gpio管脚阈值电压为1.5-3.5v。

31、在该实施方式中,cpld gpio管脚阈值电压的设定是根据硬件条件和信号特性等一系列因素进行计算和优化的,可以达到较高的精度。因此,当输入信号的高低跳变满足这个阈值时,就可以确定输入信号电平跳变的延时。相比于其他方法,如软件延时、rc延时等,这种方式能够保证延时时间的准确性。

32、本技术实施例提供的一种计算设备,可以用于检测服务器单板硬件配置信息,本技术使用cpld、电阻、电容以及p-mosfet组成的可控rc延时电路,利用电容的充电行为所消耗的时间,来标定不同规格的电阻和电容组合所代表的数值,不同的数值对应不同的单板硬件版本,可以在减少占用cpld的gpio管脚资源和硬件元件物料的情况下,让bmc读取后用以识别不同的单板硬件id配置信息。

- 还没有人留言评论。精彩留言会获得点赞!