一种逻辑运算单元电路和加法器电路的制作方法

本技术涉及但不限于数字电路技术,尤指一种逻辑运算单元电路和加法器电路。

背景技术:

1、加法器作为最基本的逻辑运算单元,普遍应用在各种类型的处理器中。在电路系统中,加法器主要负责计算、索引等。而且加法器也是其他硬件逻辑运算单元如乘法器、减法器等的重要组成部分。根据加法器电路的拓扑结构不同,可以对加法器进行分类,常见的加法器拓扑结构大致包括:行波进位法、超前进位法等。

2、不同拓扑结构的加法器,在面积和速率上各不相同。随着对处理器核的高工作频率和低功耗的要求,对加法器也有了更高的要求。如何在保证高速率的同时,降低功耗;或者在特定的速率场景下,采用面积更小、功耗更低的拓扑结构,平衡功耗与速率的关系成为了亟需解决的问题。

技术实现思路

1、本技术提供一种逻辑运算单元电路和加法器电路,电路结构简洁,能够很好地平衡功耗与速率的关系。

2、本技术实施例提供一种逻辑运算单元电路,应用于多比特加法器,所述逻辑运算单元电路用于实现!g逻辑和!p逻辑,包括:一与-或非门、一与非门;

3、所述与-或非门的三个输入分别为pi:k、gk-1:j和gi:k,所述与-或非门的输出为!gi:j;

4、所述与非门的两个输入分别pk-1:j、所述pi:k,与非门的输出为!pi:j;

5、其中,i、k、j分别表示所述加法器的输入数据的第几比特数据,i>k>j。

6、本技术实施例还提供一种逻辑运算单元电路,应用于多比特加法器,所述逻辑运算单元电路用于实现g逻辑和p逻辑,包括:一或-与非门、一或非门;

7、所述或-与非门的三个输入分别为!pi:k、!gk-1:j和!gi:k,所述或-与非门的输出为gi:j;

8、所述或非门的两个输入分别!pk-1:j、所述!pi:k,或非门的输出为pi:j;

9、其中,i、k、j分别表示所述加法器的输入数据的第几比特数据,i>k>j。

10、本技术实施例又提供一种逻辑运算单元电路,应用于多比特加法器,所述逻辑运算单元电路用于实现p逻辑,包括:两个与非门、一个或非门;其中,

11、一个与非门的两个输入分别为pi:k、pk-1:m,输出为!pi:m;

12、另一个与非门的两个输入分别为pm-1:n、pn-1:j,输出为!pm-1:j;

13、或非门的两个输入分别为所述两个与非门的输出,或非门的输出为pi:j;其中,i、k、m、n、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>m>n>j。

14、本技术实施例再提供一种逻辑运算单元电路,应用于多比特加法器,所述逻辑运算单元电路用于实现g逻辑,包括:两个与-或非门、一个或-与非门;其中,

15、一个与-或非门的三个输入分别为pi:k、gk-1:m和gi:k,输出为!gi:m;

16、另一个与-或非门的三个输入分别为pm-1:n、gn-1:j和gm-1:n,输出为!gm-1:j;

17、或-与非门的三个输入分别为两个与-或非门的输出,以及!pi:m,输出为gi:j;其中,i、k、m、n、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>m>n>j。

18、本技术实施例还提供一种加法器电路,包括上述任一项所述的逻辑运算单元电路。

19、在一种示例性实例中,所述加法器为多必特lfa加法器,或多必特bk加法器。

20、本技术实施例又提供一种加法器电路,所述加法器为n+1=32位lfa加法器;所述lfa加法器包括七级依次连接的运算单元,其中,

21、第一级运算单元包括n+1个第一单元电路,所述第一单元电路用于产生p逻辑和g逻辑,gi=and(ai,bi),pi=xor(ai,bi),ai、bi分别表示参与所述lfa加法器运算的数据a和数据b的第i比特数据;

22、第二级运算单元包括个如上述本技术实施例提供的一种所述的逻辑运算单元电路、1个第七单元电路;其中,所述第七单元电路用于实现!g逻辑,包括:一与-或非门,所述与-或非门的三个输入分别为pi:k、gk-1:j和gi:k,所述与-或非门的输出为!gi:j,其中,i、k、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>j;

23、第三级运算单元包括个非门、个如上述本技术实施例还提供的一种所述的逻辑运算单元电路,以及2个第八单元电路;其中,所述第八单元电路用于实现g逻辑,包括:一或-与非门,所述或-与非门的三个输入分别为!pi:k、!gk-1:j和!gi:k,所述或-与非门的输出为gi:j,其中,i、k、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>j;

24、第四级运算单元包括个非门、个如上述本技术实施例提供的一种所述的逻辑运算单元电路,以及4个所述第七单元电路;

25、第五级运算单元包括个非门、个如上述本技术实施例还提供的一种所述的逻辑运算单元电路,以及8个所述第八单元电路;

26、第六级运算单元包括个所述第七单元电路,和5个非门;

27、第七级运算单元包括n个第四单元电路和21个非门,其中所述第四单元电路用于实现si=xor(pi,gi-1,0),si表示经过所述lfa加法器运算后的第i比特数据。

28、本技术实施例再提供一种加法器电路,所述加法器为n+1=32位bk加法器;所述bk加法器包括十级依次连接的运算单元,其中,

29、第一级运算单元包括n+1个第一单元电路,所述第一单元电路用于产生p逻辑和g逻辑,gi=and(ai,bi),pi=xor(ai,bi),ai、bi分别表示参与所述lfa加法器运算的数据a和数据b的第i比特数据;

30、第二级运算单元包括个如上述本技术实施例提供的一种所述的逻辑运算单元电路、1个第七单元电路;其中,所述第七单元电路用于实现!g逻辑,包括:一与-或非门,所述与-或非门的三个输入分别为pi:k、gk-1:j和gi:k,所述与-或非门的输出为!gi:j,其中,i、k、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>j;

31、第三级运算单元包括个如上述本技术实施例还提供的一种所述的逻辑运算单元电路,和1个第八单元电路;其中,所述第八单元电路用于实现g逻辑,包括:一或-与非门,所述或-与非门的三个输入分别为!pi:k、!gk-1:j和!gi:k,所述或-与非门的输出为gi:j,其中,i、k、j分别表示所述加法器的输入数据的第几比特比特数据,i>k>j;

32、第四级运算单元包括个如上述本技术实施例提供的一种所述的逻辑运算单元电路,和1个所述第七单元电路;

33、第五级运算单元包括1个如上述本技术实施例还提供的一种所述的逻辑运算单元电路,和1所述的第八单元电路;

34、第六级运算单元包括2个所述第七单元电路,和1个非门;

35、第七级运算单元包括2个所述第八单元电路和2个非门,以及1个所述第七单元电路;

36、第八级运算单元包括4个所述第七单元电路和4个非门,以及3个所述第八单元电路;

37、第九级运算单元包括7个所述第七单元电路,以及8个所述第八单元电路和8个非门;

38、第十级运算单元包括n个第四单元电路和7个非门;其中所述第四单元电路用于实现si=xor(pi,gi-1,0),si表示经过所述lfa加法器运算后的第i比特数据。

39、本技术实施例提供的加法器电路采用了结构最简洁、逻辑门最少的电路,加法器电路结构简洁,在采用面积和延迟上都更好,功耗更低,很好地平衡了功耗与速率的关系,进而使得电路运行的频率更快,性能更好。

40、本实用新型的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本实用新型而了解。本实用新型的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

41、附图概述

42、附图用来提供对本技术技术方案的进一步理解,并且构成说明书的一部分,与本技术的实施例一起用于解释本技术的技术方案,并不构成对本技术技术方案的限制。

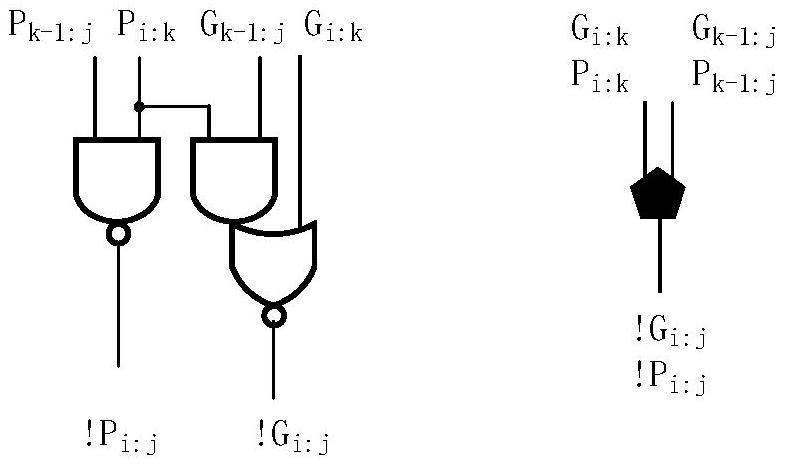

43、图1为相关技术中主流的加法器中核心的逻辑运算单元的电路拓扑结构示意图;

44、图2(a)为一种实施例中实现连续两级p逻辑的电路结构示意图;

45、图2(b)为另一种实施例中实现连续两级p逻辑的电路结构示意图;

46、图3(a)为一种实施例中的实现连续两级g逻辑的电路结构示意图;

47、图3(b)为另一种实施例中实现连续两级g逻辑的电路结构示意图;

48、图4为一种lfa加法器电路的拓扑结构示意图;

49、图5(a)为图4所示lfa加法器电路中第一单元电路的电路结构示意图和对应的示意图符号;

50、图5(b)为图4所示lfa加法器电路中第二单元电路的电路结构示意图和对应的示意图符号;

51、图5(c)为图4所示lfa加法器电路中第三单元电路的电路结构示意图和对应的示意图符号;

52、图5(d)为图4所示lfa加法器电路中第四单元电路的电路结构示意图和对应的示意图符号;

53、图6(a)为另一种实施例lfa加法器电路中第五单元电路的电路结构示意图和对应的示意图符号;

54、图6(b)为另一种实施例lfa加法器电路中第六单元电路的电路结构示意图和对应的示意图符号;

55、图6(c)为另一种实施例lfa加法器电路中第七单元电路的电路结构示意图和对应的示意图符号;

56、图6(d)为另一种实施例lfa加法器电路中第八单元电路的电路结构示意图和对应的示意图符号;

57、图7为本一种实施例中lfa加法器电路的拓扑结构示意图;

58、图8为一种实施例中bk加法器电路的拓扑结构示意图;

59、图9为另一种实施例中bk加法器电路的拓扑结构示意图。

60、详述

61、为使本技术的目的、技术方案和优点更加清楚明白,下文中将结合附图对本技术的实施例进行详细说明。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互任意组合。

62、为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

63、除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

64、主流的加法器拓扑结构中,核心的逻辑运算单元包括propagate逻辑(简称为p逻辑)和generate逻辑(简称为g逻辑),电路结构图如图1所示,p逻辑由一个与(and)门构成,pi:j=and(pi:k,pk-1:j);g逻辑由一个与-或(ao,and-or)门构成,gi:j=or(gi:k,and(pi:k,gk-1:j))=ao(gi:k,pi:k,gk-1:j);其中,i>k>j,i、k、j分别表示输入数据的第几比特(bit),如i表示第i比特。

65、为了尽可能用结构最简洁,逻辑门最少的电路来实现等价逻辑,本技术提出一种逻辑运算单元电路,包括p逻辑电路和/或g逻辑电路;其中,p逻辑电路包括或非门和/或与非门,以实现p逻辑或p非(!p)逻辑;g逻辑电路包括与-或非(aoi)门和/或或-与非(oai)门,以实现g逻辑或!g逻辑。

66、在一种示例性实例中,以连续两级p逻辑为例,图2(a)为一种实施例中的实现连续两级p逻辑的电路结构示意图,图2(b)为另一种实施例中实现连续两级p逻辑的电路结构示意图,图2(a)和图2(b)两个电路结构是等价的,其中,i>k>m>n>j,i、k、m、n、j分别表示输入数据的第几比特。对于这两个电路应用于加法器中时,i、k、m、n、j分别表示参与加法运算的数据的第几比特,如i表示第i比特。如图2(a)所示,实现连续两级p逻辑的电路结构由3个与门构成,如图2(b)所示,实现连续两级p逻辑的电路结构由2个与非门和1个或非门构成。在一种实施例中,实现p逻辑的连续两级p逻辑的电路结构包括:两个与非门、一个或非门;其中,其中一个与非门的两个输入分别为pi:k、pk-1:m,输出为!pi:m;另一个与非门的两个输入分别为pm-1:n、pn-1:j,输出为!pm-1:j;或非门的两个输入分别为两个与非门的输出即!pi:m和!pm-1:j,或非门的输出为pi:j,其中,i>k>m>n>j,pi:j=nor(nand(pi:k,pk-1:m),nand(pm-1:n,pn-1:j))。

67、图2(a)和图2(b)所示的两个电路结构中,与门和与非门相比,与门的采用面积要多1个反相器(inv),延迟也会多1个inv。与非门和或非门相比,二者的采用面积和延迟近乎相等。那么,整体而言,图2(b)所示的本技术实施例中实现连续两级p逻辑的电路结构相对于图2(a)所示的典型的实现连续两级p逻辑的电路结构,采用面积节省了3个inv,电路最长路径延迟减少了2个inv的延迟。可见,本技术实施例提供的p逻辑采用了结构最简洁,逻辑门最少的电路实现了和典型的p逻辑相同的功能,也就是说,本技术实施例提供的p逻辑电路结构简洁,在采用面积和延迟上都更好,很好地平衡了功耗与速率的关系。

68、在一种示例性实例中,以连续两级g逻辑为例,图3(a)为一种实施例中的实现连续两级g逻辑的电路结构示意图,图3(b)为另一种实施例中实现连续两级g逻辑的电路结构示意图,图3(a)和图3(b)两个电路结构是等价的,其中,i>k>m>n>j,i、k、m、n、j分别表示输入数据的第几比特。对于这两个电路应用于加法器中时,i、k、m、n、j分别表示参与加法运算的数据的第几比特,如i表示第i比特。假设图3(a)的表达式为:gi:j=function1(gi:k,pi:k,gk-1:m,gm-1:n,pm-1:n,gn-1:j,pi:m),是一种实施例中的连续两级g逻辑电路结构。假设图3(b)的表达式为:gi:j=function2(gi:k,pi:k,gk-1:m,gm-1:n,pm-1:n,gn-1:j,!pi:m)。对比两个表达式,两个等式的左边结果相同,两个等式的右边输入项有一项不同,不同的部分是pi:m和!pi:m,按照相关技术可知,pi:m=and(pi:k,pk-1:m),!pi:m=nor(pi:k,pk-1:m),因此,在输入项相同的前提下,pi:m和!pi:m的实现可以采用and门和nor门进行转换。

69、如图3(a)所示,一种实施例中实现连续两级g逻辑电路结构由3个ao门构成。如图3(b)所示,另一种实施例中实现连续两级g逻辑的电路结构由两个与-或非(aoi,and-or-invert)门和一个或-与非(oai,or-and-invert)门构成。在一种实施例中,实现g逻辑的连续两级g逻辑的电路结构包括:两个与-或非门、一个或-与非门;其中,其中一个与-或非门的三个输入分别为pi:k、gk-1:m和gi:k,输出为!gi:m;另一个与-或非门的三个输入分别为pm-1:n、gn-1:j和gm-1:n,输出为!gm-1:j;或-与非门的三个输入分别为两个与-或非门的输出即!gi:m和!gm-1:j,以及!pi:m,输出为gi:j,其中,i>k>m>n>j,

70、图3(a)和图3(b)所示的两个电路结构中,ao门和aoi门相比,ao门的面积多1个inv,延迟多1个inv。aoi门和oai门相比,二者的采用面积和延迟相当。那么,整体而言,图3(b)所示的本技术实施例中实现连续两级g逻辑的电路结构相对于图3(a)所示的典型的实现连续两级g逻辑电路结构,采用面积节省了3个inv,电路最长路径延迟减少2个inv的延迟。可见,本技术实施例提供的p逻辑采用了结构最简洁,逻辑门最少的电路实现了和典型的g逻辑相同的功能,也就是说,本技术实施例提供的g逻辑电路结构简洁,在采用面积和延迟上都更好,很好地平衡了功耗与速率的关系。

71、加法器作为最基本的逻辑运算单元,主流的加法器拓扑结构中,核心的逻辑运算单元包括p逻辑电路和g逻辑电路。如何减小加法器电路的采用面积,降低其功耗,减小其电路延迟,使得加法器电路运行的频率更快,性能更好是一个亟需解决的问题。

72、在一种示例性实例中,以lfa加法器为例,其中lfa为lander fischer adder的缩写,lfa加法器以pg逻辑进行推导。图4为一种lfa加法器电路的拓扑结构示意图,图4中黑色六边形示意图符号表示的逻辑电路如图5(a)所示的第一单元电路,第一单元电路用于产生p逻辑,g逻辑,gi=and(ai,bi),pi=xor(ai,bi),ai、bi分别表示参与运算的数据a和数据b的第i比特数据。图4中黑色小方格示意图符号表示的逻辑电路如图5(b)所示的第二单元电路,第二单元电路用于实现pi:j=and(pi-1:j,pi:k),gi:j=ao(gi:k,pi:k,gk-1:j)。图4中灰色小方格示意图符号表示的逻辑电路如图5(c)所示的第三单元电路,第三单元电路用于实现gi:j=ao(gi:k,pi:k,gk-1:j)。图4中灰色六边形示意图符号表示的逻辑电路如图5(d)所示的第四单元电路,第四单元电路用于实现si=xor(pi,gi-1,0),si表示经过加法器运算后的输出第i比特数据。其中,图4中黑色小方格示意图符号表示的逻辑电路是一个p逻辑+g逻辑的电路。

73、为了减小lfa加法器电路的采用面积,降低其功耗,减小其电路延迟,如图7所示,其中,采用了图6(a)所示的对应示意图符号为黑色五边形的第五单元电路和图6(b)所示的对应示意图符号为黑色菱形的第六单元电路的组合,以及采用了图6(c)所示的对应示意图符号为灰色五边形的第七单元电路和图6(d)所示的对应示意图符号为灰色菱形的第八单元电路的组合。其中,图7中黑色五边形示意图符号表示的逻辑电路是图6(a)所示的采用本技术实施例提供的p逻辑电路和g逻辑电路实现的一个!p逻辑+!g逻辑的电路,图7中黑色菱形示意图符号表示的逻辑电路是图6(b)所示的采用本技术实施例提供的p逻辑电路和g逻辑电路实现的一个p逻辑+g逻辑的电路。图7中灰色五边形示意图符号表示的逻辑电路是图6(c)所示的采用本技术实施例提供的g逻辑电路实现的一个!g逻辑的电路,图7中灰色菱形示意图符号表示的逻辑电路是图6(d)所示的采用本技术实施例提供的g逻辑电路实现的一个g逻辑的电路。

74、在一种实施例中,图6(c)提供了一种实现!g逻辑的电路结构即第七单元电路,如图6(c)所示,本实施例中的g逻辑电路包括一与-或非门,该与-或非门的三个输入分别为pi:k、gk-1:j和gi:k,该与-或非门的输出为!gi:j,即!gi:j=aoi(gi:k,pi:k,gk-1:j),其中,i>k>j。

75、在一种实施例中,图6(a)提供了一种实现!p逻辑和!g逻辑的电路结构即第五电路单元,如图6(a)所示,本实施例中的p逻辑+g逻辑电路在图6(c)的基础上还包括一与非门,如图6(a)所示,与-或非门的三个输入分别为pi:k、gk-1:j和gi:k,该与-或非门的输出为!gi:j,!gi:j=aoi(gi:k,pi:k,gk-1:j);与非门的两个输入分别pk-1:j、pi:k,与非门的输出为!pi:j,!pi:j=nand(pk-1:j,pi:k)。

76、在一种实施例中,图6(d)提供了一种实现g逻辑的电路结构即第八电路单元,如图6(d)所示,本实施例中的g逻辑电路包括一或-与非门,该或-与非门的三个输入分别为!pi:k、!gk-1:j和!gi:k,该或-与非门的输出为gi:j,即gi:j=oai(!gi:k,!pi:k,!gk-1:j)。

77、在一种实施例中,图6(b)提供了一种实现p逻辑和g逻辑的电路结构即第六电路单元,如图6(b)所示,本实施例中的p逻辑+g逻辑电路在图6(d)的基础上还包括一或非门,如图6(b)所示,或-与非门的三个输入分别为!pi:k、!gk-1:j和!gi:k,该或-与非门的输出为gi:j,gi:j=oai(!gi:k,!pi:k,!gk-1:j);或非门的两个输入分别!pk-1:j、!pi:k,或非门的输出为pi:j,pi:j=nor(!pk-1:j,!pi:k)。

78、如图7所示,以n+1=32位的多比特lfa加法器为例,本技术实施例提供的lfa加法器电路,包括七级依次连接的运算单元,第一级运算单元包括n+1个第一单元电路;第二级运算单元包括个第五单元电路、1个第七单元电路;第三级运算单元包括个非门、个第六单元电路和2个第八单元电路;第四级运算单元包括个非门、个第五单元电路和4个第七单元电路;第五级运算单元包括个非门、个第六单元电路和8个第八单元电路;第六级运算单元包括个第七单元电路和5个非门;第七级运算单元包括n个第四单元电路和21个非门;其中,

79、第一级运算单元中,每一个第一单元电路,输入包括ai和bi,用于经过运算后输出为gi和pi;其中,ai为参与加法运算的数据a的每一位信息,bi为参与加法运算的数据b的每一位信息,i=0,1,2…n,n+1表示参与加法运算的数据a、数据b的位数。

80、第二级运算单元中,每一个第五单元电路,输入包括gi:k、pi:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi:j和!pi:j,其中,k=i,j=i-1,i=3,n-26,n-24…n-6,n-4,n-2,n;第七单元电路的输入包括gi:k、pi:k、gk-1:j,用于经过运算后输出为!gi:j,其中,k=i,j=i-1,i=1。

81、第三级运算单元中,每两个第六单元电路和一个非门组成一种第三级小运算单元(称为第一第三级小运算单元),两个第八单元电路和一个非门组成另一种第三级小运算单元(称为第二第三级小运算单元)。在第一第三级小运算单元中,非门的输入为gi-1和pi-1,用于输出为!gi-1和!pi-1;其中一个第六单元电路的输入包括!gi:k、!pi:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi:j和pi:j;另一个第六单元电路的输入包括非门的输出即!gi-1:k、!pi-1:k以及!gk-1:j、!pk-1:j,用于经过运算后输出为gi-1:j和pi-1:j,其中,k=i-1,j=i-3,i=7,n-20,n-16,n-12,n-8,n-4,n。在第二第三级小运算单元中,非门的输入为gi-1和pi-1,用于输出为!gi-1和!pi-1;其中一个第八单元电路的输入包括!gi:k、!pi:k、!gk-1:j,用于经过运算后输出为gi:j;另一个第八单元电路的输入包括非门的输出即!gi-1、!pi-1以及!gk-1:j,用于经过运算后输出为gi-1:j,其中,k=i-1,j=i-3,i=3。

82、第四级运算单元中,每四个第五单元电路和一个非门组成一种第四级小运算单元(称为第一第四级小运算单元),四个第七单元电路和一个非门组成另一种第四级小运算单元(称为第二第四级小运算单元)。在第一第四级小运算单元中,非门的输入为!gi-2:k和!pi-2:k,用于输出为gi-2:k和pi-2:k;其中一个第五单元电路的输入包括gi:k、pi:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi:j和!pi:j;另一个第五单元电路的输入包括gi-1:k-1、pi-1:k-1、gk-1:j、pk-1:j,用于经过运算后输出为!gi-1:j和!pi-1:j;再一个第五单元电路的输入包括非门的输出即gi-2:k、pi-2:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi-2:j和!pi-2:j;又一个第五单元电路的输入包括gi-3:k、pi-3:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi-3:j和!pi-3:j,其中,k=i-3,j=i-7,i=n-16,n-8,n。在第二第四级小运算单元中,非门的输入为!gi-2:k和!pi-2:k,用于输出为gi-2:k和pi-2:k;其中一个第七单元电路的输入包括gi:k、pi:k、gk-1:j,用于经过运算后输出为!gi:j;另一个第七单元电路的输入包括gi-1:k、pi-1:k、gk-1:j,用于经过运算后输出为!gi-1:j;再一个第七单元电路的输入包括非门的输出即gi-2:k、pi-2:k以及gk-1:j,用于经过运算后输出为!gi-2:j;又一个第七单元电路的输入包括gi-3:k、pi-3:k、gk-1:j,用于经过运算后输出为!gi-3:j,其中,k=i-3,j=i-7,i=n-24。

83、第五级运算单元中,每八个第六单元电路和三个非门组成一种第五级小运算单元(称为第一第五级小运算单元),八个第八单元电路和三个非门组成另一种第五级小运算单元(称为第二第五级小运算单元)。在第一第五级小运算单元中,第一非门的输入为gi-4:k、pi-4:k,输出为!gi-4:k、!pi-4:k;第二非门的输入为gi-5:k、pi-5:k,输出为!gi-5:k、!pi-5:k;第三非门的输入为gi-7、pi-7,输出为!gi-7、!pi-7;其中,第一第六单元电路的输入包括!gi:k、!pi:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi:j和pi:j;第二第六单元电路的输入包括!gi-1:k、!pi-1:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi-1:j和pi-1:j;第三第六单元电路的输入包括!gi-2:k、!pi-2:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi-2:j和pi-2:j;第四第六单元电路的输入包括!gi-3:k、!pi-3:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi-3:j和pi-3:j;第五第六单元电路的输入包括第一非门的输出即!gi-4:k、!pi-4:k以及!gk-1:j、!pk-1:j,用于经过运算后输出为gi-4:j和pi-4:j;第六第六单元电路的输入包括第二非门的输出即!gi-5:k、!pi-5:k以及!gk-1:j、!pk-1:j,用于经过运算后输出为gi-5:j和pi-5:j;第七第六单元电路的输入包括第一非门的输出即!gi-6:k、!pi-6:k以及!gk-1:j、!pk-1:j,用于经过运算后输出为gi-6:j和pi-6:j;第八第六单元电路的输入包括第三非门的输出即!gi-7:k、!pi-7:k以及!gk-1:j、!pk-1:j,用于经过运算后输出为gi-7:j和pi-7:j;其中,k=i-7,j=i-15,i=n,本实施例中n=31。在第二第五级小运算单元中,第一非门的输入为gi-4:k、pi-4:k,输出为!gi-4:k、!pi-4:k;第二非门的输入为gi-5:k、pi-5:k,输出为!gi-5:k、!pi-5:k;第三非门的输入为gi-7、pi-7,输出为!gi-7、!pi-7;其中,第一第八单元电路的输入包括!gi:k、!pi:k、!gk-1:j,用于经过运算后输出为gi:j;第二第八单元电路的输入包括!gi-1:k、!pi-1:k、!gk-1:j,用于经过运算后输出为gi-1:j;第三第八单元电路的输入包括!gi-2:k、!pi-2:k、!gk-1:j,用于经过运算后输出为gi-2:j;第四第八单元电路的输入包括!gi-3:k、!pi-3:k、!gk-1:j,用于经过运算后输出为gi-3:j;第五第八单元电路的输入包括第一非门的输出即!gi-4:k、!pi-4:k以及!gk-1:j,用于经过运算后输出为gi-4:j;第六第八单元电路的输入包括第二非门的输出即!gi-5:k、!pi-5:k以及!gk-1:j,用于经过运算后输出为gi-5:j;第七第八单元电路的输入包括第一非门的输出即!gi-6:k、!pi-6:k以及!gk-1:j,用于经过运算后输出为gi-6:j;第八第八单元电路的输入包括第三非门的输出即!gi-7:k、!pi-7:k以及!gk-1:j,用于经过运算后输出为gi-7:j;其中,k=i-7,j=i-15,i=n-16。

84、第六级运算单元中,包括个第七单元电路和5个非门,其中,每个非门的输入为!gi-8-p:k和!pi-8-p:k,用于输出为gi-8-p:k和pi-8-p:k,p=0,1,2,3和6;每个第七单元电路的输入包括gn-m:k、pn-m:k、gk-1:j,用于经过运算后输出为!gn-m:j,其中,k=i-15,j=i-31,i=17、18、19…n;m=0,1,2…15。

85、第七级运算单元中,包括n个第四单元电路和21个非门,其中,每个非门的输入为!gn-p:0和!pn-p:0,用于输出为gn-p:0和pn-p:0,p=0,1,2,3…15,24,25,26,27和30;每个第四单元电路的输入包括gi-1:0、pi,用于经过加法运算后输出为si,其中,i=1,2,3…n,之外s0=p0,进位carry=g31:0。

86、对比图4和图7,不难看出,如图7所示的重新构建整个lfa加法器电路的拓扑结构,相对于图4所示的lfa加法器电路的拓扑结构,结合对图2(b)和图3(b)的分析,采用了结构最简洁,逻辑门最少的电路实现了lfa加法器,也就是说,本技术实施例提供的lfa加法器电路结构简洁,在采用面积和延迟上都更好,功耗更低,很好地平衡了功耗与速率的关系,进而使得电路运行的频率更快,性能更好。

87、需要说明的是,如图7中可见,在必要情况下,会增加一些非门电路,如图7中的示意图符号所示,以保证正确的逻辑实现,这点是本领域技术人员在基于本技术实施例提供的p逻辑电路和g逻辑电路的基础上实现lfa加法器时,容易想到的。

88、在一种示例性实例中,以bk加法器为例,其中bk为brent kung adder的缩写,bk加法器由richard p.brent和h.t.kung教授于上世纪80年代提出,bk加法器以典型的pg逻辑进行推导。图8为一种实施例中bk加法器电路的拓扑结构示意图,图9为另一种实施例中bk加法器电路的拓扑结构示意图,本实施例中,同样,在图9所示的本技术实施例bk加法器电路中,采用了图6(a)所示的对应示意图符号为黑色五边形的第五单元电路和图6(b)所示的对应示意图符号为黑色菱形的第六单元电路的组合,以及采用了图6(c)所示的对应示意图符号为灰色五边形的第七单元电路和图6(d)所示的对应示意图符号为灰色菱形的第八单元电路的组合。

89、如图9所示,以n+1=32位的多比特bk加法器为例,本技术实施例提供的bk加法器电路,包括十级依次连接的运算单元,第一级运算单元包括n+1个第一单元电路;第二级运算单元包括个第五单元电路、1个第七单元电路;第三级运算单元包括个第六单元电路和1个第八单元电路;第四级运算单元包括个第五单元电路和1个第七单元电路;第五级运算单元包括1个第六单元电路和1第八单元电路;第六级运算单元包括2个第七单元电路和1个非门;第七级运算单元包括2个第八单元电路和2个非门,以及1个第七单元电路;第八级运算单元包括4个第七单元电路和4个非门,以及3个第八单元电路;第九级运算单元包括7个第七单元电路,以及8个第八单元电路和8个非门;第十级运算单元包括n个第四单元电路和9个非门;其中,

90、第一级运算单元中,每一个第一单元电路,输入包括ai和bi,用于经过运算后输出为gi和pi;其中,ai为参与加法运算的数据a的每一位信息,bi为参与加法运算的数据b的每一位信息,i=0,1,2…n,n表示参与加法运算的数据a、数据b的位数。

91、第二级运算单元中,每一个第五单元电路,输入包括gi:k、pi:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi:j和!pi:j,其中,k=i,j=i-1,i=n,n-2,n-4,n-6…n-24,n-26,3;第七单元电路的输入包括gi:k、pi:k、gk-1:j,用于经过运算后输出为!gi:j,其中,k=i,j=i-1,i=1。

92、第三级运算单元中,每个第六单元电路的输入包括!gi:k、!pi:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi-m:j和pi-m:j;其中,k=i-1,j=i-3,i=n,n-4,n-8,n-2,n-12,n-16,n-20,7。第八单元电路的输入包括!gi:k、!pi:k、!gk-1:j,用于经过运算后输出为gi:j,其中,k=i-1,j=i-3,i=3。

93、第四级运算单元中,每个第五单元电路的输入包括gi:k、pi:k、gk-1:j、pk-1:j,用于经过运算后输出为!gi:j和!pi:j,其中,k=i-3,j=i-7,i=n,n-8,n-16。第七单元电路输入包括gi:k、pi:k、gk-1:j,用于经过运算后输出为!gi:j,其中,k=i-3,j=i-7,i=7。

94、第五级运算单元中,1个第六单元电路的输入包括!gi:k、!pi:k、!gk-1:j、!pk-1:j,用于经过运算后输出为gi:j和pi:j;其中,k=i-7,j=i-15,i=n;1个第八单元电路的输入包括!gi:k、!pi:k、!gk-1:j,用于经过运算后输出为gi:j,其中,k=i-7,j=i-15,i=n-16=15。

95、第六级运算单元中,1个非门的输入为!gi-8:k和!pi-8:k,用于输出为gi-8:k和pi-8:k;其中一个第七单元电路的输入包括gi:k、pi:k、gk-1:j,用于经过运算后输出为!gi:j;另一个第七单元电路的输入包括非门的输出即gi-8:k、pi-8:k以及gk-1:j,用于经过运算后输出为!gi-8:j,其中,k=i-15,j=i-31,i=n。

96、第七级运算单元中,1个第七单元电路的输入包括gi-12:k、pi-12:k以及gk-1:j,用于经过运算后输出为!gi-12:j;其中一个非门(第一非门)的输入为gi-4:k+8和pi-4:k+8,用于输出为!gi-4:k+8和!pi-4:k+8,其中一个第八单元电路的输入包括第一非门的输出即!gi-4:k+8和!pi-4:k+8以及!gk-1:j,用于经过运算后输出为gi-4:j;另一个非门(第二非门)的输入为gi-20:k-8和pi-20:k-8,用于输出为!gi-20:k-8和!pi-20:k-8,另一个第八单元电路的输入包括第二非门的输出即!gi-20:k-8和!pi-20:k-8以及!gk-1:j,用于经过运算后输出为gi-20:j;其中,k=16,j=i-31,i=n。

97、第八级运算单元中,4个非门的输入分别为:!gi:k和!pi:k、!gi-12:k-12和!pi-12:k-12、!gi-16:k和!pi-16:k、!gi-24:k和!pi-24:k,分别用于输出gi:k和pi:k、gi-12:k-12和pi-12:k-12、gi-16:k和pi-16:k、gi-24:k和pi-24:k;4个第七单元电路的输入分别包括:非门的输出即gi:k、pi:k以及gk-2:j、非门的输出即gi-12:k-12、pi-12:k-12以及gk-14:j、非门的输出即gi-16:k-16、pi-16:k-16以及gk-18:j、非门的输出即gi-24:k-24、pi-24:k-24以及gk-26:j,分别用于经过运算后分别输出:!gi:j、!gi-12:j、!gi-16:j和、!gi-24:j;3个第八单元电路的输入分别包括:!gi-4:k-4、!pi-4:k-4和!gk-5:j,!gi-8:k-8、!pi-8:k-8和!gk-9:j,!gi-20:k-20、!pi-20:k-20和!gk-21:j,分别用于经过运算后分别输出为gi-4:j、gi-8:j和gi-20:j;其中,k=i-1,j=i-29,i=n-2。

98、第九级运算单元中,7个第七单元电路的输入为:gi:k、pi:k以及gk-1:j,用于经过运算后分别输出为!gi:j,其中,k=i,j=0,对应7个第七单元电路的i分别取值为:i=n-3、n-5、n-9、n-15、n-19、n-21、n-27;每个非门的输入为:gi:k和pi:k,用于输出!gi:k和!pi:k,每个非门的输出分别与各第八单元电路的一输入连接,每个第八单元电路的输入包括!gi:k、!pi:k和!gk-1:j-i,用于经过运算后分别输出为gi-4:j;其中,k=i,j=i,对应8个非门的i分别取值为:i=n-1、n-7、n-11、n-13、n-17、n-23、n-25、n-29。

99、第十级运算单元中,包括n个第四单元电路和9个非门,其中,每个非门的输入为!gi-p:0和!pi-p:0,用于输出为gi-p:0和pi-p:0,对应每个非门的i的取值为n,p=0,3,5,9,15,19,21,27和30;每个第四单元电路的输入包括gi-1:0、pi,用于经过运算后输出为si,其中,对应每个第四单元的i的取值为:i=1,2,3…n,之外s0=p0,进位carry=g31:0。

100、对比图8和图9,不难看出,图9所示的重新构建整个bk加法器电路的拓扑结构,相对于图8所示的bk加法器电路的拓扑结构,结合对图2(b)和图3(b)的分析,采用了结构最简洁,逻辑门最少的电路实现了bk加法器,也就是说,本技术实施例提供的bk加法器电路结构简洁,在采用面积和延迟上都更好,功耗更低,很好地平衡了功耗与速率的关系,进而使得电路运行的频率更快,性能更好。

101、需要说明的是,如图9中可见,在必要情况下,会增加一些非门电路,如图9中的示意图符号所示,以保证正确的逻辑实现,这点是本领域技术人员在基于本技术实施例提供的p逻辑电路和g逻辑电路的基础上实现lfa加法器时,容易想到的。

102、如上所述,本技术实施例提供一种加法器电路,其中的p逻辑电路采用本技术实施例任一项提供的p逻辑电路,其中的g逻辑电路采用本技术实施例任一项提供的g逻辑电路。

103、虽然本技术所揭露的实施方式如上,但所述的内容仅为便于理解本技术而采用的实施方式,并非用以限定本技术。任何本技术所属领域内的技术人员,在不脱离本技术所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本技术的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

- 还没有人留言评论。精彩留言会获得点赞!