数据处理方法、装置、芯片及交通设备与流程

本技术涉及数据处理技术,尤其涉及数据处理方法、装置、芯片及交通设备。

背景技术:

1、在多核系统中,通常存在需要在多个处理器之间共享的重要数据,如电机应用的标定数据;该重要数据的数据量不大,但是会被各处理器以较高的频率读取。在多数处理器同时读取该重要数据时,会存在访问冲突,降低处理器的访问效率。

技术实现思路

1、本技术实施例提供一种数据处理方法、装置、芯片及交通设备,能够提高处理器的访问效率。

2、本技术实施例的技术方案是这样实现的:

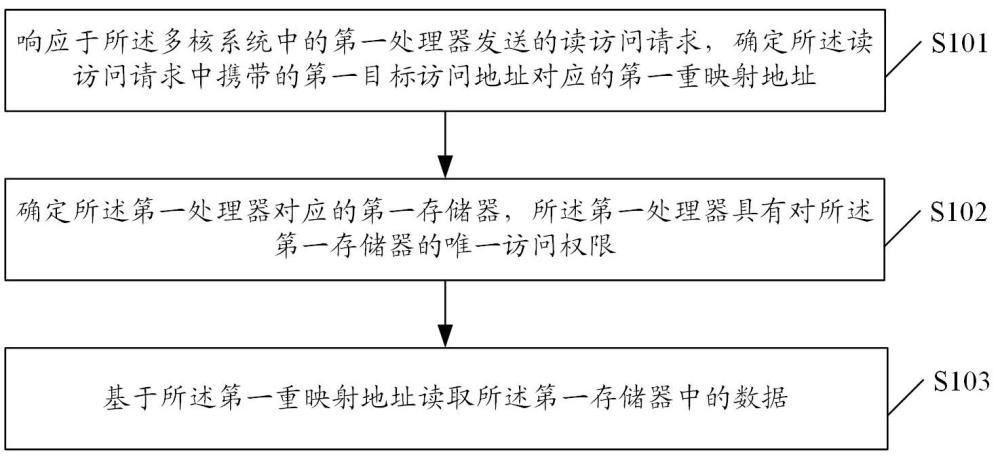

3、第一方面,本技术实施例提供一种数据处理方法,所述方法应用于包括至少两个处理器的多核系统,所述方法包括:响应于所述多核系统中的第一处理器发送的读访问请求,确定所述读访问请求中携带的第一目标访问地址对应的第一重映射地址;确定所述第一处理器对应的第一存储器,所述第一处理器具有对所述第一存储器的唯一访问权限;基于所述第一重映射地址读取所述第一存储器中的数据;其中,所述第一目标访问地址对应于第二存储器,所述第二存储器的访问速度小于所述第一存储器的访问速度。

4、在一些可选实施例中,所述确定所述读访问请求中携带的第一目标访问地址对应的第一重映射地址,包括:

5、基于所述读访问请求确定待读取数据对应的第一存储区域大小;

6、基于所述第一目标访问地址和所述第一存储区域大小,确定所述第一重映射地址。

7、在一些可选实施例中,所述基于所述第一重映射地址读取所述第一存储器中的数据,包括:

8、在所述第一存储器中读取所述第一重映射地址存储的数据。

9、在一些可选实施例中,所述基于所述第一重映射地址读取所述第一存储器中的数据,包括:

10、基于所述读访问请求确定待读取数据对应的第一存储区域大小;

11、以所述第一重映射地址作为第一起始地址,基于所述第一起始地址和所述第一存储区域大小确定第一目标地址;所述第一目标地址与所述第一起始地址之间存储的数据大小等于所述第一存储区域大小;

12、在所述第一存储器中读取所述第一起始地址与所述第一目标地址之间存储的数据。

13、在一些可选实施例中,所述确定所述第一处理器对应的第一存储器包括:

14、在所述多核系统的第一寄存器中,查找所述第一处理器具有唯一访问权限的第一存储器。

15、在一些可选实施例中,所述方法还包括:响应于所述第一处理器发送的写访问请求,确定所述写访问请求中携带的第二目标访问地址对应的第二重映射地址;

16、基于所述第二重映射地址将待写入数据写入所述多核系统对应的全部第一存储器;

17、其中,所述多核系统中的每个所述处理器分别对应一个第一存储器,每个所述处理器具有对所述处理器对应的第一存储器的唯一访问权限。

18、在一些可选实施例中,所述确定所述写访问请求中携带的第二目标访问地址对应的第二重映射地址,包括:

19、基于所述写访问请求确定待写入数据对应的第二存储区域大小;

20、基于所述第二目标访问地址和所述第二存储区域大小,确定所述第二重映射地址。

21、在一些可选实施例中,所述基于所述第二重映射地址将待写入数据写入所述多核系统对应的全部第一存储器,包括:

22、将所述待写入数据写入所述多核系统对应的每个第一存储器中的所述第二重映射地址。

23、在一些可选实施例中,所述基于所述第二重映射地址将待写入数据写入所述多核系统对应的全部第一存储器,包括:

24、基于所述写访问请求确定待写入数据对应的第二存储区域大小;

25、以所述第二重映射地址作为第二起始地址,基于所述第二起始地址和所述第二存储区域大小确定第二目标地址;所述第二目标地址与所述第二起始地址之间存储的数据大小等于所述第二存储区域大小;

26、在所述第二起始地址与所述第二目标地址之间写入所述待写入数据。

27、第二方面,本技术实施例提供一种数据处理装置,所述装置包括:第一确定模块,用于响应于多核系统中的第一处理器发送的读访问请求,确定所述读访问请求中携带的第一目标访问地址对应的第一重映射地址;

28、第二确定模块,用于确定所述第一处理器对应的第一存储器,所述第一处理器具有对所述第一存储器的唯一访问权限;

29、读取模块,用于基于所述第一重映射地址读取所述第一存储器中的数据;

30、其中,所述第一目标访问地址对应于第二存储器,所述第二存储器的访问速度小于所述第一存储器的访问速度。

31、在一些可选实施例中,所述第一确定模块,用于基于所述读访问请求确定待读取数据对应的第一存储区域大小;

32、基于所述第一目标访问地址和所述第一存储区域大小,确定所述第一重映射地址。

33、在一些可选实施例中,所述读取模块,用于在所述第一存储器中读取所述第一重映射地址存储的数据。

34、在一些可选实施例中,所述读取模块,用于基于所述读访问请求确定待读取数据对应的第一存储区域大小;

35、以所述第一重映射地址作为第一起始地址,基于所述第一起始地址和所述第一存储区域大小确定第一目标地址;所述第一目标地址与所述第一起始地址之间存储的数据大小等于所述第一存储区域大小;

36、在所述第一存储器中读取所述第一起始地址与所述第一目标地址之间存储的数据。

37、在一些可选实施例中,所述第二确定模块,用于在所述多核系统的第一寄存器中,查找所述第一处理器具有唯一访问权限的第一存储器。

38、在一些可选实施例中,所述数据处理装置还包括:处理模块,用于响应于所述第一处理器发送的写访问请求,确定所述写访问请求中携带的第二目标访问地址对应的第二重映射地址;

39、基于所述第二重映射地址将待写入数据写入所述多核系统对应的全部第一存储器;

40、其中,所述多核系统中的每个所述处理器分别对应一个第一存储器,每个所述处理器具有对所述处理器对应的第一存储器的唯一访问权限。

41、在一些可选实施例中,所述处理模块,用于基于所述写访问请求确定待写入数据对应的第二存储区域大小;

42、基于所述第二目标访问地址和所述第二存储区域大小,确定所述第二重映射地址。

43、在一些可选实施例中,所述处理模块,用于将所述待写入数据写入所述多核系统对应的每个第一存储器中的所述第二重映射地址。

44、在一些可选实施例中,所述处理模块,用于基于所述写访问请求确定待写入数据对应的第二存储区域大小;

45、以所述第二重映射地址作为第二起始地址,基于所述第二起始地址和所述第二存储区域大小确定第二目标地址;所述第二目标地址与所述第二起始地址之间存储的数据大小等于所述第二存储区域大小;

46、在所述第二起始地址与所述第二目标地址之间写入所述待写入数据。

47、第三方面,本技术实施例提供一种芯片,所述芯片包括至少一个处理器;以及与所述至少一个处理器通信连接的存储器;其中,

48、所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够实现上述的方法。

49、第四方面,本技术实施例提供一种交通设备上的部件,所述部件包括芯片,所述芯片能够执行本技术实施例提供的方法。

50、第五方面,本技术实施例提供一种交通设备,所述交通设备包括芯片,所述芯片能够执行本技术实施例提供的方法。

51、第六方面,本技术实施例提供一种计算机存储介质,存储有可执行指令,用于被处理器执行时,实现上述的方法。

52、本技术实施例提供的数据处理方法,所述方法应用于包括至少两个处理器的多核系统,所述方法包括:响应于所述多核系统中的第一处理器发送的读访问请求,确定所述读访问请求中携带的第一目标访问地址对应的第一重映射地址;确定所述第一处理器对应的第一存储器,所述第一处理器具有对所述第一存储器的唯一访问权限;基于所述第一重映射地址读取所述第一存储器中的数据;其中,所述第一目标访问地址对应于第二存储器,所述第二存储器的访问速度小于所述第一存储器的访问速度。由于多核系统中的第一处理器具有对所述第一存储器的唯一访问权限,即第一处理器仅能够访问与第一处理器对应的第一存储器,第一存储器仅能够被与第一存储器对应的第一处理器访问,因此,在多核系统中的多个处理器同时访问同一个数据时,在同一时刻每个处理器均在各自对应的第一存储器中读取数据;避免在同一时刻多个处理器需要读取同一个数据的场景下,只能一个处理器读取数据,其他处理器在队列中等待的情况,提高了数据访问的速度和数据访问的效率。

- 还没有人留言评论。精彩留言会获得点赞!