一种缓存数据处理方法、缓存控制器、芯片及电子设备与流程

本公开涉及计算机,尤其涉及一种缓存数据处理方法、缓存控制器、芯片及电子设备。

背景技术:

1、cache即缓存,其保存的内容是下游存储器中的一个子集,cpu/gpu 等其他访问设备访问下游存储器时会先在cache中检索,如果在cache中命中,则直接在该cache中进行读写操作,如果在cache中未命中再从下游存储器中读取数据。采用这方式减少了访问下游存储器的次数,从而提升传输性能。

2、目前,在需要将cache中的数据写回至下游存储器时,通常是以cacheline即缓存行为最小单位进行写回,即在需要写回时会写回整个cacheline。 采用这种方式会产生多余的写,进而导致带宽的浪费。

技术实现思路

1、本公开的目的是提供一种缓存数据处理方法、缓存控制器、芯片及电子设备。

2、根据本公开的第一个方面,提供一种缓存数据处理方法,所述缓存中包括若干缓存行,任一缓存行存储有:若干数据块、用于标识每个数据块是否有效的数据块有效标识以及用于标识每个数据块是否为脏数据的数据块脏标识;所述方法包括:

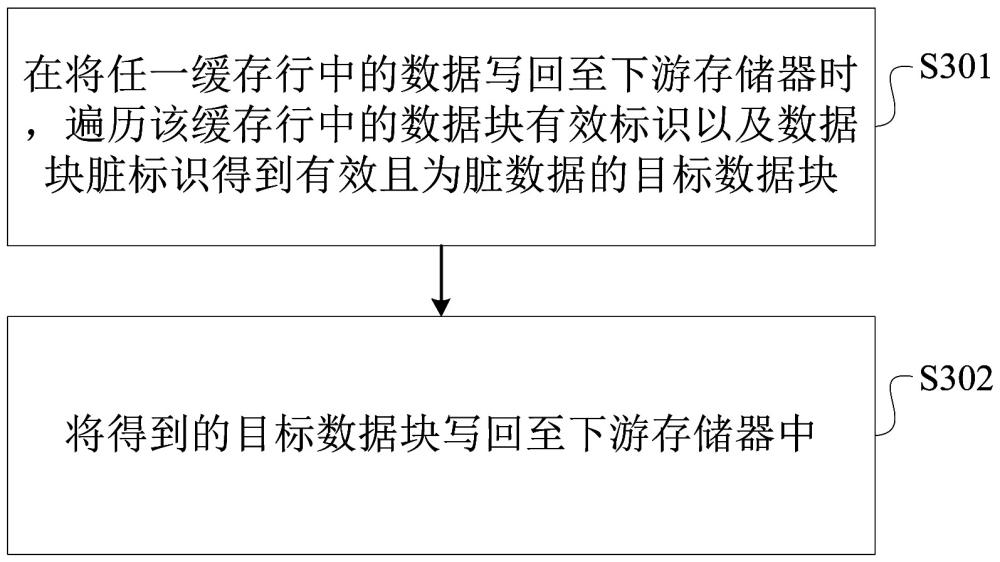

3、在将任一缓存行中的数据写回至下游存储器时,遍历所述缓存行中的数据块有效标识以及数据块脏标识得到有效且为脏数据的目标数据块;

4、将得到的目标数据块写回至下游存储器中。

5、在一种实施方式中,所述将任一缓存行中的数据写回至下游存储器,包括:

6、在检测到下游存储器空闲时,确定将所述缓存中的每个缓存行中的数据写回至下游存储器。

7、在一种实施方式中,所述将任一缓存行中的数据写回至下游存储器,包括:

8、在接收到写请求后,若所述写请求未命中所述缓存中的任一缓存行,且所述缓存中没有空闲缓存行,则确定从所述缓存中确定目标缓存行,将所述目标缓存行中的数据写回至下游存储器。

9、在一种实施方式中,将所述目标缓存行中的数据写回至下游存储器后,还包括:

10、将所述写请求携带的至少一个数据块写入至所述目标缓存行中,将所述数据块有效标识和数据块脏标识修改为用于标识所述至少一个数据块为有效且为脏数据的数据块。

11、在一种实施方式中,所述缓存与下游存储器的映射方式为组相联映射,所述缓存中包括若干组,任一组中包括若干缓存行;所述从所述缓存中确定目标缓存行包括:

12、确定所述写请求命中的组,遍历所述组中各个缓存行中的数据块有效标识以及数据块脏标识,确定所述组中包括目标数据块最多的缓存行为目标缓存行,其中目标数据块为有效且为脏数据的数据块。

13、在一种实施方式中,该方法还包括:

14、在接收到写请求后,若所述写请求命中缓存中的任一缓存行,或者,所述写请求未命中缓存中的任一缓存行且所述缓存中存在可处理所述写请求的空闲缓存行,则将所述写请求携带的至少一个数据块写入至缓存行中,并将数据块有效标识和数据块脏标识修改为用于标识该被写入的数据块为有效且为脏数据的数据块。

15、在一种实施方式中,该方法还包括:

16、在接收到读请求后,在所述读请求命中缓存中的任一缓存行的情况下,根据数据块有效标识和数据块脏标识确定所述读请求需要读取的数据块是否均在所述缓存行中,若是,则从被命中的缓存行中读取所述读请求对应的数据块返回给所述读请求的发起方;

17、若否,则针对读请求对应的、未在所述缓存行中的数据块生成读命令发送至下游存储器,并从被命中的缓存行中读取所述读请求对应的、在所述缓存行中的数据块返回给所述读请求的发起方。

18、在一种实施方式中,该方法还包括:

19、在接收到读请求后,若所述读请求未命中缓存中的任一缓存行,则将所述读请求发送至下游存储器,以使下游存储器将所述读请求对应的数据块返回给所述读请求的发起方。

20、在一种实施方式中,所述任一缓存行被配置为存储若干数据块、用于标识每个数据块是否有效的数据块有效标识、以及用于标识每个数据块是否为脏数据的数据块脏标识,包括:

21、任一缓存行中存储有若干数据块,针对每个数据块分别配置有一个数据块有效标识以及一个数据块脏标识。

22、根据本公开的第二个方面,提供一种缓存控制器,用于对缓存进行控制,所述缓存中包括若干缓存行,任一缓存行存储有:若干数据块、用于标识每个数据块是否有效的数据块有效标识以及用于标识每个数据块是否为脏数据的数据块脏标识;所述缓存控制器包括:

23、遍历模块,用于在将任一缓存行中的数据写回至下游存储器时,遍历所述缓存行中的数据块有效标识以及数据块脏标识得到有效且为脏数据的目标数据块;

24、写回模块,用于将得到的目标数据块写回至下游存储器中。

25、在一种实施方式中,所述写回模块,具体用于在检测到下游存储器空闲时,确定将所述缓存中的每个缓存行中的数据写回至下游存储器。

26、在一种实施方式中,所述写回模块,具体用于在接收到写请求后,若所述写请求未命中所述缓存中的任一缓存行,且所述缓存中没有空闲缓存行,则确定从所述缓存中确定目标缓存行,将所述目标缓存行中的数据写回至下游存储器。

27、在一种实施方式中,所述缓存控制器还包括:

28、写入模块,用于将所述写请求携带的至少一个数据块写入至所述目标缓存行中,将所述数据块有效标识和数据块脏标识修改为用于标识所述至少一个数据块为有效且为脏数据的数据块。

29、在一种实施方式中,所述缓存与下游存储器的映射方式为组相联映射,所述缓存中包括若干组,任一组中包括若干缓存行;

30、所述写回模块,具体用于确定所述写请求命中的组,遍历所述组中各个缓存行中的数据块有效标识以及数据块脏标识,确定所述组中包括目标数据块最多的缓存行为目标缓存行,其中目标数据块为有效且为脏数据的数据块。

31、在一种实施方式中,所述缓存控制器还包括:

32、写入模块,用于在接收到写请求后,若所述写请求命中缓存中的任一缓存行,或者,所述写请求未命中缓存中的任一缓存行且所述缓存中存在可处理所述写请求的空闲缓存行,则将所述写请求携带的至少一个数据块写入至缓存行中,并将数据块有效标识和数据块脏标识修改为用于标识该被写入的数据块为有效且为脏数据的数据块。

33、在一种实施方式中,所述缓存控制器还包括:

34、读取模块,用于在接收到读请求后,在所述读请求命中缓存中的任一缓存行的情况下,根据数据块有效标识和数据块脏标识确定所述读请求需要读取的数据块是否均在所述缓存行中,若是,则从被命中的缓存行中读取所述读请求对应的数据块返回给所述读请求的发起方;

35、若否,则针对读请求对应的、未在所述缓存行中的数据块生成读命令发送至下游存储器,并从被命中的缓存行中读取所述读请求对应的、在所述缓存行中的数据块返回给所述读请求的发起方。

36、在一种实施方式中,所述读取模块,还用于在接收到读请求后,若所述读请求未命中缓存中的任一缓存行,则将所述读请求发送至下游存储器,以使下游存储器将所述读请求对应的数据块返回给所述读请求的发起方。

37、根据本公开的第三个方面,提供一种芯片,包括第二个方面中任一实施方式中的缓存控制器。

38、根据本公开的第四个方面,提供一种电子设备,包括第三个方面的芯片。

39、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!