一种高可靠、免拆卸的FPGA程序在线更新方法与流程

本技术实施例涉及电子电路,特别涉及一种高可靠、免拆卸的fpga程序在线更新方法。

背景技术:

1、随着现代军事领域、民用领域对雷达性能要求的不断提高以及数字处理技术和数字处理硬件的日益成熟,数字阵列雷达的应用也愈发广泛。数字前端是数字阵列雷达的重要组成部分,数字前端的性能对雷达的总体性能起到至关重要的最用。再在雷达整机的调试中,需要不断地微调数字前端的各种参数,即需要多次更新数字前端的fpga(fieldprogrammable gate array,现场可编程逻辑门阵列)程序。随着数字阵列雷达规模的不断增大,数字前端的通道数不也断增多,数字前端中的fpga芯片数量也随之愈发增多。

2、传统的数字前端的fpga程序更新流程需要从编程接口下载程序更新文件,使用电缆通过编程接口将数字前端连接至pc机,启动专用编程软件完成更新,每片fpga每次更新大约需要6至7分钟。大规模数字阵列的数字前端的fpga可达几百片并且更新是串行的,这导致程序更新需耗费数十小时。由于散热和总体结构设计要求,每片fpga的编程口在总站上一般是不可接触的,每次程序更新时需要进行数字前端的拆装,这导致每次程序更新所需时间高达72小时以上,并且拆装过程中会因不可控因素发生非预期结果。

技术实现思路

1、本技术实施例的目的在于提供一种高可靠、免拆卸的fpga程序在线更新方法,可以在不进行数字前端整体结构拆装的情况下,快捷、稳定、安全、可靠地完成数字前端的fpga程序更新,为雷达性能指标的调试达成提供了有力支撑。

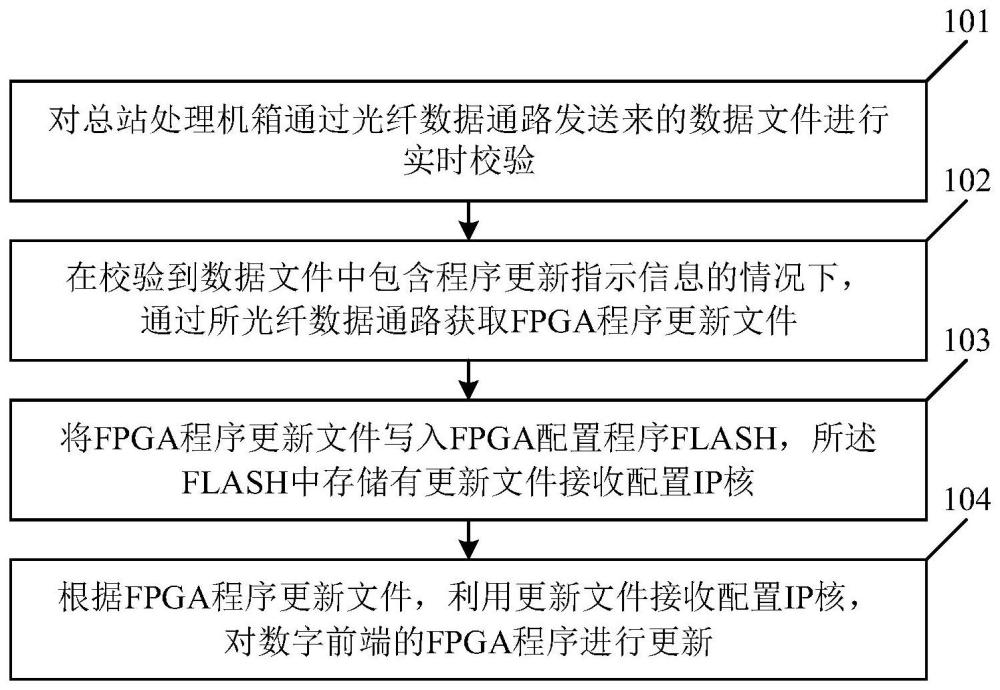

2、为解决上述技术问题,本技术的实施例提供了一种高可靠、免拆卸的fpga程序在线更新方法,应用于雷达的数字前端,适用于对所述数字前端的fpga程序进行更新,所述数字前端与总站处理机箱之间建立有光纤数据通路,所述方法包括以下步骤:对所述总站处理机箱通过所述光纤数据通路发送来的数据文件进行实时校验;在校验到所述数据文件中包含程序更新指示信息的情况下,通过所述光纤数据通路获取fpga程序更新文件;将所述fpga程序更新文件写入fpga配置程序flash;其中,所述flash中存储有更新文件接收配置ip核;根据所述fpga程序更新文件,利用所述更新文件接收配置ip核,对所述数字前端的fpga程序进行更新。

3、本技术的实施例还提供了一种高可靠、免拆卸的fpga程序在线更新系统,所述系统包括:装载在雷达上的数字前端、总站处理机箱和中心控制计算机,所述数字前端与所述总站处理机箱之间均建立有光纤数据通路;所述中心控制计算机用于根据更新需求生成fpga程序更新文件,并将所述fpga程序更新文件发送至所述总站处理机箱;所述总站处理机箱通过所述光纤数据通路向所述数字前端发送携带有程序更新指示信息的数据文件;所述数字前端在收到所述携带有程序更新指示信息的数据文件后,通过所述光纤数据通路获取fpga程序更新文件,将所述fpga程序更新文件写入fpga配置程序flash,并根据所述fpga程序更新文件,利用所述flash中存储的更新文件接收配置ip核,对所述数字前端的fpga程序进行更新。

4、本技术的实施例还提供了一种电子设备,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器中存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行上述的一种高可靠、免拆卸的fpga程序在线更新方法。

5、本技术的实施例还提供了一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时实现上述的一种高可靠、免拆卸的fpga程序在线更新方法。

6、本技术的实施例提供的一种高可靠、免拆卸的fpga程序在线更新方法,利用雷达的数字前端已有的与总站处理机箱之间建立的光纤数据通路接收fpga程序更新文件,由数字前端的fpga配置程序flash中存储的更新文件接收配置ip核执行fpga程序更新,数字前端与总站均不需要进行硬件结构改动,fpga程序更新的全过程不需要进行数字前端整体结构的拆卸和装载,避免了拆卸和装载过程中因不可控因素发生的非预期结果,同时实现了数字前端中所有fpga程序更新的并行进行,数字前端的fpga程序更新完成仅需20分钟,远低于拆卸数字前端进行更新所需的72小时的更新时间,大幅提高了数字前端的fpga程序更新的效率。整个fpga程序更新的过程高度自动化,节约了人力成本以及宝贵的雷达调试时间,能够快捷、稳定、安全、可靠地完成数字前端的fpga程序更新,为雷达性能指标的调试达成提供了有力支撑。

7、在一些可选的实施例中,所述flash中设置有第一区和第二区,所述第一区中存储有一个更新文件接收配置ip核,所述第二区存储有一个更新文件接收配置ip核和数字前端工作配置文件,所述将所述fpga程序更新文件写入fpga配置程序flash,包括:默认将所述fpga程序更新文件写入所述第二区;根据所述fpga程序更新文件,利用所述第二区的更新文件接收配置ip核,对所述第二区存储的所述数字前端工作配置文件进行更新;检测所述数字前端工作配置文件是否更新成功;在检测到所述数字前端工作配置文件更新失败的情况下,通过所述光纤数据通路重新获取所述fpga程序更新文件,并将所述fpga程序更新文件写入所述第二区;根据所述fpga程序更新文件,利用所述第一区的更新文件接收配置ip核,对所述第二区存储的所述数字前端工作配置文件和所述第二区的更新文件接收配置ip核进行更新。flash的第一区作为第二区的紧急备份,正常情况下由第二区存储的更新文件接收配置ip核执行fpga程序更新,如果第二区因某些不可测原因导致更新失败,则数字前端重新从总站处理机箱处获取fpga程序更新文件,由第一区存储的更新文件接收配置ip核执行fpga程序更新,并对第二区的更新文件接收配置ip核进行更新,使得第二区的更新文件接收配置ip核在后续工作中可以正常运行,因第一区的存在,fpga程序更新失败后仍可进行继续更新工作,进一步提升了fpga程序更新的安全性、可靠性。

8、在一些可选的实施例中,所述在检测到所述数字前端工作配置文件更新失败的情况下,通过所述光纤数据通路重新获取所述fpga程序更新文件,并将所述fpga程序更新文件写入所述第二区,包括;在检测到所述数字前端工作配置文件更新失败的情况下,通过所述光纤数据通路向所述总站处理机箱发送重新更新请求信息;通过所述光纤数据通路重新获取所述fpga程序更新文件,并将所述fpga程序更新文件写入所述第二区;其中,所述总站处理机箱在收到所述数字前端通过所述光纤数据通路发送来的所述重新更新请求信息后,通过所述光纤数据通路再次向所述数字前端发送所述fpga程序更新文件。在正常情况下,总站只向数字前端发送一次fpga程序更新文件,总站不知道数字前端的fpga程序是否更新成功,本技术设置数字前端在使用第二区的更新文件接收配置ip核更新fpga程序失败后,向总站发送重新更新请求信息,以便再次获取到fpga程序更新文件,排除因上次接收到的fpga程序更新文件不完整导致更新失败的情况。

9、在一些可选的实施例中,在所述根据所述fpga程序更新文件,利用所述第一区的更新文件接收配置ip核,对所述第二区存储的所述数字前端工作配置文件和所述第二区的更新文件接收配置ip核进行更新之后,所述方法包括:再次检测所述数字前端工作配置文件是否更新成功;在检测到所述数字前端工作配置文件更新失败的情况下,将所述数字前端从所述雷达上拆卸下来,通过下载电缆和所述数字前端的编程接口将所述数字前端连接至pc机;根据所述fpga程序更新文件,使用所述pc机上安装的编程软件对所述数字前端的fpga程序进行更新;在所述数字前端的fpga程序更新完成后,重新将所述数字前端装载在所述雷达上。如果第一区的更新文件接收配置ip核更新fpga程序也失败,则需要通过拆卸和装载数字前端的方式进行fpga程序更新,保证fpga程序最终成功更新。

10、在一些可选的实施例中,所述第一区中存储的更新文件接收配置ip核不会被更新。第一区中存储的更新文件接收配置ip核永远作为第二区的更新备份,可以保证更新通路通畅。

11、在一些可选的实施例中,所述在校验到所述数据文件中包含程序更新指示信息的情况下,通过所述光纤数据通路获取fpga程序更新文件,包括:在校验到所述数据文件中包含程序更新指示信息的情况下,检测所述数字前端的fpga程序的当前版本是否低于所述程序更新指示信息对应的fpga程序的版本;若所述当前版本低于所述程序更新指示信息对应的fpga程序的版本,则通过所述光纤数据通路获取fpga程序更新文件;若所述当前版本不低于所述程序更新指示信息对应的fpga程序的版本,则忽略所述程序更新指示信息。总站面对多个雷达的数字前端,不同的雷达的数字前端的fpga程序的版本可能不同,对于一次fpga程序更新,某些数字前端的fpga程序可能早已更新完成,因此数字前端在校验程序更新指示信息时还要对版本进行校验,只在当前版本低于程序更新指示信息对应的fpga程序的版本时进行更新,避免获取冗余数据。

12、在一些可选的实施例中,在所述再次检测所述数字前端工作配置文件是否更新成功之后,所述方法还包括:在检测到所述数字前端工作配置文件更新成功的情况下,通过所述光纤数据通路向所述总站处理机箱发送fpga程序更新成功信息。

- 还没有人留言评论。精彩留言会获得点赞!