一种实现FPGA虚拟输入/输出模块的布局布线方法及装置与流程

本技术涉及但不限于数字电路设计和集成电路设计技术,尤指一种实现fpga虚拟输入/输出模块的布局布线方法及装置。

背景技术:

1、现场可编程门阵列(fpga,field-programmable gate array)软件工具的开发过程主要包括逻辑综合、布局、布线、时序分析和码流的生成等环节。

2、fpga虚拟输入/输出模块(vio)是工具,用于实时监控和驱动fpga内部信号。fpgavio通常用于调试、验证和测试fpga设计,允许工程师在运行时检查和控制fpga内部的信号,而无需重新编译代码或重新配置fpga。通过fpga vio,工程师可以监视内部信号的状态,比如观察寄存器、内部总线或其他逻辑单元的值;修改内部信号的值,允许工程师动态地改变设计的行为,而无需重新合成和实现;收集和记录信号的数据,以便分析和故障排除。这些功能对于调试复杂的fpga设计尤其有用,可以大大缩短调试周期,并帮助工程师更快地发现和解决问题。

3、fpga vio的设计有助于提高用户的设计效率和调试能力。fpga vio的输入端口用于监控用户配置的fpga信号,即可以将fpga内部信号映射到fpga vio的输入端口,从而实时监视这些信号的状态;fpga vio的输出端口用于驱动用户配置的fpga信号,即可以通过fpga vio的输出端口修改这些信号的值,以驱动fpga内部的逻辑和状态。这种功能在故障重现场景中尤其有用,因为用户可以忽略外部设备(如按键、led灯等)对fpga信号的影响,专注于检查和修改内部信号的行为。这样,用户就可以更轻松地重现和调试特定的故障情况,而无需受到外部环境的干扰。总的来说,fpga vio为fpga设计人员提供了一种强大的工具,可以帮助他们更有效地开发、调试和验证复杂的fpga设计。

4、fpga vio的原理大致如下:首先,用户在fpga开发环境中设计fpga vio,并将其与待测试的fpga设计结合,这包括将fpga vio与fpga设计进行综合(将用户的设计转换为底层逻辑元件)和布局布线(在fpga芯片上分配逻辑资源和建立物理连接)。接着,完成综合和布局布线后,生成了一个包含用户设计的完整位流(bitstream)以实现码流下载,这个位流文件包含了将用户设计加载到fpga芯片上所需的所有信息。之后,用户将生成的位流文件下载到目标fpga芯片中以将用户设计的fpga vio的信息下载到fpga芯片中,比如可以通过fpga开发板上的下载接口(如jtag)完成。然后,用户通过上位机与fpga芯片建立通信连接,通常通过串口、以太网或其他通信接口,这里,上位机负责向fpga发送控制指令,并接收来自fpga的数据。一旦建立了通信连接,fpga vio即可以通过上位机实时驱动用户设置的信号,并且可以将实时捕获的信号数据传输回上位机进行显示和分析。通过这种方式,用户可以利用上位机界面实时监控和控制fpga内部的信号,从而加快调试和验证的过程。

5、相关技术中,fpga vio的布局布线方式是将fpga vio与用户设计一起综合后生成融合网表文件,然后按照融合网表文件的信息进行布局布线,最后生成带有fpga vio配置信息的码流文件。这种方法的优势在于,可以保证用户选择的信号不会出现被优化掉的情况。但是,这种方法会导致fpga vio占用资源的连接关系,这样的话,当用户设计中去掉fpga vio对用户设计生成网表文件时,会改变综合产生的融合网表文件的信息,从而导致不使用fpga vio的用户设计的布局布线结果和使用fpga vio时的不一致,这可能导致调试和验证过程中的混乱和困惑,从而降低加快调试和验证的效率。同时,fpga vio的增加可能会导致布局布线结果不满足时序要求,因为资源被占用后,布局布线工具在满足时序约束时可能会受到限制,从而影响设计的性能和稳定性。

技术实现思路

1、本技术提供一种实现fpga虚拟输入/输出模块的布局布线方法及装置,能够提升调试和验证的效率,提高设计的性能和稳定性。

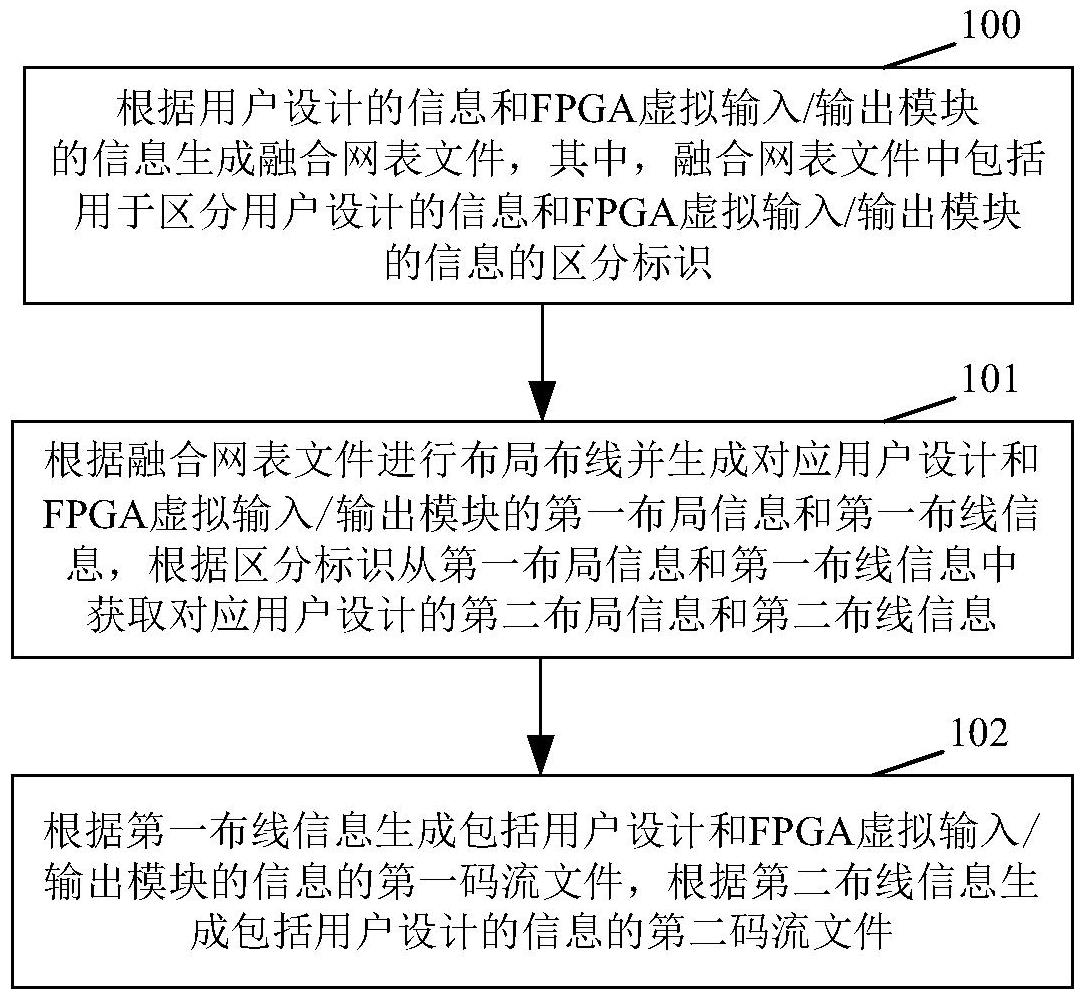

2、本发明实施例提供了一种实现fpga虚拟输入/输出模块的布局布线方法,包括:

3、根据用户设计的信息和现场可编程门阵列fpga虚拟输入/输出模块的信息生成融合网表文件,其中,融合网表文件中包括用于区分用户设计的信息和fpga虚拟输入/输出模块的信息的区分标识;

4、根据融合网表文件进行布局布线并生成对应用户设计和fpga虚拟输入/输出模块的第一布局信息和第一布线信息,根据区分标识分别从第一布局信息和第一布线信息中获取对应用户设计的第二布局信息和第二布线信息;

5、根据第一布线信息生成包括用户设计和fpga虚拟输入/输出模块的信息的第一码流文件,根据第二布线信息生成包括用户设计的信息的第二码流文件。

6、在一种示例性实例中,所述根据融合网表文件进行布局布线并生成对应用户设计和fpga虚拟输入/输出模块的第一布局信息和第一布线信息,根据区分标识分别从第一布局信息和第一布线信息中获取对应用户设计的第二布局信息和第二布线信息,包括:

7、对生成的所述融合网表文件进行解析得到用于布局的用户设计和fpga虚拟输入/输出模块的资源;

8、根据解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源进行布局并生成所述第一布局信息,根据所述区分标识从所述第一布局信息中获取对应用户设计的所述第二布局信息;

9、根据解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线并生成所述第一布线信息,根据所述区分标识从所述第一布线信息中获取对应用户设计的所述第二布线信息。

10、在一种示例性实例中,在所述布线完成后,对于出现布线失败的情况,还包括:

11、根据布线失败信息对所述布局中对应布线失败的位置进行约束并生成二次布局约束信息;

12、返回所述进行布局的步骤继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源重新进行布局以生成新的第一布局信息并更新所述第一布局信息。

13、在一种示例性实例中,在所述布线完成后,对于时序不满足要求的情况,还包括:

14、根据路径延迟信息对不满足时序要求的布线信息进行约束并生成二次布线约束信息;

15、返回所述进行布线的步骤继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线以生成新的第一布线信息并更新所述第一布线信息。

16、在一种示例性实例中,在所述布线完成后,对于时序不满足要求的情况,还包括:

17、根据路径延迟信息对不满足时序要求以及虽满足时序要求但路径延迟大于预设阈值的布线信息进行约束并生成二次布线约束信息;

18、返回所述进行布线的步骤继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线以生成新的第一布线信息并更新所述第一布线信息。

19、本技术实施例还提供一种计算机可读存储介质,存储有计算机可执行指令,所述计算机可执行指令用于执行上述任一项所述实现fpga虚拟输入/输出模块的布局布线方法。

20、本技术实施例再提供一种计算机设备,包括存储器和处理器,其中,存储器中存储有以下可被处理器执行的指令:用于执行上述任一项所述实现fpga虚拟输入/输出模块的布局布线方法的步骤。

21、本技术实施例又提供一种实现fpga虚拟输入/输出模块的布局布线装置,包括:融合模块、处理模块、生成模块;其中,

22、融合模块,用于根据用户设计的信息和fpga虚拟输入/输出模块的信息生成融合网表文件,其中,融合网表文件中包括用于区分用户设计的信息和fpga虚拟输入/输出模块的信息的区分标识;

23、处理模块,用于根据融合网表文件进行布局布线并生成对应用户设计和fpga虚拟输入/输出模块的第一布局信息和第一布线信息,根据区分标识分别从第一布局信息和第一布线信息中获取对应用户设计的第二布局信息和第二布线信息;

24、生成模块,用于根据第一布线信息生成包括用户设计和fpga虚拟输入/输出模块的信息的第一码流文件,根据第二布线信息生成包括用户设计的信息的第二码流文件。

25、在一种示例性实例中,所述处理模块包括:解析模块、布局模块和布线模块;其中,

26、解析模块,用于对生成的所述融合网表文件进行解析得到用于布局的用户设计和fpga虚拟输入/输出模块的资源;

27、布局模块,用于根据解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源进行布局并生成所述第一布局信息,根据所述区分标识从所述第一布局信息中获取对应用户设计的所述第二布局信息;

28、布线模块,用于根据解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线并生成所述第一布线信息,根据所述区分标识从所述第一布线信息中获取对应用户设计的所述第二布线信息。

29、在一种示例性实例中,所述布线模块还用于:在布线完成后,对于出现布线失败的情况,根据布线失败信息对布局中对应布线失败的位置进行约束并生成二次布局约束信息;将二次布局约束信息反馈给所述布局模块;相应地,

30、所述布局模块还用于:返回所述进行布局的过程继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源重新进行布局以生成新的第一布局信息并更新所述第一布局信息。

31、在一种示例性实例中,所述布线模块还用于:

32、在布线完成后,对于时序不满足要求的情况,根据路径延迟信息对不满足时序要求的布线信息进行约束并生成二次布线约束信息;返回所述进行布线的过程继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线以生成新的第一布线信息并更新所述第一布线信息。

33、在一种示例性实例中,所述布线模块还用于:

34、在布线完成后,对于时序不满足要求的情况,根据路径延迟信息对不满足时序要求以及虽满足时序要求但路径延迟大于预设阈值的布线信息进行约束并生成二次布线约束信息;返回所述进行布线的过程继续执行,并根据二次布局约束信息、以及所述解析得到的用于布局的用户设计和fpga虚拟输入/输出模块的资源和所述第一布局信息进行布线以生成新的第一布线信息并更新所述第一布线信息。

35、本技术实施例提供的实现fpga虚拟输入/输出模块的布局布线方法,生成了带有fpga虚拟输入/输出模块的信息的码流和不带有fpga虚拟输入/输出模块的信息的两个码流文件,两个码流文件中关于用户设计的布局布线结果是完全一致,既保证了用户在调试完成,去掉fpga虚拟输入/输出模块后,用户设计的布局布线结果与调试过程中完全一致,提升调试和验证的效率,为后续进行故障重现以及故障定位提供了方便,提高了设计的性能和稳定性;又保证了加入fpga虚拟输入/输出模块的信息的布局布线结果满足时序条件,有助于用户故障重现以及快速故障定位,极大提高了用户的设计效率。

36、本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!