芯片、通信方法及通信系统与流程

本技术涉及芯片,更具体而言,涉及到一种芯片、通信方法及通信系统。

背景技术:

1、一方面,由于改进式集成电路总线(improved inter-integrated circuit,i3c)具有较快的通信速度(12.5mhz),为实现高速通信,需满足严格的时序要求,尤其是scl输入到sda输出的时序路径上,有严苛的时序约束条件(mipi协议中称为tsco,最大为12ns)。另一方面,由于不需要额外的中断引脚,又能向下兼容i2c,因此i3c广泛应用于主机挂传感器的多主多从总线拓扑中。但是传感器一般是数模混合芯片,难以采用高端制程,导致在设计上,时序收敛往往变成了一个难点。

技术实现思路

1、本技术实施方式提供一种芯片、通信方法及通信系统。

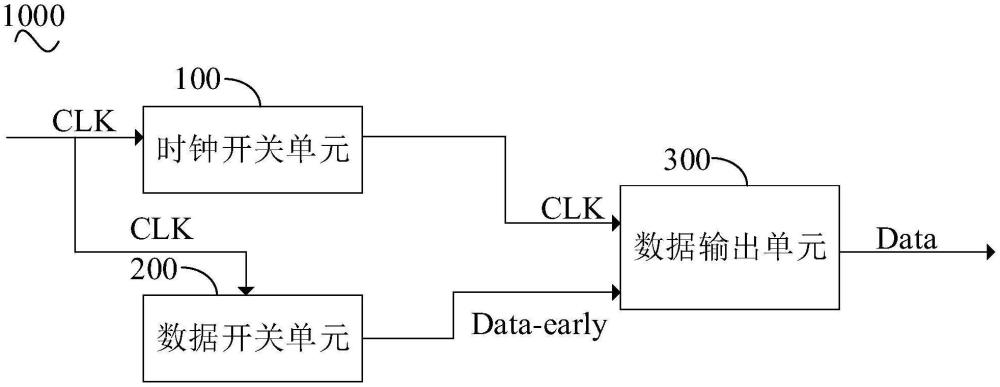

2、本技术实施方式提供的芯片包括时钟开关单元、数据开关单元及数据输出单元。其中,时钟开关单元被配置为获取时钟信号,所述时钟信号包括周期依次出现的第一信号和第二信号。所述数据开关单元被配置为获取所述时钟信号,并在所述第一信号出现时发送数据信号给所述数据输出单元,所述数据输出单元被配置为获取所述时钟信号并在同周期的所述第二信号出现时输出所述数据信号。

3、在本技术实施方式的芯片中,时钟信号包括周期依次出现的第一信号和第二信号,数据开关单元在第一信号出现时就可以发送数据信号,而不用等到第二信号出现时发送数据信号,使得数据输出单元可以提前获取数据信号,并在第二信号出现时立刻输出数据信号,减少了scl输入到sda输出的时序路径延时,改善了芯片的时序收敛。

4、在某些实施方式中,所述第一信号为所述时钟信号的上升沿,所述第二信号为所述时钟信号的下降沿。

5、第一信号和第二信号可以设置为时钟信号的边沿脉冲,边沿脉冲便于数据开关单元和数据输出单元识别采样,以使数据开关单元在第一信号出现时发送数据信号,数据输出单元在第二信号出现时输出数据信号。

6、在某些实施方式中,所述数据开关单元包括触发单元及处理单元,所述触发单元被配置为在所述第一信号出现时将触发信号提供给所述处理单元,所述处理单元被配置为处理所述触发信号以得到所述数据信号。

7、触发单元可以设置为识别第一信号的单元,处理单元可以设置发送数据信号的单元。处理单元可以根据不同的应用场景设置,以便处理单元可以将触发信号处理得到特定的数据信号提供给数据输出单元。

8、在某些实施方式中,所述触发单元包括第一比较器及第一触发器,所述第一比较器包括第一输入端、第二输入端及第一输出端,所述第一输入端与所述第一触发器的输出端连接,所述第二输入端被配置为接入第一基准电压。所述第一触发器被配置为获取所述时钟信号,在所述第一信号出现时将与所述第一信号对应的第一标识电压提供给所述第一输入端,以使所述第一输出端输出所述触发信号。

9、第一触发器可以识别第一信号,第一比较器在第一触发器识别到第一信号时可以提供第一标识电压,以标识第一信号出现的情况。

10、在某些实施方式中,所述时钟开关单元包括第二比较器,所述第二比较器包括第三输入端、第四输入端及第二输出端,所述第三输入端被配置为接入第二基准电压。所述第四输入端被配置为在满足所述时钟信号开启的条件下获取第二标识电压,以使所述第二输出端输出所述时钟信号。

11、第二标识电压可以标识满足时钟信号开启条件的情况,使得第二比较器输出时钟信号。

12、在某些实施方式中,所述数据输出单元包括第二触发器,所述第二触发器包括第五输入端、第六输入端及第三输出端,所述第五输入端被配置为获取所述数据信号,所述第六输入端被配置为获取所述时钟信号,所述第三输出端被配置为输出所述数据信号。所述第二输出端与所述第六输入端连接。

13、基于芯片的应用场景,数字电路上需要设置复杂的逻辑门电路在处理数字信号。第二比较器的第二输出端可以直接和第三触发器的第六输入端连接,即第二比较器可以直接将时钟信号提供给第三触发器的第六输入端,不需要经过数字电路,可以绕开数字电路中的逻辑门电路,减少了scl时效路径的延时。

14、在某些实施方式中,所述数据开关单元被配置为在所述第一信号出现时将使能信号发送给所述数据输出单元。所述数据输出单元被配置为获取所述时钟信号及所述使能信号,并在获取所述使能信号,且同周期的所述第二信号出现时输出所述数据信号。

15、数据输出单元基于使能信号确定输出数据信号,使得sda路径可以提前或持续提供数据信号,降低了对sda路径的时效约束。

16、在某些实施方式中,所述数据开关单元包括第一选择器及第二选择器,所述第一选择器及所述第二选择器的受控端被配置为接入选择信号。在所述选择信号的控制下,所述第一选择器被配置为提供所述数据信号及所述第二选择器被配置为提供所述使能信号,或所述第二选择器被配置为提供所述数据信号。

17、选择信号可以设置数据开关单元的工作模式,使得数据开关单元提供数字信号,或提供数字信号及使能信号。

18、在某些实施方式中,所述数据输出单元包括第三触发器、第四触发器及第三选择器,所述第三触发器被配置为获取所述时钟信号并将所述数据信号发送给所述第三选择器,所述第四触发器被配置为获取所述时钟信号并在同周期的所述第二信号出现时将所述使能信号发送给所述第三选择器,所述第三选择器被配置为在获取所述使能信号的情况下输出所述数据信号。

19、第三触发器可以设置为提前或持续发送数据信号的触发器,第四触发器可以在同周期的所述第二信号出现时发送使能信号。数据输出单元基于使能信号确定输出数据信号,使得sda路径可以提前或持续提供数据信号,降低了对sda路径的时效约束。

20、在某些实施方式中,所述第一信号出现至所述第二信号出现的时刻内,第一设备基于所述芯片向第二设备发送所述数据信号,在同周期的所述第二信号出现至下个周期的所述第一信号出现的时刻内,所述第二设备基于所述芯片向所述第一设备发送所述数据信号。

21、在时钟信号的同一个周期内,可以进行芯片通信总线控制权的交换,提高了芯片的通信效率。

22、在某些实施方式中,所述时钟信号为双沿时钟信号。

23、双沿时钟是指在时钟的上升沿和下降沿均可以传输数据的时钟信号,使得数据的传输效率提高了一倍。

24、本技术实施方式提供的通信方法包括:获取时钟信号,所述时钟信号包括周期依次出现的第一信号和第二信号;获取在所述第一信号出现时发送的数据信号;在同周期的所述第二信号出现时输出所述数据信号。

25、本技术实施方式提供的通信系统包括上述实施方式的芯片及多个通信设备,所述芯片被配置为实现多个所述通信设备之间的通信连接。

26、在本技术实施方式提供的芯片、通信方法及通信系统中,芯片包括时钟开关单元、数据开关单元及数据输出单元。其中,时钟开关单元被配置为获取时钟信号,时钟信号包括周期依次出现的第一信号和第二信号。数据开关单元被配置为获取时钟信号,并在第一信号出现时发送数据信号给数据输出单元,数据输出单元被配置为获取时钟信号并在同周期的第二信号出现时输出数据信号。数据开关单元在第一信号出现时就可以发送数据信号,而不用等到第二信号出现时发送数据信号,使得数据输出单元可以提前获取数据信号,并在第二信号出现时立刻输出数据信号,减少了scl输入到sda输出的时序路径延时,改善了芯片的时序收敛。

27、本技术的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!