基于FPGA的平衡时钟偏斜的电路系统及控制方法与流程

本发明涉及集成电路,特别涉及一种基于fpga的平衡时钟偏斜的电路系统及控制方法。

背景技术:

1、fpga(field programmable gate array,现场可编程门阵列)是在pal(可编程阵列逻辑)、gal(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、随着工艺的深化,fpga器件的逻辑容量规模越来越大,信号走线也越来越复杂,尤其是对fpga在时钟进行布线上产生了巨大的挑战。通常的,fpga核内的模块都需要走专用的时钟布线,从而保证在时钟布线上的每一个点都会有比较小的时钟偏斜(clock skew),然而专用的时钟布线需要很长的时钟路径延时,这便导致时钟源端的寄存器和fpga上的寄存器之间存在较大的时钟偏斜,进而使得寄存器之间的时序违规且难以修复,导致fpga的运行效率较低,从而降低了fpga的性能。

3、为了解决时钟源端的寄存器和fpga上的寄存器之间存在的时钟偏斜,目前通常用锁相环(pll)将时钟源端的源时钟和fpga处的核内源时钟的相位进行纠正,从而减小时钟偏斜;或,采用先入先出(fifo)存储器对数据进行缓存,以弥补时钟偏斜。

4、然而,由于锁相环是模拟电路,面积较大,若对fpga中每一模块设置锁相环,则会导致fpga的面积增大,不利于fpga的小型化设计;另外,锁相环是否能够锁相取决于参考时钟,因此需要额外引入一个参考时钟,这会浪费fpga的输入输出(io)资源。而fifo的使用会加大数据延迟,且当时钟频率存在偏差时会引入误码,从而导致系统混乱。因此,现有的两种解决时钟偏斜的方案都不利于实际应用。

技术实现思路

1、本发明的目的在于提供一种基于fpga的平衡时钟偏斜的电路系统及控制方法,以至少解决如何在不增加fpga硬件资源的同时有效平衡时钟偏斜的问题。

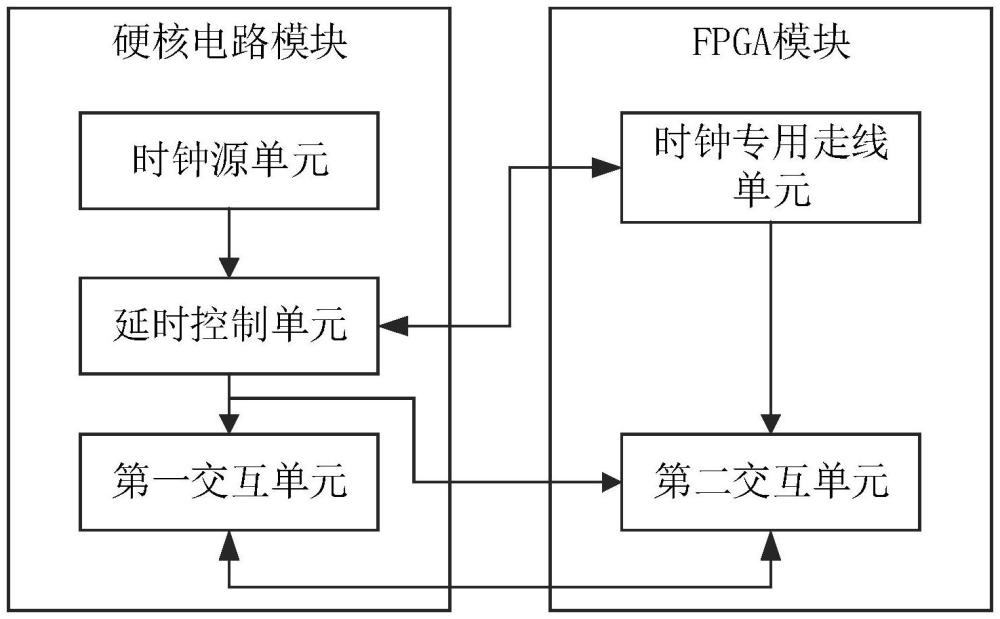

2、为解决上述技术问题,本发明提供一种基于fpga的平衡时钟偏斜的电路系统,包括:

3、硬核电路模块,包括时钟源单元、延时控制单元和第一交互单元;所述时钟源单元用于产生源时钟;所述延时控制单元用于根据源时钟生成延迟时钟,还用于根据源时钟和核内源时钟生成相位相同信号;所述第一交互单元用于在源时钟和相位相同信号的控制下,与第二交互单元进行数据的收发;

4、fpga模块,包括时钟专用走线单元和第二交互单元;所述时钟专用走线单元用于根据延迟时钟生成核内源时钟;所述第二交互单元用于在核内源时钟和相位相同信号的控制下,与所述第一交互单元进行数据的收发。

5、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述延时控制单元包括延时控制器和延迟时钟生成器;所述延时控制器用于根据源时钟和核内源时钟生成延时编码和相位相同信号;所述延迟时钟生成器用于根据延时编码对源时钟进行延时,以得到延迟时钟。

6、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述延时控制器包括数字鉴相器和编码器;所述数字鉴相器用于检测源时钟和核内源时钟的相位是否一致,并根据检测结果输出鉴相信号;所述编码器用于在源时钟的控制下,根据鉴相信号输出相位相同信号和/或延时编码信号。

7、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述数字鉴相器为寄存器;所述寄存器的ck端接入源时钟,d端接入核内源时钟,q端输出鉴相信号,以将源时钟作为采样时钟对核内源时钟进行采样,得知在源时钟上升沿时核内源时钟的相位。

8、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述延迟时钟生成器包括多路复用器和若干级联的缓冲器,所述缓冲器的个数与所述多路复用器的输入端的个数一致,且每一所述缓冲器的输出端与所述多路复用器的一个输入端一一对应连接;每一所述缓冲器的输出端与下一级缓冲器的输入端相连,第一级缓冲器的输入端接收源时钟;所述多路复用器用于根据延时编码接通对应的输入端,以输出延迟时钟。

9、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述第一交互单元包括第一发送器和第一接收器;所述第一发送器和所述第一接收器均包括第一寄存器、交互逻辑控制器和第二寄存器;所述第一寄存器和所述第二寄存器的时钟端均接入源时钟,所述交互逻辑控制器的使能端均接入相位相同信号;

10、所述第一发送器中的第一寄存器的输出端与所述第一发送器中的交互逻辑控制器的输入端相连,所述第一发送器中的交互逻辑控制器的输出端与所述第一发送器中的第二寄存器的输入端相连,所述第一发送器中的第二寄存器的输出端与所述第二交互单元相连,以实现数据的发送;

11、所述第一接收器中的第一寄存器的输入端与所述第二交互单元相连,输出端与所述第一接收器中的交互逻辑控制器的输入端相连,所述第一接收器中的交互逻辑控制器的输出端与所述第一接收器中的第二寄存器的输入端相连,以实现数据的接收。

12、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述第二交互单元包括第二发送器和第二接收器;所述第二发送器和所述第二接收器均包括第三寄存器和用户逻辑控制器;所述第三寄存器的时钟端和所述用户逻辑控制器的时钟端均接入核内源时钟,所述用户逻辑控制器的使能端接入相位相同信号;

13、所述第二发送器中的第三寄存器的输出端与所述第一接收器中的第一寄存器的输入端相连,所述第二发送器中的第三寄存器的输入端与所述第二发送器中的用户逻辑控制器的输出端相连,以实现数据的发送;

14、所述第二接收器中的第三寄存器的输入端与所述第一发送器中的第二寄存器的输出端相连,所述第二接收器中的第三寄存器的输出端与所述第二接收器中的用户逻辑控制器的输入端相连,以实现数据的接收。

15、可选的,在所述的基于fpga的平衡时钟偏斜的电路系统中,所述第一寄存器、所述第二寄存器和所述第三寄存器均为d触发器;d触发器的ck端为时钟端,d端为输入端,q端为输出端。

16、为解决上述技术问题,本发明还提供一种电路系统控制方法,应用于如上任一项所述的基于fpga的平衡时钟偏斜的电路系统,所述电路系统控制方法包括:

17、由时钟源单元提供源时钟,由时钟专用走线单元提供和内源时钟;

18、利用延时控制单元,根据源时钟和核内源时钟生成延迟时钟和相位相同信号;

19、将延迟时钟送入时钟专用走线单元,将源时钟作为第一交互单元的时钟信号,将核内源时钟作为第二交互单元的时钟信号,将相位相同信号作为第一交互单元和第二交互单元的使能信号;

20、根据时钟信号和使能信号,实现第一交互单元和第二交互单元之间的数据收发。

21、可选的,在所述的电路系统控制方法中,所述延时控制单元包括延时控制器和延迟时钟生成器,所述延时控制器包括数字鉴相器和编码器;所述根据源时钟和核内源时钟生成延迟时钟和相位相同信号的方法包括:

22、将源时钟和核内源时钟同时送入数字鉴相器;

23、在数字鉴相器中,使用源时钟对核内源时钟进行采样;

24、利用编码器,根据采样的结果,生成相位相同信号和延时编码信号;

25、将延时编码信号送入延迟时钟生成器,以得到延迟时钟。

26、可选的,在所述的电路系统控制方法中,所述根据采样的结果,生成相位相同信号和延时编码信号的方法包括:

27、无论采样的结果如何,数字鉴相器持续采样,编码器生成对应的延时编码信号,其中,每次采样后生成的延时编码信号不完全相同;

28、或,若源时钟和核内源时钟的相位一致,则编码器输出高电平的相位相同信号,且当数字鉴相器采样后输出的鉴相信号出现上边沿时,停止采样,编码器生成对应的延时编码信号。

29、本发明提供的基于fpga的平衡时钟偏斜的电路系统及控制方法,包括:硬核电路模块,包括时钟源单元、延时控制单元和第一交互单元;所述时钟源单元用于产生源时钟;所述延时控制单元用于根据源时钟生成延迟时钟,还用于根据源时钟和核内源时钟生成相位相同信号;所述第一交互单元用于在源时钟和相位相同信号的控制下,与第二交互单元进行数据的收发;fpga模块,包括时钟专用走线单元和第二交互单元;所述时钟专用走线单元用于根据延迟时钟生成核内源时钟;所述第二交互单元用于在核内源时钟和相位相同信号的控制下,与所述第一交互单元进行数据的收发。通过在硬核电路模块中设置的延时控制单元根据源时钟和核内源时钟生成延迟时钟和相位相同信号,并通过延迟时钟和相位相同信号实现fpga模块中第二交互单元和硬核电路模块中第一交互单元的数据交互,如此,利用延时控制单元来对时钟源端的寄存器和fpga上的寄存器之间的时钟偏斜进行平衡,使得fpga模块能够在不增加硬件资源的同时,有效减少了时钟偏斜,解决了如何在不增加fpga硬件资源的同时有效平衡时钟偏斜的问题。

- 还没有人留言评论。精彩留言会获得点赞!