基于UVM与FPGA验证平台的PCIe通道相位偏移验证方法及系统

本发明涉及计算机扩展总线验证,特别涉及一种基于uvm与fpga验证平台的pcie通道相位偏移验证方法及系统。

背景技术:

1、pcie总线技术,也称为计算机内部总线技术,即外围组件互联,一般应用在大型数据中心,可以接网卡、显卡等片外设备。pcie的基本结构包括根组件(root complex)、交换器(switch)和各种终端设备(endpoint)。pcie子系统有4中设备类型,分为root complex(rc)、pcie switch、pcie end point和pcie bridge。switch设备和rc设备可以向上或向下连接pcie总线,pcie总线的最底层为ep设备。在pci-express中,lane_to_lane_deskew是一个重要的概念,它指的是通道与通道之间存在的相位偏移。这种相位偏移可能来自多个方面,包括芯片驱动端和接收端之间的采样差异,以及串行化和反串行化逻辑引入的延迟。此外,印制电路板的阻抗变化和通道线路长度的不匹配也会导致通道间时序与数据存在一定差距。当pcie链路上有多个lane时,如果不同lane上同时传输的符号在不同时间点达到接收方,然后被串并转换,则会引发数据混乱,为保证正确接收和处理数据,需要对相位偏移进行测试验证,以消除通道之间的相位偏移,保证并行处理数据。

技术实现思路

1、本发明提供一种基于uvm与fpga验证平台的pcie通道相位偏移验证方法及系统,将通道差别的容许测试纳入pcie全系统的验证过程中,并与硬件配合测试,能够确保pcie接收端数据传输的可靠性。

2、按照本发明所提供的设计方案,一方面,提供一种基于uvm与fpga验证平台的pcie通道相位偏移验证方法,包含:

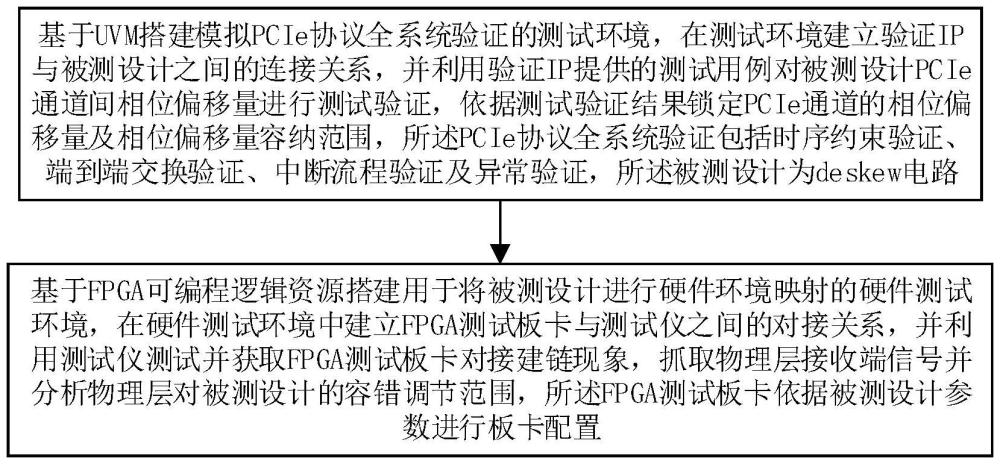

3、基于uvm搭建模拟pcie协议全系统验证的测试环境,在测试环境建立验证ip与被测设计之间的连接关系,并利用测试用例对被测设计pcie通道间相位偏移量进行测试验证,并依据测试验证结果锁定pcie通道的相位偏移量及相位偏移量容纳范围,所述pcie协议全系统验证包括时序约束验证、端到端交换验证、中断流程验证及异常验证,所述被测设计为deskew电路;

4、基于fpga可编程逻辑资源搭建用于将被测设计进行硬件环境映射的硬件测试环境,在硬件测试环境中建立fpga测试板卡与测试仪之间的对接关系,并利用测试仪测试并获取fpga测试板卡对接建链现象,抓取物理层接收端信号并分析物理层对被测设计的容错调节范围,所述fpga测试板卡依据被测设计参数进行板卡配置。

5、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,基于uvm搭建模拟pcie协议全系统验证的测试环境之前,还包含:

6、在被测设计串并口通过硬件描述语言分别建立时钟同步模型,以利用时钟同步模型模拟被测设计内外部不同时钟偏斜,所述时钟同步模型采用deskew算法生成。

7、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,基于uvm搭建模拟pcie协议全系统验证的测试环境,包含:

8、依据被测设计功能和角色设置测试环境中环境静态变量,所述环境静态变量包括被测模式、被测设计端口读写起始范围、及端口报文类型和端口报文长度;

9、设置用于检查被测设计接收数据完整性的计分板和用于模拟被测设计路由转发功能的rm队列。

10、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,建立验证ip与被测设计之间的连接关系,包含:

11、在验证ip中的各测试用例中利用指定函数改写测试环境中的环境静态变量,在验证ip和被测设计的连线依据信号进行延迟打拍配置,以依据延迟打拍配置的具体数值来改变被测设计对应通道相位偏移量。

12、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,建立验证ip与被测设计之间的连接关系,还包含:

13、依据级联调试环境配置被测设计上下游对接端口,在上下游对接端口对通道中每一组信号进行延迟打拍配置,其中,延迟打拍具体数值依据每一条pcie通道进行独立配置。

14、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,利用测试用例对被测设计pcie通道间相位偏移量进行测试验证,包含:

15、对被测设计每个端口连接的验证ip内存进行初始化,并在rm队列中模拟路由转发功能,以测试不同相位偏移量下pcie各端口的报文传输性能。

16、作为本发明基于uvm与fpga验证平台的pcie通道相位偏移验证方法,进一步地,利用验证ip提供的测试用例对被测设计pcie通道间相位偏移量进行测试验证,还包含:

17、利用验证ip提供的性能测试用例、容错测试用例及冗余测试用例分别对被测设计进行端到端交换验证、中断流程验证及异常验证。

18、再一方面,本发明还提供一种基于uvm与fpga验证平台的pcie通道相位偏移验证系统,包含:uvm测试模块和fpga测试模块,其中,

19、uvm测试模块,用于基于uvm搭建模拟pcie协议全系统验证的测试环境,在测试环境建立验证ip与被测设计之间的连接关系,并利用测试用例对被测设计pcie通道间相位偏移量进行测试验证,并依据测试验证结果锁定pcie通道的相位偏移量及相位偏移量容纳范围,所述pcie协议全系统验证包括时序约束验证、端到端交换验证、中断流程验证及异常验证,所述被测设计为deskew电路;

20、fpga测试模块,用于基于fpga可编程逻辑资源搭建用于将被测设计进行硬件环境映射的硬件测试环境,在硬件测试环境中建立fpga测试板卡与测试仪之间的对接关系,并利用测试仪测试并获取fpga测试板卡对接建链现象,抓取物理层接收端信号并分析物理层对被测设计的容错调节范围,所述fpga测试板卡依据被测设计参数进行板卡配置。

21、本发明的有益效果:

22、本发明针对高速数据传输中由于时钟抖动或传输线路不均匀,数据可能存在时钟偏移,导致严重的时序问题,基于uvm和fpga搭建测试环境和硬件平台,以实现更精准的deskew处理,能够更有效地纠正时钟偏移,确保数据在接收端能够准确、稳定地被解析,从而降低数据传输错误率。在集成电路设计中,时序问题是导致流片失败的常见原因之一,本案方案中,通过更真实地模拟实际工作环境中的时钟偏移情况,可以在设计阶段更早地发现和解决潜在的时序问题,从而提高整个流片过程的成功率,减少不必要的重新设计和制造成本。结合fpga测试和uvm验证实现更精准的deskew处理,使设计人员可以获得更多的参考信息,具体为,使用uvm上下游端口对接或者在全系统环境中与验证ip对接,能够更全面地了解deskew的临界现象和边界值,能够为设计人员提供更多的数据和洞察,使其能够更有针对性地调整时钟补偿策略,优化系统性能。本案方案可以实现更精准、更真实的deskew处理,能够为电子系统设计和通信领域带来显著的益处,包括提高数据传输可靠性、提高流片成功率、提供更多设计参考信息以及加深对整个系统的理解,有助于优化产品设计,提高产品质量,具有较好的应用前景。

- 还没有人留言评论。精彩留言会获得点赞!