DFT信号数据处理方法、DFT设计方法及验证方法与流程

本发明涉及芯片测试,尤其涉及一种dft信号数据处理方法、dft设计方法及dft验证方法。

背景技术:

1、当前随着芯片上集成的器件越来越多,soc芯片的设计复杂性急剧增加,导致芯片缺陷出现的可能性随之变大。对于量产芯片,需要通过芯片测试筛选出存在缺陷的芯片,而传统芯片测试需要较高测试成本与测试时间。目前,在芯片设计过程就已经开始考虑芯片测试,也就是加入dft(design for test)可测性设计流程。

2、dft流程在以cpu、gpu等为代表的单片超大规模集成电路中得以广泛应用。使用dft流程的目的在于找出芯片的固定故障、测试芯片的实际性能,从而便于进行量产筛片。目前dft流程的测试结构主要包括:扫描链测试、边界扫描测试、内存内建自测试、模拟测试等。

3、dft设计的目的是将某些特殊结构在芯片设计阶段植入电路,以便芯片流片后进行测试,以检测制造工艺过程中出现的设计缺陷。dft验证的目的是检查设计中的错误,确保设计符合其设计规范和所期望的功能。

4、然而,目前dft设计/验证流程存在明显的缺点,例如:

5、1、dft设计/验证文档的来源较多,这些来源包括架构工程师、ip设计工程师、后端工程师、模拟工程师的文档,这导致在项目过程中,因某些芯片的文档改动使得dft设计/验证改动的地方较多,容易发生遗漏,导致芯片流片后无法量产;

6、2、dft设计代码不容易考虑完备,进而漏掉某些测试模式、信号,导致芯片可测试性覆盖率降低,甚至在测试阶段无法测试芯片某些功能;

7、3、dft验证需要查看每个测试案例的仿真波形、检查测试模式以及芯片信号是否与期望一致,工作效率较低;另外,soc级验证平台的编译时间很长,仿真目标文件较大,单个测试案例的仿真时间就较长,导致dft验证调试时间被大大压缩;

8、4、不同项目dft设计都需要根据项目需求,重新设计修改系统级rtl代码,导致dft设计代码兼容性复用性较差,验证代码复用性较差,延长芯片开发时间。

技术实现思路

1、本发明的目的之一是提供一种soc级一种dft信号数据处理方法、dft设计方法及dft验证方法,以解决soc级dft设计功能点不完备、改动易遗漏、代码复用性差导致芯片开发时间长的问题,以及soc级dft验证效率低下、芯片测试覆盖率较低、芯片流片成功率低的技术问题。

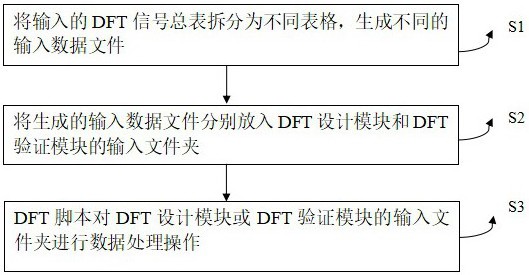

2、为了解决上述技术问题,第一方面,本发明实施例提供了一种dft信号数据处理方法,所述方法包括:

3、将输入的dft信号总表拆分为不同表格,生成不同的输入数据文件;

4、将生成的输入数据文件分别放入dft设计模块和dft验证模块的输入文件夹;

5、dft脚本对dft设计模块或dft验证模块的输入文件夹进行数据处理操作。

6、优选的,所述将输入的dft信号总表拆分为不同表格,生成不同的输入数据文件具体包括:

7、将输入的dft信号总表通过脚本转为中间文本文件;

8、根据信号名,对信号进行分类排序,所述信号包括:模拟输入信号、模拟输出信号、io输入信号、io输出信号、memory输入信号、memory输出信号、跨电压域输入信号、跨电压域输出信号;

9、根据测试优先级和信号排序,生成每种测试模式下的第一对应文件;

10、确定每种测试模式下,dft设计需要使用的信号名与设计期望值,并生成第二对应文件;

11、确定每种测试模式下,非dft设计复用信号的信号名、设计期望值、验证期望值,及dft设计复用信号的验证激励值,生成第三对应文件。

12、优选的,dft脚本对dft设计模块的输入文件夹进行数据处理操作具体包括:

13、对比每种测试模式下非dft设计复用信号的设计期望值与验证期望值,如果不一致则修改验证期望值;

14、根据第一对应文件,生成每种测试模式下的输入输出信号文件;

15、根据第一对应文件、第二对应文件,生成每种测试模式下需要用到的内部信号文件;

16、根据第一对应文件,第三对应文件,将dft设计期望值与信号名进行一一对应,若某根信号的dft设计期望值为mask,则在这种测试模式下dft设计不使用该信号,信号期望值为默认上电复位值。

17、优选的,dft脚本对dft验证模块的输入文件夹进行数据处理操作具体包括:

18、根据第一对应文件和第三对应文件,将dft验证期望值与非dft设计复用信号进行一一对应,若某根信号的dft验证期望值为mask,则在这种测试模式下不检查该信号;

19、根据第二对应文件,将每种测试模式下需要的复用信号,按照输入输出信号进行分类;

20、将每种测试模式下的dft设计复用信号的验证激励值与输入信号名进行一一对应;

21、将每种测试模式下的dft设计复用信号的验证期望值与输出信号名进行一一对应。

22、第二方面本发明实施例还提供了一种基于dft信号数据处理方法的dft设计方法,所述方法包括:

23、将生成的dft信号总表输入dft脚本,确定dft代码的信号使用信息,dft脚本自动生成各个测试模式下dft输出信号代码、dft输入信号代码;

24、根据测试模式的优先级,dft脚本将生成的dft设计代码进行合并和压缩,生成不同测试模式下的信号隔离代码;

25、根据dft代码的使用信号信息,自动生成module端口、输入、输出与内部信号;

26、在扫描链模式下,dft脚本根据dft信号总表将module端口的输出信号,增加绕回逻辑,产生新的内部信号代替原来的输入信号,作为扫描链模式下的输入信号。

27、第三方面,本发明实施例还提供了一种基于dft信号数据处理方法的dft验证方法,所述方法包括:

28、进入不同测试模式,根据测试功能点的不同,dft脚本生成对应的激励代码向dft复用输入io中灌入对应激励值,验证芯片输出信号是否与期望值一致;

29、dft脚本自动将验证代码打包生成不同测试模式的dft验证测试案例;

30、采用灰盒验证方法,dft脚本根据io、memory、数模端口、跨电压域非复用信号与验证期望值文件生成相应的断言检测代码,检测进入测试模式后到退出测试模式前该信号值是否发生变化、是否与预期值一致;

31、dft脚本自动将生成的代码打包生成dft monitor。

32、第四方面,本发明实施例提供了一种电子设备,包括处理器和存储器,所述存储器用于存储计算机程序,所述计算机程序包括程序指令,所述处理器被配置用于调用所述程序指令,执行如前所述的dft信号数据处理方法。

33、第五方面,本发明实施例提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序包括程序指令,所述程序指令当被处理器执行时使所述处理器执行如前所述的dft信号数据处理方法。

34、第六方面,本发明实施例提供了一种电子设备,包括处理器和存储器,所述存储器用于存储计算机程序,所述计算机程序包括程序指令,所述处理器被配置用于调用所述程序指令,执行如前所述的dft设计方法或dft验证方法。

35、与现有技术相比,本发明实施例提供的一种dft信号数据处理方法、dft设计方法及dft验证方法至少具有以下有益效果:

36、本发明实施例的dft信号总表通过云端直接链接架构工程师、ip设计工程师、后端工程师、模拟工程师的文档,他们对文档的修改会全部同步到dft信号总表,解决了在项目中某些芯片文档改动后,dft设计、验证改动内容容易被遗漏的问题。

37、dft脚本通过dft信号总表,进行数据处理,自动生成dft设计代码、dft monitor、dft验证测试案例,解决了设计容易考虑不够完备,验证调试时间长,工作效率较低的问题,新增加的dft monitor在仿真芯片测试时检测dft复用io、dft不复用io、数模接口信号、memory接口信号、跨电压域信号是否与预期一致,增加了dft设计、验证覆盖率,提高芯片可测性以及测试可靠性。

38、另外,本发明实施例通过使用dft信号总表整合dft设计验证所需数据,dft脚本处理数据、生成代码,解决了dft设计代码兼容性复用性较差,验证代码复用性较差,延长芯片开发时间的问题,并且具有良好兼容性复用性扩展性。

- 还没有人留言评论。精彩留言会获得点赞!