片上系统及其调频方法、电子设备和存储介质与流程

本公开涉及芯片,特别涉及一种片上系统及其调频方法、电子设备和存储介质。

背景技术:

1、片上系统(soc,system on a chip)的多处理器架构是在一个芯片上集成多个处理器核心以实现更高性能、更低功耗和更紧凑的系统设计。这种架构通常用于需要处理大量并行任务或需要更高计算能力的应用。在片上系统的多处理器架构中,每个处理器核心可以独立运行程序,执行任务,并通过共享内存或其他通信机制进行通信和协作。

2、多处理器架构的片上系统中,系统运行后某个或某些处理器会固定在某个时钟频率下工作,即使无数据传输也将维持该时钟频率,造成资源浪费。然而,该处理器通过例如监测空载率等常规方式对自身调频,将造成片上系统时钟混乱,产生总线信号采样错误,影响片上系统的整体运行稳定性。

技术实现思路

1、有鉴于此,本公开提供了一种片上系统及其调频方法、电子设备和存储介质,能够在不影响片上系统时钟的前提下实现特定处理器的调频,达到降低片上系统整体功耗,提升片上系统整体性能的目的。

2、根据本公开的第一方面,提供了一种片上系统的调频方法,所述方法应用于片上系统,所述片上系统包括第一处理器、第二处理器和第三处理器,所述第一处理器分别与所述第二处理器、第三处理器通信;

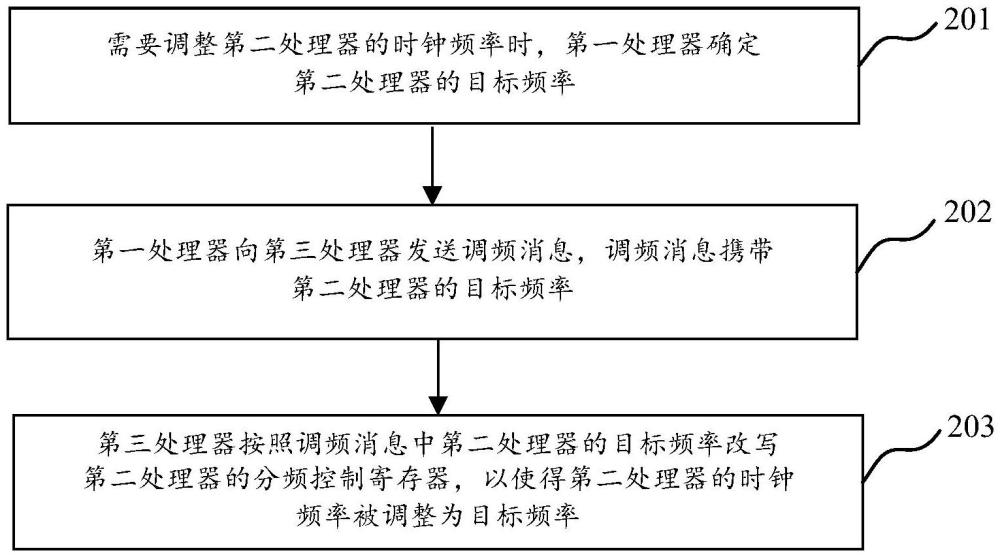

3、所述片上系统的调频方法包括:需要调整第二处理器的时钟频率时,第一处理器确定第二处理器的目标频率;第一处理器向第三处理器发送调频消息,所述调频消息携带所述第二处理器的目标频率;第三处理器按照所述调频消息中第二处理器的目标频率改写第二处理器的分频控制寄存器,以使得所述第二处理器的时钟频率被调整为所述目标频率。

4、本公开第一方面的一些实施方式中,所述片上系统还包括:繁忙寄存器,所述繁忙寄存器能够被第一处理器和第二处理器访问,用于记录繁忙值,所述繁忙值用于指示第二处理器的运行状态;所述方法还包括:所述第一处理器监控所述繁忙寄存器,在所述繁忙寄存器中的繁忙值变化时确定需要调整第二处理器的时钟频率。

5、本公开第一方面的一些实施方式中,所述繁忙值由所述第二处理器根据如下之一或多项确定并写入所述繁忙寄存器:

6、第二处理器的系统空闲比例;

7、第一中断统计值,所述第一中断统计值表示所述第二处理器在第一预定时长内处理的外设中断请求的数量。

8、本公开第一方面的一些实施方式中,所述第一中断统计值通过如下方式确定:第二处理器定时收集各外设寄存器中的全局变量,一个外设寄存器中的全局变量表示一个外设控制器在单位时间内的中断次数;第二处理器对各外设寄存器中的全局变量进行统计运算以得到所述第一中断统计值,所述第一中断统计值为所述第二处理器在单位时间内处理的外设中断数量。

9、本公开第一方面的一些实施方式中,还包括:所述第一处理器根据第二中断统计值确定是否需要调整第二处理器的时钟频率,所述第二中断统计值表示所述第一处理器在第二预定时长内发起的针对各外设控制器的中断请求的数量。

10、本公开第一方面的一些实施方式中,所述片上系统中还包括:外设寄存器,所述外设寄存器能够被第一处理器与第二处理器访问;所述第二中断统计值根据各所述外设寄存器中记录的中断请求计数值确定。

11、本公开第一方面的一些实施方式中,所述第二中断统计值通过如下方式得到:第一处理器定时收集各外设寄存器中的中断请求计数值,一个外设寄存器中的中断请求计数值表示第一处理器在单位时间发起的针对一个外设控制器的中断请求的数量;第一处理器对各外设寄存器中的中断请求计数值进行统计运算以获得第二中断统计值,所述第二中断统计值为第一处理器在单位时间内发起的外设中断请求数量。

12、本公开第一方面的一些实施方式中,所述第一处理器确定第二处理器的目标频率,包括:第一处理器中的调频驱动引擎被初始化后,所述调频驱动引擎调用预配置的第三acpi方法,所述第三acpi方法被调用时从第一处理器中的acpi表读取所述第二处理器的调频参数;第一处理器根据所述第二处理器的调频参数和当前频率,确定所述第二处理器的目标频率;

13、其中,所述调频参数包括如下之一或多项:

14、指示当前支持的调频模式的第一参数;

15、指示当前支持的调频档位数量的第二参数;

16、指示各调频档位所对应目标频率的调频档位值。

17、本公开第一方面的一些实施方式中,所述第二处理器的当前频率由所述调频驱动引擎调用预配置的第二acpi方法从所述acpi表中读取。

18、本公开第一方面的一些实施方式中,所述第一处理器根据所述第二处理器的调频参数和当前频率,确定所述第二处理器的目标频率,包括如下之一:

19、在所述第一参数指示当前支持第一调频模式时,获取用户设定的频率值并确定所述第二处理器的目标频率为所述用户设定的频率值;

20、在所述第一参数指示当前支持第二调频模式时,所述第二参数的取值为2,第一处理器将所述调频参数中不同于所述第二处理器当前频率的一调频档位值确定为所述第二处理器的目标频率;

21、在所述第一参数指示当前支持第二调频模式时,所述第二参数大于2,第一处理器在不同于所述第二处理器当前频率的多个所述调频档位值中选择一个作为所述第二处理器的目标频率。

22、本公开第一方面的一些实施方式中,所述第一处理器根据所述第二处理器的调频参数和当前频率,确定所述第二处理器的目标频率,包括:

23、所述第一处理器根据第二中断统计值和预先配置的对应各个调频档位的档位阈值,在不同于所述第二处理器当前频率的多个所述调频档位值中选择一个作为所述第二处理器的目标频率,所述第二中断统计值表示所述第一处理器在第二预定时长内发起的针对各外设控制器的中断请求的数量。

24、本公开第一方面的一些实施方式中,所述第一处理器根据所述第二处理器的调频参数和当前频率,确定所述第二处理器的目标频率,包括:

25、所述第一处理器中的调频驱动引擎检测到所述第二中断统计值大于第二档位阈值且小于第一档位阈值时,确定所述第二处理器的调频档位为所述第二档位阈值对应的第二调频档位,所述第一档位阈值对应的第一调频档位的档位值高于所述第二调频档位的档位值;

26、所述第一处理器中的调频驱动引擎调用所述第二acpi方法从所述调频参数中读取所述第二调频档位的档位值以作为所述第二处理器的目标频率。

27、本公开第一方面的一些实施方式中,所述第一处理器向第三处理器发送调频消息,包括:

28、第一处理器中的调频驱动引擎调用预配置的第一acpi方法,所述第一acpi方法被调用时解析acpi表中第二处理器的method请求以生成scmi消息并送至所述第三处理器,所述scmi消息携带所述第二处理器的目标频率。

29、本公开第一方面的一些实施方式中,所述第二处理器的输入时钟源包括主时钟源,所述主时钟源用于为所述第二处理器提供主时钟信号,所述主时钟信号为所述第二处理器的核的主时钟;所述第三处理器按照所述调频消息中第二处理器的目标频率改写所述第二处理器的分频控制寄存器,包括:所述第三处理器将用于控制所述第二处理器主时钟源的第一分频控制寄存器的值改写为所述第二处理器的目标频率,以使得所述第二处理器的主时钟信号的频率更改为所述目标频率。

30、本公开第一方面的一些实施方式中,所述第二处理器的输入时钟源还包括:参考时钟源,所述参考时钟源用于为所述第二处理器提供参考时钟信号,所述参考时钟信号为所述第二处理器的核的备用时钟;所述方法还包括:改写所述第一分频控制寄存器前,所述第三处理器控制所述第二处理器的主时钟源停顿,使能所述第二处理器的参考时钟源,以使得所述第二处理器的输入时钟从所述主时钟信号切换为所述参考时钟信号;以及,改写所述第一分频控制寄存器后,所述第三处理器释放所述第二处理器的主时钟源停顿,控制所述第二处理器的参考时钟源停顿,以使得所述第二处理器的输入时钟从所述参考时钟信号切回所述主时钟信号。

31、根据本公开的第二方面,提供了一种片上系统,包括:第一处理器、第二处理器和第三处理器,所述第一处理器能够分别与所述第二处理器、第三处理器通信;其中,

32、所述第一处理器,用于需要调整第二处理器的时钟频率时确定第二处理器的目标频率,向第三处理器发送调频消息,所述调频消息携带所述第二处理器的目标频率;

33、所述第三处理器,用于按照所述调频消息中第二处理器的目标频率改写所述第二处理器的分频控制寄存器,以使得所述第二处理器的时钟频率被调整为所述目标频率。

34、根据本公开的第三方面,提供了一种电子设备,包括:存储程序的存储器,所述程序包括指令,所述指令在由所述处理器执行时使所述处理器执行上述的方法。

35、根据本公开的第四方面,提供了一种存储有程序的计算机可读存储介质,所述程序包括指令,所述指令在由处理器执行时使所述处理器执行上述的方法。

36、由上述技术方案可以看出,本公开实施例可以由第一处理器确定第二处理器的目标频率,第一处理器向第三处理器发送针对第二处理器的调频消息,由第三处理器按照调频消息中的目标频率改写第二处理器的分频控制寄存器,从而使得第二处理器的时钟频率被调整为目标频率。由此,本公开实施例可以实现多处理器架构下特定处理器的动态调频,从而达到降低片上系统整体功耗、提升片上系统整体性能的目的。

- 还没有人留言评论。精彩留言会获得点赞!