基于施密特触发器迟滞效应的自筛选单稳态PUF电路

本发明涉及puf电路,尤其是涉及一种基于施密特触发器迟滞效应的自筛选单稳态puf电路。

背景技术:

1、数字化时代,安全性成为信息技术领域的核心关注点,物理不可克隆函数(physical unclonable function,puf)作为一种可靠的硬件安全原语迅速发展。puf电路基于集成电路(integrated circuit,ic)在制造过程中固有的、不可预测的物理差异,为每个ic赋予了独一无二的“指纹”。这些物理差异可以是器件参数的微小变化,例如晶体管的阈值电压、电阻值或电容值等。基于这些微小的物理差异,puf电路生成一系列特定的响应,用以区分不同的ics,从而为硬件设备提供唯一标识符。puf电路的出现,标志着从传统的密钥存储和管理方法向更为动态、安全的密钥生成和认证机制的转变。相比于传统的密钥存储方案,puf电路不需要在设备中存储密钥,而是根据硬件本身的特征动态生成密钥,极大地增强了集成电路的安全性。

2、puf电路根据其内部puf单元阵列中puf单元输出状态的数量,可以分为单稳态puf电路和双稳态puf电路。其中,单稳态puf电路中的puf单元只有一个稳定的输出状态,通常应用于低功耗设备和资源受限的环境。然而,现有的单稳态puf电路中的puf单元通常采用放大器输入和输出短接的方式产生熵源,通过多级放大器串联的方式对熵源进行放大提取得到puf响应。不可避免地,一部分熵源的输出电压位于放大器开关电压附近。在电压和温度波动时,熵源的输出电压会产生偏移,使提取得到的puf响应发生改变,导致了单稳态puf电路的稳定性问题。

技术实现思路

1、本发明所要解决的技术问题是提供一种具有高稳定性的基于施密特触发器迟滞效应的自筛选单稳态puf电路。

2、本发明解决上述技术问题所采用的技术方案为:一种基于施密特触发器迟滞效应的自筛选单稳态puf电路,包括由n×m个puf单元按照n行m列分布形成的puf单元阵列,其中n和m分别为大于等于1的整数,通过增加基于施密特触发器的筛选单元,利用施密特触发器的迟滞效应,对输出不稳定的puf单元进行高效自筛选,实现整体puf电路的稳定性提升。

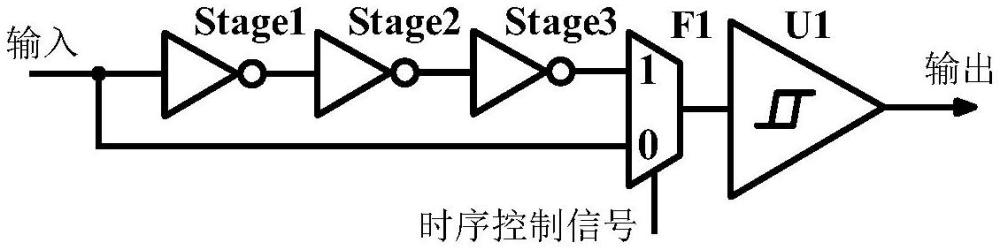

3、所述的筛选单元包括第一反相器、第二反相器、第三反相器、2选1数据选择器和施密特触发器,所述的第一反相器、所述的第二反相器和所述的第三反相器均具有输入端和输出端,所述的2选1数据选择器具有两个输入端、输出端以及时序控制端,将其两个输入端分别称为其第一输入端和第二输入端,所述的施密特触发器具有输入端和输出端,所述的第一反相器的输入端与所述的2选1数据选择器的第二输入端连接,且其连接端作为所述的筛选单元的输入端,所述的筛选单元的输入端用于接入puf单元产生的输出响应,所述的第一反相器的输出端与所述的第二反相器的输入端相连,所述的第二反相器的输出端与所述的第三反相器的输入端相连,所述的第三反相器的输出端与所述的2选1数据选择器的第一输入端相连,所述的2选1数据选择器的输出端与所述的施密特触发器的输入端相连,所述的施密特触发器的输出端作为所述的筛选单元的输出端,所述的筛选单元的输出端用于输出筛选结果,所述的2选1数据选择器的时序控制端为所述的筛选单元的时序控制端,用于接入高电平或者低电平的时序控制信号。

4、所述的基于施密特触发器迟滞效应的自筛选单稳态puf电路还包括输入寄存器、时序控制器、行译码器、列译码器和传输门阵列,所述的输入寄存器用于预存所需的行地址数据和列地址数据;所述的时序控制器具有输出端,所述的时序控制器用于产生高电平的时序控制信号或者低电平的时序控制信号通过其输出端输出,所述的时序控制器的输出端与所述的筛选单元的时序控制端连接;所述的行译码器具有输入端和n位输出端,所述的行译码器的输入端和所述的输入寄存器连接,接入所述的行地址数据,所述的行译码器用于将其输入端接入的行地址数据转换为n位行选择信号通过其n位输出端一一对应输出,其中n位行选择信号中只有一位是高电平,其他位都是低电平;所述的列译码器具有输入端和m位输出端,所述的列译码器的输入端与所述的输入寄存器连接,所述的列译码器的输入端接入所述的列地址数据,所述的列译码器用于将其输入端接入的列地址数据转换为m位列选择信号通过其m位输出端一一对应输出,其中,m位列选择信号中只有一位是高电平,其他位都是低电平;所述的传输门阵列由(n+1)×m个传输门按照n+1行m列分布形成,每个所述的传输门均具有输入端、输出端以及控制端,在其控制端接入的控制信号控制下,其输入端和输出端能够导通或者断开;每个puf单元均具有用于输出其输出响应的输出端;所述的行译码器的第k位输出端与位于第k行的m个传输门的控制端连接,k=1,2,…,n,所述的列译码器的第j位输出端与位于第n+1行第j列的传输门的控制端连接,j=1,2,…,m,位于第k行第j列的puf单元的输出端与位于第k行第j列的传输门的输入端相连,位于第j列的第1行至第n行的n个传输门的输出端均与位于第j列第n+1行的传输门的输入端连接,位于第n+1行的m个传输门的输出端均与所述的筛选单元的输入端连接。

5、每个所述的puf单元均包括第一mos管、第二mos管、第三mos管以及第四mos管,所述的第一mos管和所述的第三mos管均为pmos管,所述的第二mos管和所述的第四mos管均为nmos管,所述的第一mos管的源极和所述的第三mos管的源极均接入电源电压vdd,所述的第一mos管的漏极和栅极、所述的第二mos管的漏极和栅极、所述的第三mos管的栅极和所述的第四mos管的栅极连接,所述的第三mos管的漏极和所述的第四mos管的漏极连接,且其连接端为所述的puf单元的输出端,所述的第二mos管的源极和所述的第四mos管的源极均接地;所述的第一mos管和所述的第二mos管构成第一级反相器,所述的第三mos管和所述的第四mos管构成第二级反相器。

6、每个所述的传输门均包括第五mos管、第六mos管、第七mos管和第八mos管,所述的第五mos管和所述的第七mos管均为pmos管,所述的第六mos管和所述的第八mos管均为nmos管,所述的第五mos管的源极和所述的第六mos管的源极连接,且其连接端为所述的传输门的输入端,所述的第五mos管的漏极和所述的第六mos管的漏极连接,且其连接端为所述的传输门的输出端,所述的第五mos管的栅极、所述的第七mos管的漏极和所述的第八mos管的漏极连接,所述的第六mos管的栅极、所述的第七mos管的栅极和所述的第八mos管的栅极连接,且其连接端为所述的传输门的控制端,所述的第八mos管的源极接地,所述的第七mos管的源极接入电源电压vdd。

7、所述的施密特触发器包括第九mos管、第十mos管、第十一mos管、第十二mos管、第十三mos管和第十四mos管,所述的第九mos管、所述的第十mos管和所述的第十三mos管均为pmos管,所述的第十一mos管、所述的第十二mos管和所述的第十四mos管均为nmos管,所述的第九mos管的源极接入电源电压vdd,所述的第九mos管的栅极、所述的第十mos管的栅极、所述的第十一mos管的栅极和所述的第十二mos管的栅极连接,且其连接端为所述的施密特触发器的输入端,所述的第九mos管的漏极、所述的第十mos管的源极和所述的第十三mos管的源极连接,所述的第十三mos管的漏极接地,所述的第十mos管的漏极、所述的第十一mos管的漏极、所述的第十三mos管的栅极和所述的第十四mos管的栅极连接,且其连接端为所述的施密特触发器的输出端,所述的第十一mos管的源极、所述的第十二mos管的漏极和所述的第十四mos管的源极连接,所述的第十二mos管的源极接地,所述的第十四mos管的漏极接入电源电压vdd。

8、与现有技术相比,本发明的优点在于通过增加基于施密特触发器的筛选单元,利用施密特触发器的迟滞效应,对输出不稳定的puf单元进行高效自筛选,通过筛选单元能够将不稳定的puf单元筛选出来,从而将不稳定的puf单元产生的输出响应的提取值舍弃,仅保存稳定的puf单元产生的输出响应的提取值,具有高稳定性。

- 还没有人留言评论。精彩留言会获得点赞!