硬件加速装置、方法、系统及存储介质

本发明涉及数据处理,尤其涉及一种硬件加速装置、方法、系统及存储介质,具体是一种面向超低延时的任意次递归调用的fft和ifft硬件加速装置、方法、系统及存储介质。

背景技术:

1、快速傅里叶变换(fastfouriertransform),即利用计算机计算离散傳里叶变换q(dft)的高效、快速计算方法的统称,简称fft。快速傅里叶变换是1965年由j.w.库利和t.w,图基提出的。采用这种算法能使计算机计算离散傅里叶变换所需要的乘法次数大为减少,特别是被变换的抽样点数n越多,fft算法计算量的节省就越显著。

2、fft在多个领域有着广泛的应用,包括但不限于信号处理、通信、计算机科学、音频处理、图像处理、机器学习、数据加密和安全等。尽管fft硬件加速在许多应用中具有显著的优势,但仍存在一些弊端,包括:

3、1.成本高昂:fft硬件加速通常需要专门设计和制造的硬件电路,导致成本较高。这对于个人用户或小规模应用来说可能不太实际。

4、2.限制了灵活性:一旦fft硬件加速器被设计和制造,其功能和性能通常是固定的,难以进行灵活的修改或升级。这对于需要频繁变动需求的应用来说可能不太适用。

5、3.物理空间占用:fft硬件加速器通常需要占用较大的物理空间。对于空间受限的设备或系统,如嵌入式系统或移动设备,可能很难集成这样的硬件加速器。

6、4.依赖特定硬件平台:fft硬件加速器通常是针对特定的硬件平台设计的,不同平台之间的兼容性可能存在问题。这使得在不同平台上进行移植或跨平台开发变得更加困难。

7、因此,fft硬件加速器在某些特定场景下具有明显的优势,但也存在一些限制和弊端。在决定是否采用fft硬件加速时,需要考虑应用的需求、成本、灵活性和平台兼容性等因素。

技术实现思路

1、针对现有技术存在的不足,本发明的目的在于提供一种硬件加速装置、方法、系统及存储介质,能够根据计算资源的功耗限制和性能需求,改变参数配置,灵活地调整计算复杂度和资源利用率、实现精度、功耗和算力之间的平衡,并将运算延时推向极致。

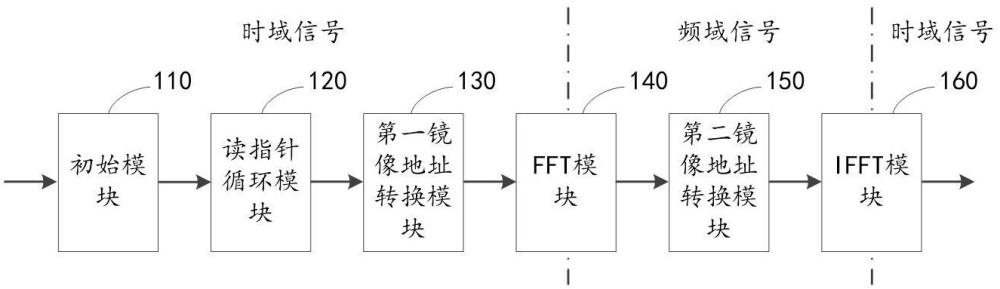

2、本公开的第一方面提供了一种硬件加速装置,所述硬件加速装置包括以下模块中一个或多个:

3、初始模块,被配置为缓存原始的时域信号;

4、读指针循环模块,被配置为基于所述原始的时域信号产生周期连续更替的初始信号;

5、第一镜像地址转换模块,被配置为将所述周期连续更替的初始信号转换为适配fft模块的指针时序,以为所述fft模块持续地提供待处理的时域信号的数据;

6、fft模块,包括fft递归体模块,所述fft模块被配置为按最优时序接收所述待处理的时域信号的数据,并通过所述fft递归体模块将所述待处理的时域信号的数据转换为周期连续更替的频域信号,所述fft递归体模块被配置为执行可任意次循环的蝶形套娃运算;

7、第二镜像地址转换模块,被配置为接收所述周期连续更替的频域信号,以及将所述周期连续更替的频域信号转换为适配ifft模块的指针时序,以为所述ifft模块持续地提供待处理的频域信号的数据;以及

8、ifft模块,包括ifft递归体模块,所述ifft模块被配置为按最优时序接收所述待处理的频域信号的数据,并通过所述ifft递归体模块将所述待处理的频域信号的数据还原为原始的时域信号,所述ifft递归体模块被配置为执行可任意次循环的蝶形套娃运算。

9、可选的,所述fft模块通过对所述fft递归体模块进行任意次递归调用,实现4到正无穷点数的fft运算,以将所述待处理的时域信号的数据转换为周期连续更替的频域信号;

10、所述ifft模块通过对所述ifft递归体模块进行任意次递归调用,实现4到正无穷点数的fft运算,以将所述待处理的频域信号的数据还原为原始的时域信号。

11、可选的,所述fft递归体模块和所述ifft递归体模块各自包括基本递归单元模块和n层递归体模块,n为所述fft递归体模块或者所述ifft递归体模块执行递归调用的最大嵌套层数,

12、所述fft递归体模块和所述ifft递归体模块各自包括一个最顶层递归体模块和一个最底层递归体模块,所述最顶层递归体模块为执行第n层递归调用的递归体模块,所述最底层递归体模块为所述基本递归单元模块。

13、可选的,所述最大递归调用嵌套层数n的值按照以下公式确定:

14、

15、其中,m为fft或者ifft的运算点数。

16、可选的,每层递归体模块都包括一顺序相同但执行时间为其前一层递归体模块的执行时间2倍的蝶形管道选通时序模块。

17、可选的,所述蝶形管道选通时序模块包括至少一个隐形状态机模块,所述隐形状态机模块的触发条件和输出指针均被计数器模块中 的倍数特质隐藏。

18、可选的,每层递归体模块中的所述隐形状态机模块均包括当前层蝶形运算0、1、2、3的四种状态,且四种状态下的蝶形管道指针的导向一致,其中,0表示对蝶形的左前翼进行乘累加,1表示对蝶形的左后翼进行乘累加,2表示对蝶形的右前翼进行乘累加,3表示对蝶形的右后翼进行乘累加。

19、可选的,每层递归体模块均有四个方向的蝶形指针,其中任意一个方向的蝶形指针中都包含了前一层递归体模块中同样方向的两枚小指针;所述递归体模块每执行一次指针操作,其所包含的前一层递归体模块中的同样方向的两枚小指针以2倍的速率陆续执行两次指针操作。

20、可选的,当前层的递归体模块的状态周期是其前一层递归体模块的状态周期的2倍,当前层的递归体模块的数据位宽为前一层递归体模块的数据位宽的2倍。

21、可选的,每层递归体模块的所述数据位宽为w的数据管道中,包含两条数据位宽均为w/2的数据位宽的数据管道。

22、本公开的第二方面提供了一种硬件加速方法,所述方法包括一个或多个以下步骤:

23、缓存原始的时域信号;

24、基于所述原始的时域信号产生周期连续更替的初始信号;

25、将所述周期连续更替的初始信号转换为适配fft变换的指针时序,以获得待处理的时域信号的数据;

26、按最优时序接收所述待处理的时域信号的数据,并通过fft递归体模块将所述待处理的时域信号的数据转换为周期连续更替的频域信号,所述fft递归体模块被配置为执行可任意次循环的蝶形套娃运算;

27、将所述周期连续更替的频域信号转换为适配ifft变换的指针时序,以获得待处理的频域信号的数据;

28、按最优时序接收所述待处理的频域信号的数据,并通过ifft递归体模块将所述待处理的频域信号的数据还原为原始的时域信号,所述ifft递归体模块被配置为执行可任意次循环的蝶形套娃运算。

29、可选的,通过对所述fft递归体模块进行任意次递归调用,实现4到正无穷点数的fft运算,以将所述待处理的时域信号的数据转换为周期连续更替的频域信号;

30、通过对所述ifft递归体模块进行任意次递归调用,实现4到正无穷点数的fft运算,以将所述待处理的频域信号的数据还原为原始的时域信号。

31、可选的,所述fft递归体模块和所述ifft递归体模块各自包括基本递归单元模块和n层递归体模块,n为所述fft递归体模块或者所述ifft递归体模块执行递归调用的最大嵌套层数,

32、所述fft递归体模块和所述ifft递归体模块各自包括一个最顶层递归体模块和一个最底层递归体模块,所述最顶层递归体模块为执行第n层递归调用的递归体模块,所述最底层递归体模块为所述基本递归单元模块。

33、可选的,所述最大递归调用嵌套层数n的值按照以下公式确定:

34、

35、其中,m为fft或ifft的运算点数。

36、可选的,每层递归体模块都包括一顺序相同但执行时间为其前一层递归体模块的执行时间2倍的蝶形管道选通时序。

37、可选的,所述蝶形管道选通时序包括至少一个隐形状态机,所述隐形状态机的触发条件和输出指针均被计数器中 的倍数特质隐藏。

38、可选的,每层递归体模块中的所述隐形状态机模块均包括当前层蝶形运算0、1、2、3的四种状态,且四种状态下的蝶形管道指针的导向一致,其中,0表示对蝶形的左前翼进行乘累加,1表示对蝶形的左后翼进行乘累加,3表示对蝶形的右前翼进行乘累加,4表示对蝶形的右后翼进行乘累加。

39、可选的,每层递归体模块均有四个方向的蝶形指针,其中任意一个方向的蝶形指针中都包含了前一层递归体模块中同样方向的两枚小指针;所述递归体模块每执行一次指针操作,其所包含的前一层递归体模块中的同样方向的两枚小指针以2倍的速率陆续执行两次指针操作。

40、可选的,当前层的递归体模块的状态周期是其前一层递归体模块的状态周期的2倍,当前层的递归体模块的数据位宽为前一层递归体模块的数据位宽的2倍。

41、可选的,每层递归体模块的所述数据位宽为w的数据管道中,包含两条数据位宽均为w/2的数据位宽的数据管道。

42、本公开的第三方面提供了一种硬件加速系统,所述硬件加速系统包括上述第一方面的硬件加速装置。

43、本公开的第四方面提供了一种非暂时性计算机可读存储介质,所述非暂时性计算机可读存储介质中存储有计算机指令,所述计算机指令适于处理器加载,以实现上述第一方面的硬件加速方法。

44、实施上述方案,具有如下有益效果:

45、本公开中,fft模块的架构和ifft模块的架构极为相似,这两套架构可由同一套代码来描述。通过修改define宏定义值来确定被例化时是扮演fft的角色,还是扮演ifft的角色,从而降低了代码维护和管理的难度。

46、fft递归体模块被配置为执行可任意次循环的蝶形套娃运算,通过调用fft递归体模块可实现任意点数的fft运算。ifft递归体模块被配置为执行可任意次循环的蝶形套娃运算,通过调用ifft递归体模块可实现任意点数的fft运算。可通过修改参数,改变例化嵌套的层级数来任意定制任意2的倍数的点数。提高了算子的重用性、灵活性,降低了版本维护和管理的经济和时间成本。

47、利用隐形状态机模块为每个递归层实现时序完全相同,但执行周期呈 2n 递增的数据流状态引导,使得不同层级间的递归调用不会产生任何运算缝隙,更不会产生数据丢包,在有限的资源内,将运算延时推向极致。并且, 隐形状态机模块的“跳转条件”和当前状态的“任务执行标识信号”被彻底“隐去”,从而减少了电路的面积和功耗。

48、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!