一种时序签核方法及装置、电子设备、存储介质与流程

本发明涉及集成电路,尤其涉及一种时序签核方法及装置、电子设备、存储介质。

背景技术:

1、芯片在委托晶圆厂进行加工前,需要进行时序签核(timing sign off )。时序签核是指对芯片设计的时序进行检查,以满足不同pvt(process voltage temperature,工艺电压温度)场景下芯片能够正常工作。

2、由于芯片生产中存在工艺变异(或称偏差variation),因此在签核时常常要对芯片的时序进行一定程度的悲观估计,然而过于悲观的估计又会严重影响芯片性能。为了避免对芯片时序过于悲观的估计,对于2维芯片而言,一般采用全局工艺角(global corner)(或称全局标准差)与局部偏差(local variation)相结合(即pocv(parametric on chipvariation,芯片上参数化的偏差))的方式来进行时序签核。

3、然而,对于3维集成芯片而言,由于各个晶粒(die)的工艺条件存在较大的随机性,如果采用上述方式进行跨晶粒签核,则一方面会存在较多的签核工艺角组合(或称签核条件组合(sign off condition)),从而使时序分析过于复杂,另一方面,随着晶粒堆叠数量的增加,上述签核方式也会越来越悲观,以致产生过度设计(over design),损失产品性能。

技术实现思路

1、有鉴于此,本发明实施例提供一种时序签核方法及装置、电子设备、存储介质,能够有效降低3维集成芯片时序签核的悲观程度和复杂度。

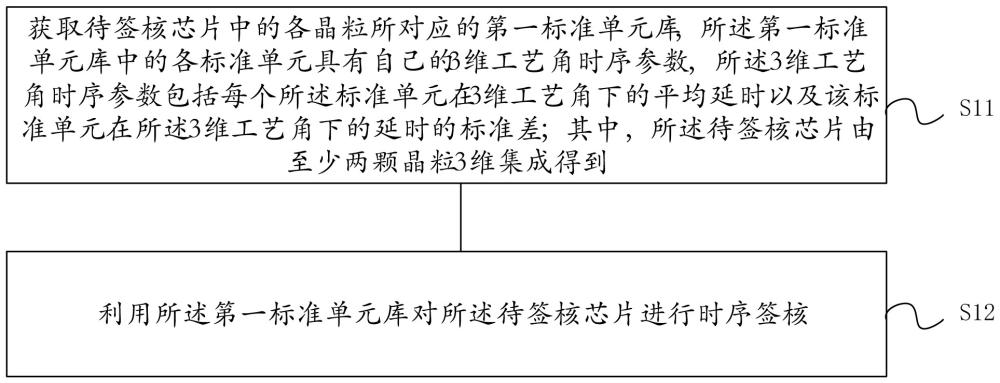

2、第一方面,本发明的实施例提供一种时序签核方法,包括:获取待签核芯片中的各晶粒所对应的第一标准单元库,所述第一标准单元库中的各标准单元具有自己的3维工艺角时序参数,所述3维工艺角时序参数包括每个所述标准单元在3维工艺角下的平均延时以及该标准单元在所述3维工艺角下的延时的标准差;其中,所述待签核芯片由至少两颗晶粒3维集成得到;利用所述第一标准单元库对所述待签核芯片进行时序签核。

3、在一种实施方式中,所述获取待签核芯片中的各晶粒所对应的第一标准单元库之前,所述方法还包括:获取所述待签核芯片中的各晶粒所对应的第二标准单元库,所述第二标准单元库中的每个标准单元具有自己的2维工艺角时序参数,所述2维工艺角时序参数包括:每个标准单元在2维条件下的平均延时及该标准单元在2维条件下的延时的局部标准差;根据每个所述标准单元在2维条件下的平均延时,确定该标准单元在所述3维工艺角下的平均延时,得到第一平均延时,并根据每个所述标准单元在2维条件下的延时的局部标准差,确定该标准单元在所述3维工艺角下的延时的标准差,得到第一标准差;将各所述第一平均延时和各所述第一标准差配置到所述第二标准单元库,以形成所述第一标准单元库。

4、在一种实施方式中,所述根据每个所述标准单元在2维条件下的平均延时,确定该标准单元在所述3维工艺角下的平均延时,得到第一平均延时包括:根据每个所述标准单元在2维条件下典型工艺角的平均延时,确定该标准单元在所述3维工艺角下的平均延时,得到所述第一平均延时。

5、在一种实施方式中,所述根据每个所述标准单元在2维条件下的延时的局部标准差,确定该标准单元在所述3维工艺角下的延时的标准差,得到第一标准差包括:通过晶圆厂提供的器件模型或通过仿真,确定所述待签核芯片中的每个晶粒中的每个器件的延时的总标准差和该器件的延时的局部标准差;根据每个所述器件的延时的总标准差和该器件的延时的局部标准差,确定该器件的标准差膨胀系数;根据每个所述标准单元在2维条件下的延时的局部标准差以及该标准单元所对应的所述器件的所述标准差膨胀系数,确定该标准单元在所述3维工艺角下的延时的标准差,得到所述第一标准差。

6、在一种实施方式中,每个所述器件的标准差膨胀系数等于该器件的延时的所述总标准差与该器件的延时的所述局部标准差的比值;每个所述标准单元的所述第一标准差等于该标准单元在2维条件下的延时的局部标准差与该标准单元所对应的所述器件的所述标准差膨胀系数的乘积。

7、在一种实施方式中,所述利用所述第一标准单元库对所述待签核芯片进行时序签核包括:基于所述第一标准单元库确定所述待签核芯片中的目标路径的第一路段的延时参数,并基于金属线延时模型确定所述目标路径的第二路段的延时参数,其中,所述第一路段为所述目标路径中位于每个晶粒内部的部分,所述第二路段为所述目标路径中位于相邻晶粒之间的部分;根据所述第一路段的延时参数和所述第二路段的延时参数,确定所述目标路径的延时参数;根据所述目标路径的延时参数是否处于预设的参数范围内,确定所述目标路径是否签核通过。

8、在一种实施方式中,所述第一路段的延时参数包括所述第一路段的平均延时以及所述第一路段的延时的标准差;所述第二路段的延时参数包括所述第二路段的平均延时以及所述第二路段的延时的标准差;所述根据所述第一路段的延时参数和所述第二路段的延时参数,确定所述目标路径的延时参数包括:将各所述第一路段的平均延时以及各所述第二路段的平均延时相加,得到所述目标路径的平均延时;将各所述第一路段的延时的标准差的平方和与各所述第二路段的延时的标准差的平方和相加,所得之和求算术平方根,得到所述目标路径的延时的标准差。

9、第二方面,本发明的实施例还提供一种时序签核装置,包括:第一获取单元,用于获取待签核芯片中的各晶粒所对应的第一标准单元库,所述第一标准单元库中的各标准单元具有自己的3维工艺角时序参数,所述3维工艺角时序参数包括每个所述标准单元在3维工艺角下的平均延时以及该标准单元在所述3维工艺角下的延时的标准差;其中,所述待签核芯片由至少两颗晶粒3维集成得到;签核单元,用于利用所述第一标准单元库对所述待签核芯片进行时序签核。

10、在一种实施方式中,所述装置还包括:第二获取单元,用于在获取待签核芯片中的各晶粒所对应的第一标准单元库之前,获取所述待签核芯片中的各晶粒所对应的第二标准单元库,所述第二标准单元库中的每个标准单元具有自己的2维工艺角时序参数,所述2维工艺角时序参数包括:每个标准单元在2维条件下的平均延时及该标准单元在2维条件下的延时的局部标准差;确定单元,用于根据每个所述标准单元在2维条件下的平均延时,确定该标准单元在所述3维工艺角下的平均延时,得到第一平均延时,并根据每个所述标准单元在2维条件下的延时的局部标准差,确定该标准单元在所述3维工艺角下的延时的标准差,得到第一标准差;配置单元,用于将各所述第一平均延时和各所述第一标准差配置到所述第二标准单元库,以形成所述第一标准单元库。

11、在一种实施方式中,所述确定单元包括第一确定模块,用于根据每个所述标准单元在2维条件下典型工艺角的平均延时,确定该标准单元在所述3维工艺角下的平均延时,得到所述第一平均延时。

12、在一种实施方式中,所述确定单元包括第二确定模块,用于:通过晶圆厂提供的器件模型或通过仿真,确定所述待签核芯片中的每个晶粒中的每个器件的延时的总标准差和该器件的延时的局部标准差;根据每个所述器件的延时的总标准差和该器件的延时的局部标准差,确定该器件的标准差膨胀系数;根据每个所述标准单元在2维条件下的延时的局部标准差以及该标准单元所对应的所述器件的所述标准差膨胀系数,确定该标准单元在所述3维工艺角下的延时的标准差,得到所述第一标准差。

13、在一种实施方式中,每个所述器件的标准差膨胀系数等于该器件的延时的所述总标准差与该器件的延时的所述局部标准差的比值;每个所述标准单元的所述第一标准差等于该标准单元在2维条件下的延时的局部标准差与该标准单元所对应的所述器件的所述标准差膨胀系数的乘积。

14、在一种实施方式中,所述签核单元包括:第三确定模块,用于基于所述第一标准单元库确定所述待签核芯片中的目标路径的第一路段的延时参数,并基于金属线延时模型确定所述目标路径的第二路段的延时参数,其中,所述第一路段为所述目标路径中位于每个晶粒内部的部分,所述第二路段为所述目标路径中位于相邻晶粒之间的部分;第四确定模块,用于根据所述第一路段的延时参数和所述第二路段的延时参数,确定所述目标路径的延时参数;第五确定模块,用于根据所述目标路径的延时参数是否处于预设的参数范围内,确定所述目标路径是否签核通过。

15、在一种实施方式中,所述第一路段的延时参数包括所述第一路段的平均延时以及所述第一路段的延时的标准差;所述第二路段的延时参数包括所述第二路段的平均延时以及所述第二路段的延时的标准差;所述第四确定模块,具体用于:将各所述第一路段的平均延时以及各所述第二路段的平均延时相加,得到所述目标路径的平均延时;将各所述第一路段的延时的标准差的平方和与各所述第二路段的延时的标准差的平方和相加,所得之和求算术平方根,得到所述目标路径的延时的标准差。

16、第三方面,本发明的实施例还提供一种电子设备,所述电子设备包括:处理器、存储器,所述处理器与所述存储器电连接;所述存储器用于存储可执行程序代码;所述处理器通过读取所述存储器中存储的可执行程序代码来运行与可执行程序代码对应的程序,以实现本发明的实施例提供的任一种时序签核方法。

17、第四方面,本发明的实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储有一个或者多个程序,所述一个或者多个程序可被一个或者多个处理器执行,以实现本发明的任一实施例提供的时序签核方法。

18、本发明的实施例提供的时序签核方法及装置、电子设备、存储介质,能够获取待签核芯片中的各晶粒所对应的第一标准单元库,利用所述第一标准单元库对所述待签核芯片进行时序签核。由于待签核芯片由至少两颗晶粒3维集成得到,而各晶粒对应的第一标准单元库中,每个标准单元都具有自己的3维工艺角时序参数,所述3维工艺角时序参数包括每个所述标准单元在3维工艺角下的平均延时以及该标准单元在所述3维工艺角下的延时的标准差,因此,在对待签核芯片进行时序签核时,就可以直接利用各标准单元的3维工艺角时序参数进行时序签核,由于3维工艺角时序参数是为3维集成情况专门定制的工艺角下的时序参数,因此,能更贴近3维集成应用场景,而无需像现有技术中那样利用各晶粒的2维签核工艺角进行各种组合,导致签核过于悲观度和复杂,从而能够有效降低3维集成芯片时序签核的悲观程度和复杂度。

- 还没有人留言评论。精彩留言会获得点赞!