仿真波形获取方法、装置、设备及存储介质与流程

本技术涉及软硬件协同仿真,尤其是涉及一种仿真波形获取方法、装置、设备及存储介质。

背景技术:

1、随着集成电路的规模不断扩大,芯片验证的时间占比越来越大,当前除了传统的模拟器(simulator),基于软硬件协同方式的仿真器(emulator)的使用越来越普遍,通过软硬件协同仿真验证的方式提高验证的效率。

2、在软硬件协同仿真中,probe(探针)/trigger(硬件断点功能)/getvalue(dut内部值)作为最常见的debug手段。软件通过scemi协议(sce-mi:standard co-emulationmodeling interface)完成对硬件侧基本单元(macro)的配置,达到debug信号的目的。传统的amd和intel的fpga厂商均提供了fpga的在线逻辑分析仪,为fpga的调试提供观察波形的便捷性。scemi协议,是一种用于软硬件交互的标准接口协议,主要用于软硬件协同验证环境中,以实现软件模型与硬件仿真器之间的无缝通信和数据交互。

3、然而,使用原厂配套的在线逻辑分析仪抓取仿真波形时,需通过jtag导出到上位机中,由于jtag存在传输速度慢的问题,从而可能会使得仿真验证速度大大降低,进而导致仿真的效率降低。

技术实现思路

1、为了有助于解决使用原厂配套的在线逻辑分析仪抓取仿真波形时,需通过jtag导出到上位机中,由于jtag传输速度慢,从而可能会使得仿真验证速度大大降低,进而导致仿真的效率低的问题,本技术提供一种仿真波形获取方法、装置、设备及存储介质。

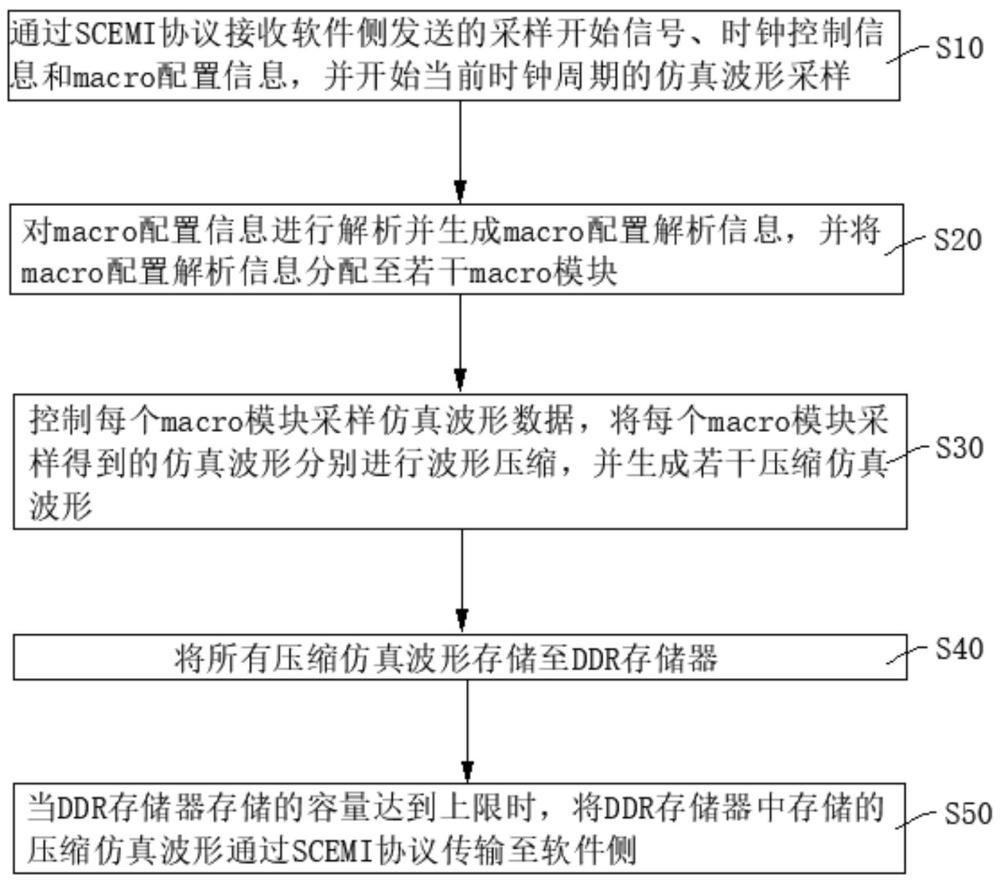

2、第一方面,本技术提供一种仿真波形获取方法,采用如下技术方案:所述方法应用于仿真波形获取系统的硬件侧,所述仿真波形获取系统的硬件侧包括ddr存储器和若干探针处理模块,所述方法包括:

3、通过scemi协议接收软件侧发送的采样开始信号、时钟控制信息和macro配置信息,并开始当前时钟周期的仿真波形采样;

4、对所述macro配置信息进行解析并生成macro配置解析信息,并将所述macro配置解析信息分配至若干所述探针处理模块;

5、控制每个所述探针处理模块采样仿真波形数据,将每个所述探针处理模块采样得到的所述仿真波形分别进行波形压缩,并生成若干压缩仿真波形;

6、将所有所述压缩仿真波形存储至所述ddr存储器;

7、当所述ddr存储器存储的容量达到上限时,将所述ddr存储器中存储的压缩仿真波形通过scemi协议传输至软件侧。

8、在一个具体的可实施方案中,所述macro配置解析信息包括macro标识信息,所述将所述macro配置解析信息分配至若干所述探针处理模块包括:

9、根据所述macro标识信息将所述macro配置解析信息分配至对应的所述探针处理模块。

10、在一个具体的可实施方案中,当前时钟周期内包含若干帧仿真波形数据,所述将每个所述探针处理模块采样得到的所述仿真波形分别进行波形压缩,并生成若干压缩仿真波形包括:

11、判断所述仿真波形的数据帧格式,所述仿真波形的数据帧格式包括i帧和p帧;

12、若所述仿真波形的数据帧格式为i帧,则将当前仿真波形的数据帧内的相邻的两组预设位数据按位依次进行比对,并将比对不一致的数据进行存储并生成所述压缩仿真波形;

13、若所述仿真波形的数据帧格式为p帧,则将相邻两帧的仿真波形的数据按位依次进行比对,并将比对不一致的数据进行存储并生成所述压缩仿真波形。

14、在一个具体的可实施方案中,在所述将每个所述探针处理模块采样得到的所述仿真波形分别进行波形压缩,并生成若干压缩仿真波形之后,还包括:

15、控制每个所述探针处理模块输出采样完成信号;

16、将所有所述采样完成信号进行与计算,并将与计算后的采样完成信号的结果传输至软件侧。

17、在一个具体的可实施方案中,所述仿真波形获取系统的硬件侧还包括合并模块,在所述将所述压缩仿真波形存储至所述ddr存储器之前,还包括:

18、将所述压缩仿真波形按顺序依次合并成一路数据,并生成合并仿真波形;

19、其中,所述压缩仿真波形的大小与所述ddr存储器的接口位宽大小一致;

20、所述将所有所述压缩仿真波形存储至所述ddr存储器包括:

21、将所述合并仿真波形存储至所述ddr存储器。

22、在一个具体的可实施方案中,所述仿真波形获取系统的硬件侧还包括断点模块;

23、在所述将所述macro配置解析信息分配至若干所述探针处理模块的同时,将所述macro配置解析信息传输至所述断点模块。

24、在一个具体的可实施方案中,所述仿真波形获取系统的硬件侧还包括断点波形获取模块;

25、在所述将每个所述探针处理模块采样得到的所述仿真波形分别进行波形压缩,并生成若干压缩仿真波形之后,还包括:

26、将若干所述压缩仿真波形传输至所述断点模块,并控制所述断点模块根据所述macro配置解析信息生成与所述压缩仿真波形对应的断点信号;

27、利用所述断点波形获取模块根据所述断点信号生成断点仿真波形;

28、所述将所有所述压缩仿真波形存储至所述ddr存储器包括:

29、将所述断点仿真波形存储至所述ddr存储器。

30、第二方面,本技术提供一种仿真波形获取装置,采用如下技术方案:所述装置应用于仿真波形获取系统的硬件侧,所述仿真波形获取系统的硬件侧包括ddr存储器和若干探针处理模块,所述装置包括:

31、信息接收模块,用于通过scemi协议接收软件侧发送的采样开始信号、时钟控制信息和macro配置信息,并开始当前时钟周期的仿真波形采样;

32、信息解析模块,用于对所述macro配置信息进行解析并生成macro配置解析信息,并将所述macro配置解析信息分配至若干所述探针处理模块;

33、波形采样模块,用于控制每个所述探针处理模块采样仿真波形数据,将每个所述探针处理模块采样得到的所述仿真波形分别进行波形压缩,并生成若干压缩仿真波形;

34、波形存储模块,用于将所有所述压缩仿真波形存储至所述ddr存储器;

35、波形传输模块,用于当所述ddr存储器存储的容量达到上限时,将所述ddr存储器中存储的压缩仿真波形通过scemi协议传输至软件侧。

36、第三方面,本技术提供一种计算机设备,采用如下技术方案:包括存储器和处理器,所述存储器上存储有能够被处理器加载并执行如上述任一种仿真波形获取方法的计算机程序。

37、第四方面,本技术提供一种计算机可读存储介质,采用如下技术方案:存储有能够被处理器加载并执行上述任一种仿真波形获取方法的计算机程序。

38、综上所述,本技术具有以下有益技术效果:

39、通过软硬件协同仿真获取仿真波形以实现对芯片的仿真验证。在硬件侧,通过对探针处理模块的配置,实现对仿真波形的采样,采样得到的波形数据存储到ddr存储器中,再读取ddr存储器中的数据并通过scemi协议传输到软件侧进行解码和显示,整个方法过程中不涉及采用jtag进行波形的抓取以及对波形的传输,采用探针处理模块进行仿真波形的采样以及将数据输出至ddr存储器,可以提高硬件内部的访问效率,从而可以提高仿真验证效率,并且可以极大提高基于硬件仿真加速器验证手段的灵活性。此外,对采样得到的波形数据进行波形压缩可以提高ddr存储器的利用率。

- 还没有人留言评论。精彩留言会获得点赞!