一种高速总线配置电路、配置方法及通信方法与流程

本发明涉及数据通讯,具体涉及一种高速总线配置电路、配置方法及通信方法。

背景技术:

1、高速总线是同步串行总线,是微处理器单元和外围设备之间进行通信的同步串行端口。高速总线系统可直接与各个厂家生产的多种标准外围器件直接连接。一般情况下该高速总线正常通信需要4根信号线,其中有从机选择信号线set、串行时钟信号线sclk、主机发送数据线tx和主机接收数据线rx。

2、在传统模式正常通信时,主机设备与每一个从机设备之间都有一根set信号线,主机设备通过set信号选择与哪个从机设备进行通信。系统中随着从机设备的增加,set信号线也随之增加,随着从机数量的增加,会增加主机设备mcu引脚的使用,增加了硬件电路的设计难度和pcb的布局;因此,从及设备数量不固定时,主机设备连接的set信号线的数量也无法确定。在实际应用中,存在某些应用场景下从机数量不固定的情况,设备处理器mcu引脚有限,这就导致传统方式存在一定弊端,限制了系统中的从机数量。

3、通过主机设备启动时钟信号发起通信,从机设备根据主机设备提供的时钟信号被动接收和发送数据,在传统的通信机制中,主机需要先启动时钟信号发送一帧报文,从机接收到报文后准备应答报文,然后主机第二次启动时钟信号发送一帧报文,从机接收到时钟信号同步把应答报文发送给主机设备,在一主多从的系统中切换从机时都需要进行两次通信。主机设备与某一个从机设备进行通信需要启动两次请求,在第二次请求时从机设备回复应答数据,主从设备间通信时间长,通信效率较低。

技术实现思路

1、针对现有技术的不足,本发明提供一种高速总线配置电路、配置方法及通信方法,优化了电路设计,保证主机设备启动时钟信号时发送请求数据时同步有从机设备返回响应数据,与传统全双工通信模式下的主从一对一通信机制相比,通信时间缩短50%,提高了通信效率。

2、本发明是通过如下技术方案实现的:

3、提供一种高速总线配置电路,包括1个主机设备和n个从机设备,主机设备和n个从机设备均连接在有时钟信号线sck、主机发送数据信号线tx和从机发送数据信号线rx组成的总线上;主机设备配置1个输出引脚gpioa,为从机设备提供使能信号;每个从机设备均配置2个gpio引脚,一个为输入引脚gpio1,为本机使能接收引脚,另一个为输出引脚gpio2,为使能输出引脚,为下一从机设备提供使能信号,主机设备和n个从机设备依次通过gpio引脚顺序相连;每个从机设备的rx接口处串联10ω的电阻匹配阻抗,并通过1kω电阻与3.3v正电压连接形成的上拉电路将从机设备发出的高电平信号钳位到高电平。

4、进一步的,主机设备的输出引脚gpioa与第1个从机设备的输入引脚gpio1相连,第i个从机设备的输出引脚gpio2与第i+1个从机设备的输入引脚gpio1相连。

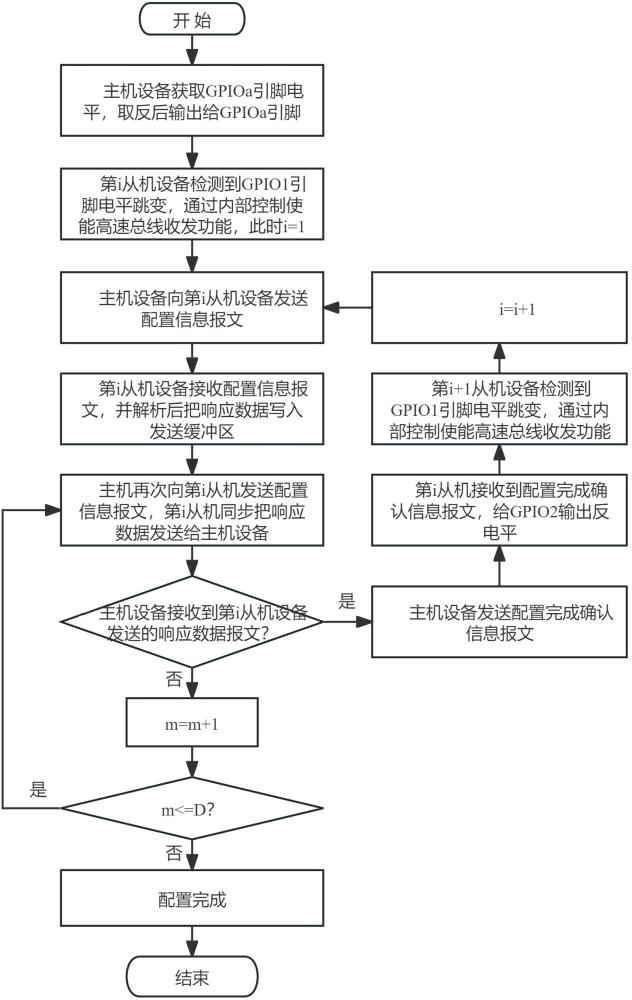

5、一种高速总线配置电路的配置方法,包括以下步骤:

6、p1、主机设备给gpioa引脚输出一个反电平以使能第1个从机设备,此时i=1;

7、p2、第i个从机设备的gpio1输入引脚检测到电平跳变,通过第i个从机设备内部控制使能第i个从机设备高速总线收发功能,等待接收主机设备发送的配置信息;

8、p3、主机设备通过tx信号线发送第i个从机设备的配置信息报文,配置信息报文中包括第i个从机设备的地址,其中配置的第i个从机设备的地址号为i;

9、p4、第i个从机设备接收并解析步骤p3中的配置信息报文,将主机设备分配的地址号写入本地内存,并把包含本地设备类型的信息回复报文写入发送缓冲区,等待主机设备下一次起动数据访问时将信息回复报文发送给主机设备;

10、p5、主机设备再次通过tx信号线向第i个从机设备发送步骤p3描述的配置信息报文,通过rx信号线同步接收第i个从机设备发送的步骤p4中的信息回复报文;

11、p6、如果主机设备接收到步骤p5描述的信息回复报文,准备配置完成确认信息报文写入主机发送缓冲区,等待下次时钟起动时执行步骤p7;如果主机设备未接收到步骤p5描述的信息回复报文,则返回执行步骤p5,同时记录返回执行步骤p5的次数m,当m>d时,主机设备默认所有从机设备均已配置完成,至此结束配置,d>1;

12、p7、主机设备通过tx信号向第i个从机设备发送配置完成确认信息报文;

13、p8、第i个从机设备接收到步骤p7描述的配置完成确认信息报文后,确保总线空闲后,通过第i个从机设备内部控制去使能从机设备i高速总线收发功能,同时给gpio2引脚输出一个反电平;

14、p9、第i+1个从机设备检测到gpio1输入引脚的电平跳变,通过第i+1个从机设备内部控制使能第i+1个从机设备的高速总线收发功能,等待接收主机设备发送的配置信息;

15、p10、使i增加1,顺序执行步骤p3-p9。

16、进一步的,主机设备对从机设备配置过程中,每一时刻至多有唯一一个从机设备高速总线收发功能被使能,避免其他从机设备向rx信号线发送数据干扰主机接收数据。

17、一种使用高速总线配置方法的高速总线通信方法,从机设备配置完成进入正常访问阶段,主机访问从机设备的过程包括以下步骤:

18、t1:主机设备以50μs的定时间隔启动定时器,在定时器中断中通过tx信号线向外发送数据用于访问从机设备,访问从机设备的顺序按照配置的地址号从小到大依次循环访问;

19、t2:主机设备给gpioa引脚输出一个反电平以通知第i个从机设备主机将要访问第i个从机设备,此时i=1;

20、t3:第i个从机设备检测到gpio1输入引脚的电平跳变,通过第i个从机设备内部控制使能第i个从机设备的高速总线收发功能,等待接受主机设备发送的请求数据报文;

21、t4:主机设备进入定时器中断,通过tx信号线向第i个从机设备发送请求数据报文;

22、t5:第i个从机设备通过tx总线接收到主机发送的请求数据报文后,解析数据并准备响应数据报文写入缓存,等待主机下一个定时器周期内时钟信号起动时发送给主机设备;同时,第i个从机设备给gpio2引脚输出一个反电平;

23、t6:第i+1个从机设备检测到gpio1输入引脚的电平跳变,通过第i+1个从机设备内部控制使能第i+1个从机设备的高速总线收发功能,等待接收主机设备发送的请求数据报文;

24、t7:主机设备进入定时器中断,通过tx信号线向第i+1个从机设备发送请求数据报文;

25、t8:第i个从机设备在主机设备向第i+1个从机设备发送请求数据报文的同时,通过rx信号线向主机设备发送步骤t5描述的响应数据,等待发送完成后,内部控制去使能第i个从机设备的高速总线收发功能;

26、t9:使i增加1,当i≤n时,顺序执行步骤t5-t8;当i>n时,执行步骤t2。

27、进一步的,在正常通信过程中有两个从机设备被使能了高速总线收发功能,两个从机设备同时接收主机发送的数据报文,但只有一个从机设备同步向主机设备发送响应报文。

28、本发明的有益效果:

29、一、本发明摒弃传统硬件电路设计思路,提供了一种新的电路设计思想,去掉了通信过程中使用的从机选择信号线,简化了电路设计,并通过软件对各设备之间配置信号线的控制实现高速总线的配置和通信。在设计过程中完全舍弃set信号接口,通过另外的一个配置信号线和从机设备的软件机制实现主机设备与从机设备的正常通信,这样在一主多从的总线系统中,大大减少了主机设备mcu的gpio引脚使用,同时简化了电路设计,优化了pcb布局,缩小了pcb尺寸;同时能实现在总线允许的距离范围内任意数量从机设备的扩展。

30、二、本发明中通过对高速总线通信硬件电路的优化设计,在主机设备配置从机设备过程中,通过对主机设备与从机设备以及从机设备与从机设备之间的配置输入输出引脚的信号控制,实现了在配置过程中主机设备与唯一从机设备的数据交互。

31、三、主机设备与唯一从机设备进行通信,确保不会因为其他从机参与通信而增加干扰可能性,从而确保配置成功。主从一对一通信,防止其他从机回复时产生的信号干扰。

32、四、主机设备根据预先配置的从机设备地址1~n,按照与主机设备距离从近到远的顺序依次访问从机设备,启动通信后第i和i+1个从机设备同时使能高速总线收发功能,控制实现正常通信过程中有且只有一个主机设备和两个前后相连的从机设备同时使能高速总线收发数据功能,保证主机设备启动时钟信号时发送请求数据时同步有从机设备返回响应数据,与传统全双工通信模式下的主从一对一通信机制相比,通信时间缩短50%,提高了通信效率。本发明中主机设备第一次给1从机设备发送请求数据,此时1从机不回复,然后主机向2从机发送数据时1从机回复,同理主机向n从机发送数据时,n-1从机回复,这样能实现主机访问n个从机的时间缩短50%,主机发送一次请求数据,从机回复一次应答数据,缩短了主从设备间通信时间,提高了通信效率。

- 还没有人留言评论。精彩留言会获得点赞!