存算一体处理器、数据处理方法和计算机设备与流程

本技术涉及新型计算领域,特别是涉及一种存算一体处理器、数据处理方法和计算机设备。

背景技术:

1、近年来,随着人工智能和大型模型应用的兴起,对处理器算力的需求不断增加。尽管大部分处理器仍然基于冯诺依曼架构,以满足算力增长的需求,但为了开发更高算力、更高能效的加速计算芯片,需要解决传统冯诺依曼架构中的“存储墙”问题。这种问题需要一种新型架构体系,通过将存储和计算融合在一起,从而解决存算分离的问题。

2、存算一体计算(computing-in-memory,cim)是一种新兴的计算架构范式,旨在将计算功能与存储功能集成在同一处理单元或模块中。传统计算机架构中,数据通常需从存储器传输到处理器进行计算,这种数据传输会消耗大量能量和时间。存算一体计算通过在新型存储器上执行计算任务,避免了这种数据移动,从而提高了计算效率和能效。但是,目前的存算一体架构大多采用串行流水模式处理数据,计算效率有待提升。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种能够提升计算效率的存算一体处理器、数据处理方法和计算机设备。

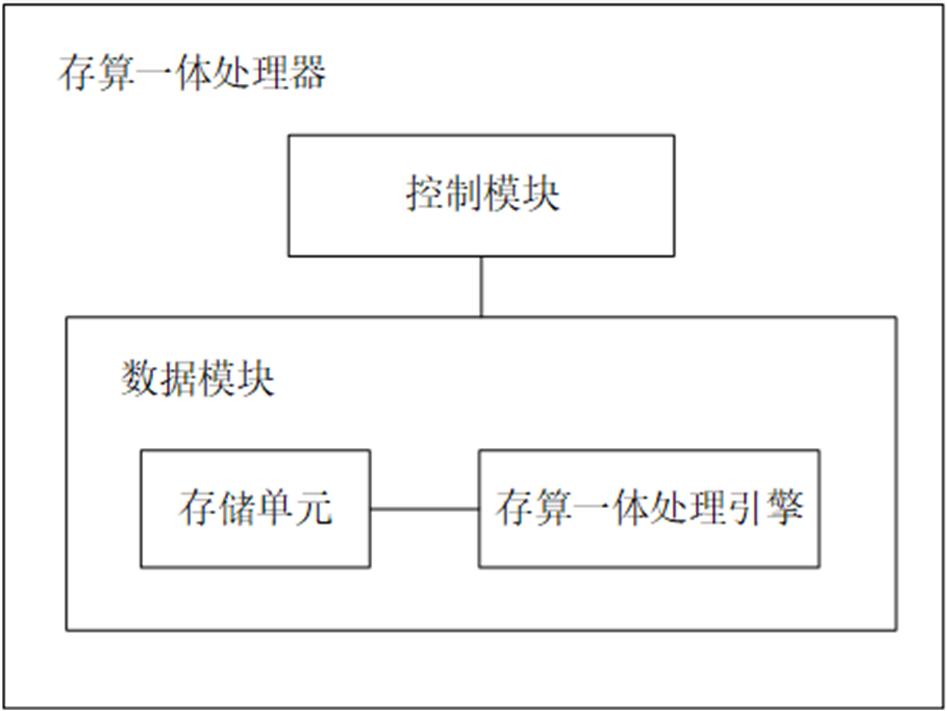

2、第一方面,本技术提供了一种存算一体处理器。包括:控制模块和数据模块,所述控制模块与所述数据模块连接;其中,所述数据模块包括存储单元和存算一体处理引擎,所述存算一体处理引擎与所述存储单元连接;

3、所述存算一体处理引擎包括n个存算一体处理单元和第一计算器组,所述存算一体处理单元与所述第一计算器组连接;各所述存算一体处理单元包括m个存算一体阵列单元和第二计算器组,所述存算一体阵列单元与所述第二计算器组连接;n为和m均为大于1的自然数;各所述存算一体阵列单元包括存算一体阵列、阵列控制单元和读出电路,所述存算一体阵列包括多个交叉排布的存算器件;

4、所述控制模块用于控制所述存算一体处理引擎从所述存储单元获取数据,并指示所述存算一体处理引擎计算所获取的数据。

5、在其中一个实施例中,所述第一计算器组包括第一累加器组和/或第一量化器组;其中,所述第一累加器组包括n个累加器,所述累加器与所述存算一体处理单元逐一对应连接;所述第一量化器组包括n个量化器,所述量化器与所述存算一体处理单元逐一对应连接;

6、所述第二计算器组包括第二累加器组和/或第二量化器组;其中,所述第二累加器组包括m个累加器,所述累加器与所述存算一体阵列单元逐一对应连接;所述第二量化器组包括m个量化器,所述量化器与所述存算一体阵列单元逐一对应连接。

7、在其中一个实施例中,所述数据模块还包括:数据预载单元、通道选择单元和数据预处理单元;其中,

8、所述数据预载单元的输入端与所述存储单元连接,所述数据预载单元的输出端与所述通道选择单元的输入端连接,所述数据预载单元用于预先从所述存储单元中加载数据;

9、所述通道选择单元的输入端还与所述存储单元连接,所述通道选择单元的输出端与所述数据预处理单元的输入端连接,所述通道选择单元用于从所述存储单元和所述数据预载单元中选择待计算的数据;

10、所述数据预处理单元的输出端与所述存算一体处理引擎连接,所述数据预处理单元用于对所述通道选择单元输出的数据进行预处理。

11、在其中一个实施例中,所述数据预载单元包括n个寄存器组,所述寄存器组与所述数据预处理单元连接;所述数据预处理单元用于对所述通道选择单元输出的数据进行预处理,包括:

12、所述数据预处理单元对各所述寄存器组的数据进行预处理,并将预处理结果传输至对应的所述存算一体处理单元;或者,

13、所述数据预处理单元对多个所述寄存器组的数据进行聚合,并将聚合结果传输至预设的其中一个所述存算一体处理单元中。

14、在其中一个实施例中,所述数据模块还包括:数据后处理单元,所述数据后处理单元的输入端与所述存算一体处理引擎连接,所述数据后处理单元的输出端与所述存储单元连接;其中,

15、所述数据后处理单元用于对所述存算一体处理引擎的计算结果进行后处理,并将后处理结果传输至所述存储单元。

16、在其中一个实施例中,所述数据模块还包括:写验证单元,所述写验证单元分别与所述存算一体处理引擎和所述存储单元连接;其中,

17、所述写验证单元用于配置所述存算一体处理引擎的写验证编程模式,所述写验证编程模式包括第一模式和第二模式;其中,

18、在所述第一模式下,通过按单元立即数写指令对单个地址的所述存算器件进行写验证编程;

19、在所述第二模式下,通过按地址写指令从所述存储单元中取值后对同一行地址的所述存算器件进行写验证。

20、在其中一个实施例中,所述数据模块还包括:数据写回单元,所述数据写回单元分别与所述存算一体处理引擎和所述存储单元连接;其中,

21、所述数据写回单元用于将所述存算一体处理引擎的计算结果按照写回数据的顺序,依序返回至所述存储单元中。

22、在其中一个实施例中,所述数据写回单元包括:n个第一写回fifo、w个第二写回fifo、数据通路开关和仲裁器;w为大于等于1的自然数;

23、所述第一写回fifo用于暂存所述存算一体处理引擎生成的写回数据和写回地址,并基于所述写回地址发送请求至所述仲裁器;

24、所述仲裁器用于根据所述请求的优先级,向最高优先级请求反馈确认信号;

25、所述数据通路开关用于选择获得确认信号的目标写回数据,使得所述目标写回数据传输至所述第二写回fifo;

26、所述第二写回fifo用于暂存所述目标写回数据和相应写回地址,并当所述存储单元可用时,将所述目标写回数据基于相应写回地址写入所述存储单元。

27、在其中一个实施例中,所述控制模块包括:控制单元、寄存器单元和指令单元,所述控制单元分别与所述寄存器单元、所述指令单元、所述数据模块连接;其中,

28、所述寄存器单元用于配置所述数据模块的运行模式、操作地址,以及记录所述数据模块的运行状态;

29、所述控制单元用于生成控制信号,并基于所述控制信号控制所述寄存器单元和所述数据模块;

30、所述指令单元用于定义指令集,所述指令集包括用于供所述控制单元执行的控制指令,以及供所述存算一体处理引擎执行的计算指令。

31、在其中一个实施例中,所述控制指令包括以下至少之一:加载数据指令、对齐加载数据指令、存储指令、寄存器配置指令、按立即数写存算器件指令、按数据写存算器件指令、数据发送指令、模块控制指令;

32、所述计算指令包括以下至少之一:数据预载的立即写回向量矩阵乘法指令、数据预载的不写回向量矩阵乘法指令、数据立即取的立即写回向量矩阵乘法指令、数据立即取的不写回向量乘法指令、数据预载的立即写回矩阵乘法指令、数据预载的不写回矩阵乘法指令、数据预处理后的立即写回矩阵乘法指令、数据预处理后的不写回矩阵乘法指令。

33、第二方面,本技术提供了一种数据处理方法。应用于上述第一方面所述的存算一体处理器,所述方法包括:

34、控制模块生成控制信号,并将所述控制信号发送至数据模块;

35、所述数据模块基于所述控制信号执行数据访存操作和数据计算操作。

36、在其中一个实施例中,所述数据模块基于所述控制信号执行数据访存操作和数据计算操作,包括:

37、将第 l层节点的特征向量载入数据预载单元中,并通过数据预处理单元进行聚合处理,得到聚合结果; l为正整数;

38、将所述聚合结果输入至存算一体处理引擎中进行向量矩阵计算,并将得到的向量矩阵计算结果通过数据后处理单元进行非线性激活函数计算,得到第 l+1层的特征向量。

39、在其中一个实施例中,将第 l层节点的特征向量载入数据预载单元中,并通过数据预处理单元进行聚合处理,得到聚合结果,包括:

40、以相邻的n个周期为一组,将所述第 l层中目标节点及其邻近节点的特征向量中当前批次的数据按照周期依次载入所述数据预载单元中;n为大于1的自然数;

41、在第n+1个周期中,将所述第l层的目标节点的特征向量中下一批次的数据载入所述数据预载单元中,以及通过所述数据预处理单元聚合上一批次载入所述数据预载单元中的数据,得到聚合后点嵌入向量;

42、将所述聚合后点嵌入向量输入至所述存算一体处理引擎中进行所述向量矩阵计算。

43、第三方面,本技术提供了一种计算机设备。所述计算机设备中部署有上述第一方面所述的存算一体处理器。

44、上述存算一体处理器、数据处理方法和计算机设备,通过将存储单元和存算一体处理引擎内置于处理器中,以及在存算一体处理引擎中设置多个存算一体处理单元,如此,在实现存算一体的基础上,以单个存算一体处理单元为最小运算单元处理数据,支持数据并行计算,提升了计算效率。

- 还没有人留言评论。精彩留言会获得点赞!