防止存储单元数据遗失的方法与流程

1.本发明提供了一种防止存储单元数据遗失的方法,尤指可正确读取存储单元的数据的防止数据遗失方法,在对存储单元进行清除后注入少许电子,使隧穿氧化层内不易累积电子,并不阻止源极、漏极间的通道形成导通,达到降低读取存储单元数据发生错误的机会的目的。

背景技术:

2.存储器用以存储电子信息或数据等的半导体元件,而通过半导体工艺所成型的半导体存储器装置,可分类成非易失性半导体装置(例如,闪存装置)及易失性半导体装置〔例如,动态随机存取存储器装置(dram) 、静态随机存取存储器装置(sram)等〕;其中,闪存(flash memory) 为一种非易失性(non-volatile)半导体存储装置,并在缺乏外部电源供应时,还能将存储在存储器内部的数据予以保存,且闪存具有可重复写入及被抹除等优点,所以被应用在各式可携式电子装置,如平板计算机、智能型手机、数字相机、个人数字助理或游戏机等产品。

3.而目前所应用的闪存为可划分成许多存储区块,并于每个存储区块具有许多存储单元,且每个存储单元供用于记录一个位的数据,但是存储单元具有控制栅极(control gate,cg)、浮置栅极(floating gate,fg)、源极(source,s)与漏极(drain,d),则存储单元的数据是以浮置栅极( fg)中所存储的电子量多寡而定,则在对存储器的存储单元写入数据前,都会先进行清除的步骤,然后再进行写入作业,将电子注入浮置栅极(fg )内,且当浮置栅极(fg)内部具有足够的电子时,在浮置栅极(fg) 内变会形成一电场效应,且阻止源极(s)与漏极(d)之间的通道形成导通,则于读取数据时可以测量到很小电流(leakage)或是没有测量到电流,表示为状态“0”或逻辑“0”(logic“0”);但若浮置栅极(fg)内部没有足够的电子达到可阻止源极与漏极(s-d)之间的通道形成导通时,则因造成源极与漏极(s-d)之间的通道导通,因此在读取时,则会测量到足够大的电流(vgs>vth),表示状态为“1”或逻辑“1”(logic

“ꢀ

1”)。

4.且因半导体存储器装置发生在工艺上的瑕疵时,有可能经一段时间后,就会有热电子被卡制在浮置栅极(fg)与控制栅极(cg)之间的隧穿氧化层(tunnel oxide,to)内,并使得电子持续累积在隧穿氧化层(to )内,造成读取存储器时在漏极与源极(d-s)间的通道无法形成导通,即浮置栅极(fg)内部没有足够的电子可阻止漏极与源极(d-s)间的通道形成导通,而造成读取数据时原本应是状态“1”或逻辑“1”(logic

“ꢀ

1”)的情形,因为受到持续累积在隧穿氧化层(to)内的电子影响,即造成读取存储器数据时读取到状态“0”或逻辑“0”(logic“0”)的错误结果,则将欲存储的存储单元数据写入存储器的浮置栅极(fg)内,并覆盖住原来的存储单元数据,因此造成存储器数据遗失的缺失。

5.因此,如何解决目前存储器装置的浮置栅极受到隧穿氧化层内部累积的电子影响,读取数据时容易发生状态错误的问题与麻烦,且导致浮置栅极内部存储的存储单元被覆盖,造成浮置栅极内部数据遗失等的缺失及困扰,即为从事此行业的相关厂商所亟欲研

究改善的方向所在。

技术实现要素:

6.因此,发明人有鉴于上述的问题与缺失,乃搜集相关资料,经由多方评估及考虑,并以从事于此行业累积的多年经验,经由不断试作及修改,始设计出此种可通过存储器单元的浮置栅极内注入少量电子,并与隧穿氧化层内的电子形成相斥,避免在隧穿氧化层内部累积电子,不会阻止漏极与源极之间的通道导通,达到降低读取存储器数据时发生错误情形的目的的防止存储器数据遗失的方法的发明专利诞生。

7.本发明的主要目的乃在于该存储单元的晶体管,于半导体基底(bulk )上成型源极(source,s)、漏极(drain,d)与通道,且通道上成型隧穿氧化层(tunnel oxide,to)、浮置栅极(floating gate,fg)、隧穿氧化层(to)及控制栅极(control gate,cg),而先对浮置栅极进行清除作业,并使用微弱电场,将少许电子注入浮置栅极内部,供浮置栅极内部保持少许电子,并导通源极与漏极间的通道,且浮置栅极内部少许电子与二侧隧穿氧化层内部电子形成相互排斥,避免电子累积在二侧隧穿氧化层内,可供正常读取浮置栅极内部数据,利用正常写入电场对浮置栅极注入正常电子,阻止源极与漏极间的通道导通,则可将数据写入浮置栅极内,而不会覆盖住其它数据,并达到有效防止存储器数据遗失的目的。

8.本发明的次要目的乃在于该存储单元欲写入数据前,针对浮置栅极进行清除(erase)作业,可于控制栅极(control gate,cg)施加9~12伏特 (v)等的电压,并于源极(source,s)施予6伏特(v)等电压,则读取浮置栅极(floating gate,fg)的状态为“1”,则不致阻止源极与漏极( s-d)之间的通道形成;且当针对浮置栅极进行写入(program)作业,则于控制栅极(control gate,cg)施加12伏特(v)等的电压,并于漏极( drain,d)施予7伏特(v)等电压,则写入后的浮置栅极(floating gate ,fg)的状态为“0”,进而阻止源极与漏极(s-d)之间的通道形成。

9.本发明的另一目的乃在于该存储单元欲写入数据时,可采用通道热电子编成〔che〕或〔flowler-nordheim,fn〕通道法,将预定电子量注入浮置栅极(floating gate,fg)内部。

附图说明

10.图1为本发明的流程图。

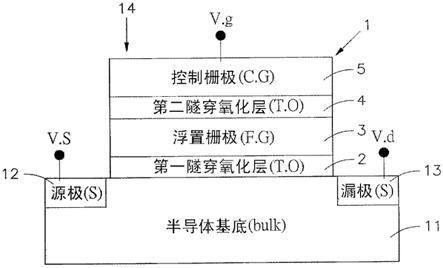

11.图2为本发明存储单元构造的侧视剖面图。

12.【符号说明】

13.1、晶体管

14.11、半导体基底

15.12、源极

16.13、漏极

17.14、通道

18.2、第一隧穿氧化层

19.3、浮置栅极

20.4、第二隧穿氧化层

21.5、控制栅极

具体实施方式

22.为达成上述目的与功效,本发明所采用的技术手段及其构造、实施的方法等,兹绘图就本发明的优选实施例详加说明其特征与功能如下,以利于完全了解。

23.请参阅图1、图2所示,为本发明的流程图、存储单元构造的侧视剖面图,由图中所示可以清楚看出,本发明防止存储器数据遗失的方法,其中:

24.该存储器单元的晶体管1包括半导体基底11、成型于半导体基底(bulk) 11上的源极(source,s)12、漏极(drain,d)13,并于源极12、漏极 13之间形成通道14,则于通道14上成型有依序堆叠的第一隧穿氧化层 (tunnel oxide,to)2、浮置栅极(floating gate,fg)3、第二隧穿氧化层(tunnel oxide,to)4及控制栅极(control gate,cg)5,以供第一隧穿氧化层(to)2成型于半导体基底11与浮置栅极(fg)3之间,而第二隧穿氧化层(to)4则成型于浮置栅极(fg)3另侧与控制栅极(cg) 5之间,而欲将数据写入存储器单元防止数据遗失方法的步骤为:

25.(a)欲将数据写入存储单元的晶体管1时,先对浮置栅极(fg)3 进行清除作业。

26.(b)使用低于正常写入的微弱电场,并将少许电子注入浮置栅极(fg) 3内部。

27.(c)而于浮置栅极(fg)3内部保持少许电子,则可供存储单元晶体管1的源极(s)12与漏极(d)13之间的通道14形成导通。

28.(d)且浮置栅极(fg)3内部少许电子与二侧第一隧穿氧化层(to) 2、第二隧穿氧化层(to)4内部的电子形成相互排斥状态,避免电子累积在二侧第一隧穿氧化层(to)2、第二隧穿氧化层(to)4内,以供正常读取浮置栅极(fg)3内部的数据。

29.(e)再利用正常写入电场对浮置栅极(fg)3注入正常电子,即可阻止存储单元晶体管1的源极(s)12与漏极(d)13间的通道形成导通,则可将数据写入浮置栅极(fg)3内部。

30.而上述该步骤(a)中,欲针对浮置栅极(fg)3进行清除(erase) 作业时,可于控制栅极(cg)5施加〔9~12〕伏特(v)电压或其它可用的电压等,并于源极(s)12施予〔6〕伏特(v)电压或其它可用的电压等,则读取浮置栅极(fg)3的状态即为“1”,而可将电子信息或数据等的存储单元予以写入该存储单元晶体管1的浮置栅极(fg)3内部;且上述该步骤(e)中,欲针对浮置栅极(fg)3进行写入(program)作业时,则于控制栅极(cg)5施加〔12〕伏特(v)的电压或其它可用的电压等,并于漏极(d)13施予〔7〕伏特(v)电压或其它可用的电压等,则写入后的浮置栅极(fg)3的状态则为“0”,即于存储单元晶体管1的该浮置栅极(fg)3内部,已经写入电子信息或数据等的存储单元;并可达到对存储单元晶体管1的上的浮置栅极(fg)3读取时降低读取错误机会的目的。

31.另,上述该步骤(b)及步骤(e)中,欲将电子注入浮置栅极(fg) 3时,可采用通道热电子编成〔che〕或〔flowler-nordheim,fn〕通道法等方式,将预定电子量注入浮置栅极(fg)3内部。

32.且一般进行读取(read)闪存的晶体管1的状态时(为“1”或“0”),可侦测流经漏极(d)13的电流量(vd),而当流经漏极(d)13的电流量(vd)为大于一门坎限值(v

th

)时,(vd>v

th

),则漏极(d)13与源极(s)12之间会形成导通的(d-s)通道14;欲进行测量漏极(d)13 流过的电流量时,可于漏极(d)13处连接外部回路进行测量,但此为一般测量存储单元的晶体

管1电流流过的方式,故不赘述其详细测量方式内容。

33.因此,以上所述仅为本发明的优选实施例而已,非因此局限本发明的专利范围,本发明防止存储器数据遗失的方法,利用存储单元的晶体管1 于半导体基底11上成型源极(s)12、漏极(d)13,再于源极(s)12、漏极(d)13之间的通道14处依序堆叠成型第一隧穿氧化层(to)2、浮置栅极(fg)3、第二隧穿氧化层(to)4及控制栅极(cg)5等,通过写入微弱电场,以注入少量电子于浮置栅极3内,且供少量电子与二侧隧穿氧化层2、4内的电子形成相斥,而不致阻止源极12、漏极13之间的通道导通,即供读取显示状态“0”;再采用正常写入电场对浮置栅极3注入电子,进而阻止源极12、漏极13之间的通道导通,读取显示状态“1”,并可将电子信息或数据等写入浮置栅极3,俾可达到浮置栅极3内部数据不会遗失的目的,且写入数据时读取晶体管的浮置栅极3状态“0”或“1”不易错误的效果,而可有效防止存储单元的数据不遗失的功能,故举凡可达成前述效果的结构、装置皆应受本发明所涵盖,此种简易修饰及等效结构变化,均应同理包含于本发明的专利范围内,合予陈明。

34.故,本发明为主要针对防止存储器数据遗失的方法进行设计,利用存储单元的晶体管于半导体基底上成型源极、漏极,再于源极与漏极之间的通道上依序堆叠成型第一隧穿氧化层、浮置栅极、第二隧穿氧化层及控制栅极,并对浮置栅极写入微弱电场孺入少许电子,并与二侧隧穿氧化层内部电子相斥,不致阻止源极、漏极之间的通道导通,而显示状态“0”,再采用正常写入电场对浮置栅极注入电子,且阻止源极、漏极之间的通道导通,即显示状态“1”,以将电子信息或数据写入浮置栅极,并可达到防止浮置栅极内部存储数据遗失为主要保护重点,且可有效控制源极、漏极之间的通道导通与否,乃仅使对存储单元的晶体管写入数据时读取不易发生错误现象的优势,并可正常保存存储单元的浮置栅极内部数据的效果,只是,以上所述仅为本发明的优选实施例而已,非因此即局限本发明的专利范围,故举凡运用本发明说明书及附图内容所为的简易修饰及等效结构变化,均应同理包含于本发明的专利范围内,合予陈明。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1