用于执行编程操作的方法及相关的存储器件与流程

1.本发明涉及一种用于执行编程操作的方法,具体地涉及一种用于对三维(3d)nand存储器件执行编程操作的方法。

背景技术:

2.半导体存储器被广泛用于各种电子设备,诸如蜂窝电话、数码相机、个人数字助理、医疗电子设备、移动计算设备和非移动计算设备。非易失性存储器允许信息被存储和保留。非易失性存储器的示例包括闪存(例如,nand型和nor型闪存)和电可擦除可编程只读存储器(电可擦除可编程只读存储器eeprom)。

3.在一些nand架构中的存储单元具有充电存储区域(charging storage region),该充电存储区域保持充电以对存储单元进行编程。充电存储区域的一个示例是浮动栅极。当对诸如nand闪存器件之类的eeprom或闪存器件进行编程时,通常编程电压被施加至控制栅极(或被选择的字线),并且位线被接地。来自沟道的电子被注入到充电存储区域中。当电子在充电存储区域中累积时,充电存储区域变为带负电,并且存储单元的阈值电压升高,使得存储单元处于编程状态。

4.申请人注意到,在预充电阶段,残留的电子可能被捕获在未被选择的串的虚拟单元的存储区域中,从而造成对与未被选择的串相邻的被选择的串的被选择的存储单元的编程干扰。例如,在升压/编程阶段期间,在未被选择的串中捕获的残留的电子可能降低与被选择的串的被选择的存储单元对应的沟道电势,从而造成编程干扰。

5.因此,需要提供一种用以减少程序干扰的方法和存储器件。

技术实现要素:

6.因此,本发明的目的是提供一种用以减少程序干扰的方法和相关的存储器件。

7.本发明公开了一种用于对三维(3d)nand存储器件执行编程操作的方法。所述方法包括:在所述编程操作的预充电阶段期间,将第一电压施加到所述3d nand存储器件的多条第一字线,其中,所述多条第一字线垂直地位于被选择的字线下方以及多条虚拟字线上方;在所述预充电阶段期间,将第二电压施加到所述3d nand存储器件的第二相邻字线,其中,所述第二相邻字线垂直地位于所述多条第一字线和所述被选择的字线上方;以及在所述编程操作的升压阶段期间,将所述第二电压施加到所述第二相邻字线和所述多条第一字线,并将第三电压施加到所述3d nand存储器件的第一相邻字线,其中,所述第一相邻字线垂直地位于所述第二相邻字线下方以及所述被选择的字线、所述多条第一字线和所述多条虚拟字线上方。

8.本发明还公开了一种三维(3d)nand存储器件,所述三维(3d)nand存储器件包括:多条位线;多条字线;存储阵列,其包括多个串;字线驱动器,其耦接至所述存储阵列,并被配置为根据多个控制信号来产生施加到所述存储阵列的所述多条字线的多个电压;以及控制电路,其被配置为根据用于执行编程操作的过程来产生所述多个控制信号,其中,所述过

程包括如上所述的所述用于对三维(3d)nand存储器件执行编程操作的方法的步骤。

9.在阅读了以下在各个附图和图示中示出的优选实施例的具体实施方式之后,本发明的这些和其它目的无疑对于本领域普通技术人员将变得显而易见。

附图说明

10.图1示出了在与被选择的串相邻的未被选择的串的沟道中余下的残留的电子。

11.图2是针对图1中的串的编程操作的信号图。

12.图3示出了根据本发明的实施例,在与被选择的串相邻的未被选择的串的沟道中余下的残留的电子的运动。

13.图4是针对图3中的串的编程操作的信号图。

14.图5是根据本发明的实施例的存储器件的功能框图。

15.图6是根据本发明的实施例,针对图3中的串的编程操作的过程的流程图。

具体实施方式

16.图1示出了在与被选择的串10相邻的未被选择的串12的沟道中余下的残留的电子。存储阵列可以包括被选择的串10和未被选择的串12。存储阵列可以是包括多条位线、多条字线和多个串的三维nand闪存阵列,其中,所述串中的每个串垂直地延伸,并包括在多个水平层中形成的多个存储单元。

17.串10和12在结构上相同;例如,串10和12中的每一个可以包括顶部选择单元、多个顶部虚拟单元、多个顶部存储单元、多个中间虚拟单元、多个底部存储单元、多个底部虚拟单元和底部选择单元,其中,在串中包括的单元是串联地连接的。多个顶部虚拟单元包括i个单元,多个顶部存储单元包括j个单元,多个中间虚拟单元包括k个单元,多个底部存储单元包括m个单元,并且多个底部虚拟单元包括n个单元,其中,i、j、k、m和n是大于1的整数。

18.字线wl_tsg连接到串10和12的顶部选择单元的栅极。多条字线wl_td_1至wl_td_i连接到多个顶部虚拟单元的多个栅极。多条字线wl_1至wl_j连接到串10和12的多个顶部存储单元的多个栅极。多条字线wl_1至wl_j之一是被选择的字线wl_x,其连接到被选择的串10的被选择的存储单元和与被选择的存储单元水平相邻的存储单元。多条字线wl_1至wl_j之一是连接至第一相邻存储单元的第一相邻字线wl_x+1,该第一相邻存储单元垂直地相邻于被选择的串10的被选择的存储单元。多条字线wl_1至wl_j之一是连接至第二相邻存储单元的第二相邻字线wl_x+2,该第二相邻存储单元垂直地相邻于被选择的串10的第一相邻存储单元。

19.多条字线wl_md_1至wl_md_k连接到串10和12的多个中间虚拟单元的多个栅极。多条字线wl_b_1至wl_b_m连接到串10和12的多个底部虚拟单元的多个栅极。多条字线wl_bd_1至wl_bd_n连接到串10和12的多个底部虚拟单元的多个栅极。字线wl_bsg连接到串10和12的底部选择单元的栅极。

20.顶部选择单元的漏极连接到位线(bl),并且在编程操作期间,被选择的串10的位线始终被施加零(地)电压,而在编程操作期间,未被选择的串12被施加系统电压脉冲vcc。在编程操作的预充电阶段期间,一定量的残留的电子可能在与未被选择的串12的多条字线wl_md_1至wl_md_k对应的多个中间虚拟单元的存储区域中被俘获,从而造成对相邻的被选

择的串10的编程干扰。

21.图2是针对图1中的串10和12的编程操作的信号图。在预充电阶段期间,被选择的串12的位线的电压从时间t0处的零伏增大到时间t4处的电压vcc。字线wl_tsg的电压从时间t0处的零伏增大到时间t1处的电压vtsg,并且字线wl_tsg的电压从时间t3减小到时间t4处的零伏。在预充电阶段,字线wl_bsg、wl_bd_1至wl_bd_n、wl_b_1至wl_b_m、wl_md_1至wl_md_k、wl_1至wl_j以及wl_td_1至wl_td_i处于零伏。多条字线wl_1至wl_j之一是被选择的字线wl_x。

22.在时间t1至时间t2期间,一定数量的残留的电子可能在与未被选择的串12的多条字线wl_md_1至wl_md_k对应的多个中间虚拟单元的存储区域中被俘获,从而造成对相邻的被选择的串10的编程干扰。例如,在未被选择的串12的升压阶段以及被选择的串10的编程阶段期间,特别是从时间t9到时间t10,电压vpass被施加到与存储单元对应的字线wl_b_1至wl_b_m和wl_1至wl_j以增大存储单元的沟道电势,并且电压vbias被施加到与虚拟单元对应的字线wl_bd_1至wl_bd_n、wl_md_1至wl_md_k以及wl_td_1至wl_td_i以增大虚拟单元的沟道电势。在时间t10到时间t11期间,编程电压vpgm被施加到被选择的字线wl_x。然而,未被选择的串12的中间虚拟单元处的残留的电子可以感生出对相邻的被选择的串10的横向场,从而造成编程干扰。例如,由于被残留的电子感生出的横向场,与被选择的串10的被选择的存储单元对应的沟道电势减小。

23.为了减少编程干扰,参照图3,图3示出了根据本发明的实施例的在未被选择的串12的沟道中余下的残留的电子的运动,该未被选择的串12与被选择的串10相邻。为了减少残留的电子以避免编程干扰,在预充电阶段期间,向与全部多个顶部存储单元对应的全部字线wl_1至wl_j施加电压von以部分地导通未被选择的串12的沟道,从而残留的电子可以沿着部分地导通的沟道从中间虚拟单元向多个顶部存储单元移动。此外,在预充电阶段期间,在字线wl_1至wl_x+1以及wl_x+3至wl_j被施加零伏以部分地截止未被选择的串12的沟道之后,字线wl_x+2被施加电压vpass以部分地导通被选择的串12的沟道,从而残留的电子可以沿着部分地导通的沟道从顶部存储单元向顶部虚拟单元移动。最后,在升压/编程阶段期间,向字线wl_x+1施加电压vcut,以弱截止与字线wl_x+1对应的顶部存储单元,从而未被选择的串12的沟道被部分地截止,以防止残留的电子移回到在与字线wl_x+1对应的顶部存储单元下方的顶部存储单元。结果,可以从多个中间虚拟单元中移除残留的电子,以避免编程干扰。

24.图4是图3中的针对串10和12的编程操作的信号图。详细地,预充电阶段在时间t0处开始,并在时间t7处结束。未被选择的串12的位线的电压从时间t0处的零伏增大到时间t1处的电压vcc,电压vcc从时间t1到时间t6被施加到未被选择的串12的位线,并且未被选择的串12的位线的电压从时间t6处的电压vcc减小到时间t7处的零伏。在编程操作期间,被选择的串10的位线总是被施加零伏。字线wl_tsg的电压从时间t0处的零伏增大到时间t1处的电压vtsg,电压vtsg从时间t1到时间t5被施加到字线wl_tsg,并且字线wl_tsg的电压在预充电阶段即将结束时从时间t5处的电压vtsg减小为时间t6处的零伏。在编程操作期间,字线wl_x+2、wl_x+1、wl_x、wl_b_1至wl_b_m、wl_td_1至wl_td_i、wl_md_1至wl_md_k以及wl_bd_1至wl_bd_n的电压始终被施加零伏。

25.从时间tl到时间t2,电压von被施加到字线wl_1至wl_j,以部分地导通多个顶部存

储单元处的沟道。因此,在未被选择的串12的多个中间虚拟单元的存储区域处捕获的残留的电子在被通过电压von提供的电压电势吸引时,能够向与字线wl_1至wl_j对应的顶部存储单元移动。从时间t2到时间t3,字线wl_1至wl_j的电压从电压von减小至零伏,以截止与字线wl_1至wl_j对应的多个顶部存储单元处的未被选择的串12的沟道。注意,被配置为控制存储阵列的控制电路的电路面积取决于编程操作的复杂度;例如,控制电路需要较大的面积来执行较复杂的编程操作。通过在预充电阶段期间向与全部多个顶部存储单元对应的全部字线wl_1至wl_j施加电压von,与图2中的编程操作的复杂度相比,编程操作的复杂度是可接受的。

26.与第二相邻存储单元对应的字线wl_x+2的电压从时间t4处的零伏增大到时间t5处的电压vpass,以部分地导通未被选择的串12的第二相邻存储单元处的沟道。因此,与字线wl_1至wl_x-1对应的顶部存储单元处的残留的电子在被通过电压vpass提供的电压电势吸引时,可以移动至与字线wl_x+2对应的第二相邻存储单元。注意,从预充电阶段处的时间t5到升压阶段处的时间t11,电压vpass被施加到字线wl_x+2;从另一角度来看,对应于字线wl_x+2的第二相邻存储单元在多条字线wl_1至wl_x+1以及wl_x+3至wl_j的其余部分之前被导通,以在进入升压/编程阶段之前,提升与字线wl_x+2对应的沟道电势。

27.注意,图2中的预充电阶段在时间t0处开始并在时间t4处结束,而图4中的预充电阶段开始于时间t0并结束于时间t7。本发明的预充电阶段被扩展以允许残留的电子在预充电阶段期间从位线放电。

28.预充电阶段在时间t7处结束,未被选择的串12的升压阶段和被选择的串10的编程阶段在时间t7处开始并在时间t12处结束。

29.详细地,与第一相邻存储单元对应的字线wl_x+1的电压从时间t7处的零伏增大到时间t8处的电压vcut,电压vcut从时间t8至t11被施加到字线wl_x+1,字线wl_x+1的电压从时间t11处的电压vcut减小到时间t12处的零伏。字线wl_1至wl_x-1、wl_x、wl_b_1至wl_b_m的电压从时间t7处的零伏增大到时间t8处的电压vpass,电压vpass从时间t8到时间t11被施加至字线wl_1至wl_x-1、wl_x、wl_b_1至wl_b_m,以及字线wl_1至wl_x-1、wl_x、wl_b_1至wl_b_m的电压从时间t11处的电压vcut减小到时间t12处的零伏。字线wl_td_1至wl_td_i、wl_md_1至wl_md_k和wl_bd_1至wl_bd_n的电压从时间t7处的零伏增加至时间t8处的电压vbias,电压vbias从时间t8到时间t11被施加至字线wl_td_1至wl_td_i、wl_md_1至wl_md_k、和wl_bd_1至wl_bd_n,以及字线wl_td_1到wl_td_i、wl_md_1到wl_md_k以及wl_bd_1到wl_bd_n的电压从时间t11处的电压vcut减小到时间t12处的零伏。

30.在未被选择的串12的升压阶段期间,对应于第二相邻存储单元的字线wl_x+2被施加电压vpass(t8至t11),对应于第一相邻存储单元的字线wl_x+1被施加电压vcut(t8至t11),并与被选择的存储单元对应的字线wl_x被施加电压vpass(t8至t9)和电压vpgm(t10至t11),其中,电压vcut为小于电压vpass和vpgm。因此,第一相邻存储单元被电压vcut弱截止,从而未被选择的串12的沟道被第一相邻存储单元切断(cut),并且位于第一相邻存储单元上方的存储单元与在第一相邻存储单元下方的存储单元隔离。结果,残留的电子可以通过未被选择的串12的位线和被弱截止的第一相邻存储单元被放电,以防止残留的电子被由电压vpass或vpgm提供的电压电势吸引。

31.在未被选择的串12的升压阶段(t8至t11)期间,通过将电压vpass施加到与存储单

元对应的字线并且将电压vbias施加到与虚拟单元对应的字线来提升未被选择的串12的沟道电势,这防止了与被选择的字线wl_x对应的未被选择的串12的存储单元被电压vpgm无意地编程。

32.在被选择的串10的编程阶段期间,通过从时间t8到时间t9施加电压vpass来提升与被选择的存储单元对应的沟道电势。电压vpgm被施加到与被选择的串10的被选择的存储单元对应的被选择的字线wl_x,以执行从时间t10到时间t11的编程操作。

33.最后,升压阶段和编程阶段将从时间t11结束,并且当升压阶段和编程阶段结束时,全部位线和全部字线都在时间t12处减小至零伏。

34.结果,可以在预充电阶段期间将残留的电子从未被选择的串12移除,以减少在升压/编程阶段期间对相邻的被选择的串10的编程干扰。此外,通过将电压von施加到与全部多个顶部存储单元对应的全部字线wl_1至wl_j以导通多个顶部存储单元,与图2中的编程操作的复杂度相比,编程操作的复杂度是可接受的。

35.图5是根据本发明实施例的存储器件5的功能框图。存储器件5包括存储阵列50、字线驱动器52和控制电路54。存储器件5可以是三维nand闪存设备。存储阵列5包括多条位线(bl)、多条字线和多个串(例如,图3中的串10和12)。每个串包括多个存储单元和多个虚拟单元,其中,多个存储单元和多个虚拟单元被串联地连接并在衬底(未示出)上方垂直地延伸。控制电路54被配置为产生多个控制信号给字线驱动器52以执行编程操作。字线驱动器52耦合到控制电路54和存储阵列50,并被配置为根据由控制电路54产生的多个控制信号来产生施加到存储阵列50的多条字线的多个电压。

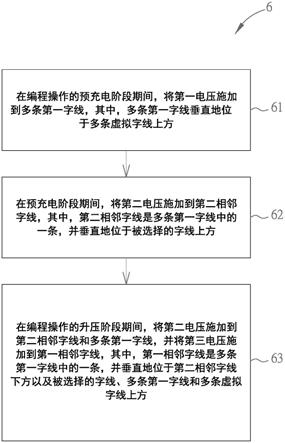

36.图6是根据本发明的实施例,针对图3中的串的编程操作的过程6的流程图。过程6可以由控制电路54执行,并且包括以下步骤。

37.步骤61:在编程操作的预充电阶段期间,将第一电压施加到多条第一字线,其中,多条第一字线垂直地位于多条虚拟字线上方。

38.步骤62:在预充电阶段期间,将第二电压施加到第二相邻字线,其中,第二相邻字线是多条第一字线中的一条,并垂直地位于被选择的字线上方。

39.步骤63:在编程操作的升压阶段期间,将第二电压施加到第二相邻字线和多条第一字线,并将第三电压施加到第一相邻字线,其中,第一相邻字线是多条第一字线中的一条,并垂直地位于第二相邻字线下方以及被选择的字线、多条第一字线和多条虚拟字线上方。

40.在步骤61中,在编程操作的预充电阶段期间,控制电路54被配置为将第一电压(例如,von)施加到多条第一字线(例如,wl_1至wl_j),其中,多条第一字线(例如,wl_1至wl_1)垂直地位于多条虚拟字线(例如,wl_md_1至wl_md_k)上方。因此,在多个中间虚拟单元的存储区域中捕获的残留的电子可以向上移动至与字线wl_1至wl_j对应的顶部存储单元。

41.在步骤62中,在预充电阶段期间,控制电路54被配置为将第二电压(例如,vpass)施加到第二相邻字线(例如,wl_x+2),其中,第二相邻字线(例如,wl_x+2)是多条第一字线(例如,wl_1至wl_j)中的一条,并且垂直地位于被选择的字线(例如,wl_x)上方。

42.在步骤63中,在编程操作的升压阶段期间,控制电路54被配置为将第二电压(例如,vpass)施加到第二相邻字线(例如,wl_x+2)和多条第一字线,并将第三电压(例如,vcut)施加到第一相邻字线(例如,wl_x+1),其中,第一相邻字线(例如,wl_x+1)垂直地位于

第二相邻字线(例如,wl_x+2)下方以及被选择的字线(例如,wl_x)、多条第一字线(例如,wl_1至wl_x-1)和多条虚拟字线(例如,wl_md_1至wl_md_k)上方。因此,由于第三电压vcut小于第二电压vpass,因此未被选择的串12的沟道被部分地截止,以防止残留的电子移回到与字线wl_x+1对应的顶部存储单元下方的顶部存储单元。结果,可以从未被选择的串12移除残留的电子,以减少对相邻的被选择的串10的编程干扰。

43.总而言之,本发明提供了一种编程操作的方法,以移除在预充电阶段期间在未被选择的串的中间虚拟存储单元的存储区域中捕获的残留的电子,以便减少对与未被选择的串相邻的被选择的串的编程干扰。此外,通过在预充电阶段期间将电压von施加到与全部多个顶部存储单元对应的全部字线wl_1至wl_j,与图2中的编程操作的复杂度相比,编程操作的复杂度是可接受的。

44.本领域技术人员将容易地观察到,在保持本发明的教导的同时,可以对器件和方法进行多种修改和变更。因此,以上的公开内容应被解释为仅由所附权利要求书的界限来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1