半导体器件以及使用该半导体器件的刷新方法与流程

半导体器件以及使用该半导体器件的刷新方法

1.相关申请的交叉引用

2.本技术要求于2020年4月24日提交的申请号为10-2020-0050394的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开的实施例涉及对目标地址执行智能刷新操作的半导体器件以及使用该智能刷新操作的刷新方法。

背景技术:

4.诸如动态随机存取存储(dram)器件的每个半导体器件可以包括多个单元阵列,并且多个单元阵列中的每一个可以包括用于储存数据的多个存储单元。多个存储单元中的每一个可以被设计为包括单元电容器和单元晶体管。dram器件可以通过对单元电容器放电或充电来将数据储存在其中。一旦对单元电容器进行充电或放电以在将数据储存在其中,则即使经过了一段时间,储存在单元电容器中的电荷量也必须理想地恒定。然而,由于在单元电容器和与单元电容器相邻的电路之间的电压电平差或者由于单元电容器的泄漏电流,因此储存在单元电容器中的电荷量实际上可能变化。具体地,如果储存在单元电容器中的电荷量减少了,则单元电容器可能会丢失储存在其中的数据,从而导致dram器件发生故障。因此,dram器件可能需要刷新操作来防止存储单元丢失其数据。

5.由于半导体器件随着处理技术的发展变得更加高度集成,因此存储单元之间的距离以及连接到存储单元的字线之间的距离在不断减小。如果字线之间的距离被减小,则储存在相邻存储单元中的数据由于字线之间的耦接现象或干扰现象而被改变。

技术实现要素:

6.根据一个实施例,一种半导体器件可以包括外围电路和核心电路。外围电路可以被配置为:进入基于命令而执行智能刷新操作的智能刷新模式,并且可以被配置为:在智能刷新模式下从目标地址信号产生锁存地址信号,以通过全局输入/输出(i/o)线来输出锁存地址信号。核心电路可以被配置为:对锁存地址信号执行加法运算和减法运算以产生第一内部地址信号和第二内部地址信号,并可以被配置为:基于第一内部地址信号和第二内部地址信号来对第一存储体和第二存储体执行智能刷新操作。

7.根据另一实施例,一种半导体器件可以包括地址输入电路、内部地址发生电路和核心电路。该地址输入电路可以被配置为在智能刷新操作期间从目标地址信号产生锁存地址信号,以通过全局输入/输出(i/o)线来输出锁存地址信号。内部地址发生电路可以被配置为:通过基于第一存储体激活地址信号和第二存储体激活地址信号以及第一存储体刷新地址信号和第二存储体刷新地址信号而执行锁存地址信号的加法运算和减法运算来产生第一内部地址信号和第二内部地址信号。内部地址发生电路可以被配置为通过局部i/o线来输出第一内部地址信号和第二内部地址信号。核心电路可以包括第一存储体和第二存储

体。核心电路可以被配置为基于第一内部地址信号来对第一存储体执行智能刷新操作。核心电路可以被配置为基于第二内部地址信号来对第二存储体执行智能刷新操作。

8.根据又一实施例,可以提供一种刷新方法。刷新方法可以包括:在智能刷新操作期间,从地址信号产生存储体激活地址信号和存储体刷新地址信号;在智能刷新操作期间,从目标地址信号产生锁存地址信号;以及通过根据锁存地址信号的特定比特位信号的逻辑电平而执行加法运算和减法运算来产生内部地址信号,以对根据存储体激活地址信号和存储体刷新地址信号而被激活的存储体执行智能刷新操作。

附图说明

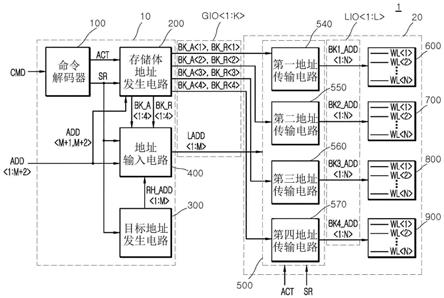

9.图1是示出根据本公开的实施例的半导体器件的配置的框图。

10.图2是示出图1所示的半导体器件中包括的存储体地址发生电路的配置的框图。

11.图3是示出图2所示的存储体地址发生电路中包括的存储体激活地址发生电路的配置的电路图。

12.图4是示出图2所示的存储体地址发生电路中包括的存储体刷新地址发生电路的配置的电路图。

13.图5示出了图1所示的半导体器件中包括的地址输入电路的配置。

14.图6是示出图1所示的半导体器件中包括的内部地址发生电路的配置的框图。

15.图7是示出图6所示的内部地址发生电路中包括的脉冲发生电路的配置的电路图。

16.图8是示出图6所示的内部地址发生电路中所包括的控制信号发生电路的配置的电路图。

17.图9和图10是示出图6所示的内部地址发生电路中包括的第一地址传输电路的配置的电路图。

18.图11和图12是示出根据本公开的实施例的半导体器件的操作的时序图。

19.图13是示出根据本公开的实施例的智能刷新方法的流程图。

20.图14是示出包括图1至图12所示的半导体器件的电子系统的结构的框图。

具体实施方式

21.在下文中将参考附图描述本公开的各种实施例。然而,本文中所描述的实施例仅用于说明性目的,并不旨在限制本公开的范围。

22.如上所述,如果字线之间的距离被减小,则由于字线之间的耦接现象或干扰现象,可能改变储存在相邻存储单元中的数据。这样,已经将与附加刷新操作相对应的智能刷新操作应用于与被频繁访问或激活的目标字线相邻的字线,以便防止连接至与目标字线相邻的字线的存储单元由于字线之间的干扰现象而丢失其数据。用于访问与目标字线相邻的两条字线的地址的加法运算和减法运算必须被运行以执行智能刷新操作,并且通过加法运算和减法运算产生的地址可以通过全局输入/输出(i/o)线被顺序地输出至核心电路,以执行智能刷新操作。

23.如图1中所示,根据实施例的半导体器件1可以包括外围电路10和核心电路20。

24.外围电路10可以包括命令解码器100、存储体地址发生电路200、目标地址发生电路300和地址输入电路400。

25.命令解码器100可以对命令cmd进行解码以产生激活信号act和刷新信号sr。命令解码器100可以对命令cmd进行解码以产生被使能以进入智能刷新操作的激活信号act。命令解码器100可以对命令cmd进行解码以产生包括第一脉冲和第二脉冲的刷新信号sr,所述第一脉冲和第二脉冲在智能刷新操作期间被顺序地创建。命令解码器100可以对命令cmd进行解码以产生被使能以进入正常操作的激活信号act。命令解码器100可以对命令cmd进行解码以产生在正常操作期间被禁止的刷新信号sr。尽管在图1中用一个信号线示出了命令cmd,但是命令cmd可以被设置为包括多个比特位的信号。

26.当激活信号act和刷新信号sr被输入到存储体地址发生电路200时,存储体地址发生电路200可以接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>,以产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>以及第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>。当激活信号act被使能时,存储体地址发生电路200可以产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>,所述第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>中的一个根据第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平而被选择性地使能。当刷新信号sr被使能时,存储体地址发生电路200可以产生第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>,所述第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>中的一个根据第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平而被选择性地使能。第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>可以对应于用于选择包括在核心电路20中的第一存储体至第四存储体600、700、800和900中的一个的比特位信号。在一个实施例中,

‘

m’是可以具有可变值的整数。也许m是大于1的整数。

27.当刷新信号sr被输入时,目标地址发生电路300可以产生第一目标地址信号至第m目标地址信号rh_add<1:m>。目标地址发生电路300可以使用寄存器来实现,并且当刷新信号sr被输入时,目标地址发生电路300可以输出储存在其中的第一目标地址信号至第m目标地址信号rh_add<1:m>。第一目标地址信号至第m目标地址信号rh_add<1:m>可以包括关于第一存储体至第四存储体600、700、800和900中所包括的所有字线之中的、被激活至少预定次数的字线的位置的信息。预定次数可以被设置为目标字线被激活直到连接至与该目标字线相邻的字线的存储单元的数据被丢失为止的次数。预定次数可以根据实施例而被设置为不同。如果字线之间的距离被减小,则预定次数也可以减小。如本文所使用的关于参数的词“预定”(诸如预定次数)指在过程或算法中使用该参数之前确定该参数的值。对于一些实施例,在过程或算法开始之前确定参数的值。在其他实施例中,在过程或算法期间但在过程或算法中使用参数之前确定参数的值。

28.当第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>被输入至地址输入电路400时,地址输入电路400可以从第一地址信号至第m地址信号add<1:m>产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。当刷新信号sr和第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>被输入至地址输入电路400时,地址输入电路400可以从第一目标地址信号到第m目标地址信号rh_add<1:m>产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。

29.第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址

信号ladd<1:m>可以通过第一全局i/o线至第k全局i/o线gio<1:k>从外围电路10传输到核心电路20。第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>可以通过第一全局i/o线至第四全局i/o线gio<1:4>传输至核心电路20。第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>可以通过第五全局i/o线至第八全局i/o线gio<5:8>传输至核心电路20。第一锁存地址信号至第m锁存地址信号ladd<1:m>可以通过第九全局i/o线至第k全局i/o线gio<9:k>传输至核心电路20。第一全局i/o线至第k全局i/o线gio<1:k>的数目“k”可以被设置为等于第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>的总数。例如,当第一锁存地址信号至第m锁存地址信号ladd<1:m>的数目“m”被设置为“8”时,第一全局i/o线至第k全局i/o线gio<1:k>的数目“k”可以被设置为“16”。

30.外围电路10可以被设计为包括用于控制半导体器件1的核心电路20的操作的控制电路。外围电路10可以通过第一全局i/o线至第k全局i/o线gio<1:k>来输出用于控制核心电路20的操作的各种信号。

31.具有前述配置的外围电路10可以进入智能刷新模式,在该智能刷新模式中由命令cmd来执行智能刷新操作,并且该外围电路10可以在智能刷新操作期间从第一地址信号至第(m+2)地址信号add<1:(m+2)>以及第一目标地址信号至第m目标地址信号rh_add<1:m>来产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>。外围电路10可以通过第一全局i/o线至第k全局i/o线gio<1:k>将第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>输出至核心电路20。

32.核心电路20可以包括内部地址发生电路500、第一存储体600、第二存储体700、第三存储体800和第四存储体900。

33.内部地址发生电路500可以包括第一地址传输电路540、第二地址传输电路550、第三地址传输电路560和第四地址传输电路570。

34.当激活信号act和刷新信号sr被输入至内部地址发生电路500时,内部地址发生电路500可以从第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>来产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>。在智能刷新操作期间,内部地址发生电路500可以通过基于激活信号act和刷新信号sr来顺序地执行第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>的加法运算和减法运算来产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>。在执行正常操作的情况下,内部地址发生电路500可以从第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>来产生第一内部地址信

号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>。

35.第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>可以通过第一局部i/o线至第l局部i/o线lio<1:l>输出至第一存储体600至第四存储体900。第一内部地址信号bk1_add<1:n>可以通过第一局部i/o线至第n局部i/o线lio<1:n>输出到第一存储体600。第二内部地址信号bk2_add<1:n>可以通过第(n+1)局部i/o线至第2n局部i/o线lio<(n+1):2n>输出到第二存储体700。第三内部地址信号bk3_add<1:n>可以通过第(2n+1)局部i/o线至第3n局部i/o线lio<(2n+1):3n>输出到第三存储体800。第四内部地址信号bk4_add<1:n>可以通过第(3n+1)局部i/o线至第l局部i/o线lio<(3n+1):l>输出到第四存储体900。第一局部i/o线至第l局部i/o线lio<1:l>的数目“l”可以被设置为等于第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>的总数。例如,当第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>中的每一个的数目“n”被设置为为“8”时,第一局部i/o线至第l局部i/o线lio<1:l>的数目“l”可以设置为“32”。

36.稍后将在下面参考图6描述第一地址传输电路540、第二地址传输电路550、第三地址传输电路560和第四地址传输电路570的配置和操作。

37.第一存储体600可以包括第一字线至第n字线wl<1:n>。包括在第一存储体600中的第一字线至第n字线wl<1:n>可以通过第一内部地址信号bk1_add<1:n>而被激活。第一存储体600可以通过基于第一内部地址信号bk1_add<1:n>而激活第一字线至第n字线wl<1:n>来执行智能刷新操作。第一字线至第n字线wl<1:n>的数目“n”可以被设置为等于第一内部地址信号bk1_add<1:n>中包括的比特位的数目“n”。

38.第二存储体700也可以包括第一字线至第n字线wl<1:n>。包括在第二存储体700中的第一字线至第n字线wl<1:n>可以通过第二内部地址信号bk2_add<1:n>而被激活。第二存储体700可以通过基于第二内部地址信号bk2_add<1:n>而激活第一字线至第n字线wl<1:n>来执行智能刷新操作。第一字线至第n字线wl<1:n>的数目“n”可以被设置为等于第二内部地址信号bk2_add<1:n>中包括的比特位的数目“n”。

39.第三存储体800也可以包括第一字线至第n字线wl<1:n>。包括在第三存储体800中的第一字线至第n字线wl<1:n>可以通过第三内部地址信号bk3_add<1:n>而被激活。第三存储体800可以通过基于第三内部地址信号bk3_add<1:n>而激活第一字线至第n字线wl<1:n>来执行智能刷新操作。第一字线至第n字线wl<1:n>的数目“n”可以被设置为等于第三内部地址信号bk3_add<1:n>中包括的比特位的数目“n”。

40.第四存储体900也可以包括第一字线至第n字线wl<1:n>。包括在第四存储体900中的第一字线至第n字线wl<1:n>可以通过第四内部地址信号bk4_add<1:n>而被激活。第四存储体900可以通过基于第四内部地址信号bk4_add<1:n>而激活第一字线至第n字线wl<1:n>来执行智能刷新操作。第一字线至第n字线wl<1:n>的数目“n”可以被设置为等于第四内部地址信号bk4_add<1:n>中包括的比特位的数目“n”。

41.可以使用包括具有多个存储单元的存储体的通用存储电路来实现核心电路20。

42.在智能刷新操作期间,具有前述配置的核心电路20可以通过对第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>以及第一锁存地址信号至第m锁存地址信号ladd<1:m>依次执行加法

运算和减法运算来产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>。核心电路20可以基于第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>来执行用于激活与由目标地址选择的目标字线相邻的两个字线的智能刷新操作,所述第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>是在智能刷新模式下通过加法运算和减法运算产生的。在正常操作期间,核心电路20可以从第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>、第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>、以及第一锁存地址信号至第m锁存地址信号ladd<1:m>产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>。

43.参考图2,存储体地址发生电路200可以包括存储体激活地址发生电路210和存储体刷新地址发生电路220。

44.当激活信号act被输入时,存储体激活地址发生电路210可以接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>以产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>。当激活信号act被输入时,存储体激活地址发生电路210可以产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>,第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>中的一个根据第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平而被选择性地使能。稍后将参考图3来描述用于产生第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>的第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平。

45.当刷新信号sr被输入时,存储体刷新地址发生电路220可以接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>以产生第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>。当刷新信号sr被输入时,存储体刷新地址发生电路220可以产生第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>,所述第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>中的一个根据第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平而被选择性地使能。稍后将参考图4来描述用于产生第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>的第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>的逻辑电平。

46.参考图3,存储体激活地址发生电路210可以包括第一存储体激活地址发生电路211、第二存储体激活地址发生电路212、第三存储体激活地址发生电路213和第四存储体激活地址发生电路214。

47.第一存储体激活地址发生电路211可以使用反相器iv11、iv12和iv13以及与非门nand11来实现。当激活信号act被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“低”电平以及第(m+2)地址信号add<m+2>具有逻辑“低”电平时,第一存储体激活地址发生电路211可以产生具有逻辑“高”电平的第一存储体激活地址信号bk_a<1>。

48.第二存储体激活地址发生电路212可以使用反相器iv14和iv15以及与非门nand12来实现。当激活信号act被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“高”电平以及第(m+2)地址信号add<m+2>具有逻辑“低”电平时,第二存储体激活地址发生电路212可以产生具有逻辑“高”电平的第二存储体激活地址信号bk_a<2>。

49.第三存储体激活地址发生电路213可以使用反相器iv16和iv17以及与非门nand13来实现。当激活信号act被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“低”电平以及第(m+2)地址信号add<m+2>具有逻辑“高”电平时,第三存储体激活地址发生电路213可以产生具有逻辑“高”电平的第三存储体激活地址信号bk_a<3>。

50.第四存储体激活地址发生电路214可以使用反相器iv18和与非门nand14来实现。当激活信号act被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“高”电平以及第(m+2)地址信号add<m+2>具有逻辑“高”电平时,第四存储体激活地址发生电路214可以产生具有逻辑“高”电平的第四存储体激活地址信号bk_a<4>。

51.参考图4,存储体刷新地址发生电路220可以包括第一存储体刷新地址发生电路221、第二存储体刷新地址发生电路222、第三存储体刷新地址发生电路223和第四存储体刷新地址发生电路224。

52.第一存储体刷新地址发生电路221可以使用反相器iv21、iv22和iv23以及与非门nand21来实现。当刷新信号sr被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“低”电平以及第(m+2)地址信号add<m+2>具有逻辑“低”电平时,第一存储体刷新地址发生电路221可以产生具有逻辑“高”电平的第一存储体刷新地址信号bk_r<1>。

53.第二存储体刷新地址发生电路222可以使用反相器iv24和iv25以及与非门nand22来实现。当刷新信号sr被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“高”电平以及第(m+2)地址信号add<m+2>具有逻辑“低”电平时,第二存储体刷新地址发生电路222可以产生具有逻辑“高”电平的第二存储体刷新地址信号bk_r<2>。

54.第三存储体刷新地址发生电路223可以使用反相器iv26和iv27以及与非门nand23来实现。当刷新信号sr被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“低”电平以及第(m+2)地址信号add<m+2>具有逻辑“高”电平时,第三存储体刷新地址发生电路223可以产生具有逻辑“高”电平的第三存储体刷新地址信号bk_r<3>。

55.第四存储体刷新地址发生电路224可以使用反相器iv28和与非门nand24来实现。当刷新信号sr被使能成具有逻辑“高”电平、第(m+1)地址信号add<m+1>具有逻辑“高”电平以及第(m+2)地址信号add<m+2>具有逻辑“高”电平时,第四存储体刷新地址发生电路224可以产生具有逻辑“高”电平的第四存储体刷新地址信号bk_r<4>。

56.参考图5,地址输入电路400可以包括第一输入电路410、第二输入电路420、第三输入电路430、第四输入电路440和锁存电路450。

57.当第一存储体激活地址信号bk_a<1>被输入时,第一输入电路410可以从第一地址信号至第m地址信号add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。当刷新信号sr和第一存储体刷新地址信号bk_r<1>被输入时,第一输入电路410可以从第一目标地址信号至第m目标地址信号rh_add<1:m>来产生第一输入地址信号至第m输入地址信号in_a<1:m>。

58.当第二存储体激活地址信号bk_a<2>被输入时,第二输入电路420可以从第一地址信号至第m地址信号add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。当刷新信号sr和第二存储体刷新地址信号bk_r<2>被输入时,第二输入电路420可以从第一目标地址信号至第m目标地址信号rh_add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。

59.当第三存储体激活地址信号bk_a<3>被输入时,第三输入电路430可以从第一地址信号至第m地址信号add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。当刷新信号sr和第三存储体刷新地址信号bk_r<3>被输入时,第三输入电路430可以从第一目标地址信号至第m目标地址信号rh_add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。

60.当第四存储体激活地址信号bk_a<4>被输入时,第四输入电路440可以从第一地址信号至第m地址信号add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。当刷新信号sr和第四存储体刷新地址信号bk_r<4>被输入时,第四输入电路440可以从第一目标地址信号至第m目标地址信号rh_add<1:m>产生第一输入地址信号至第m输入地址信号in_a<1:m>。

61.锁存电路450可以使用反相器iv33和iv34来实现。锁存电路450可以锁存第一输入地址信号至第m输入地址信号in_a<1:m>,并且可以对第一输入地址信号至第m输入地址信号in_a<1:m>的锁存信号进行反相缓冲以产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。

62.在下文中将更详细地描述第一输入电路410的配置和操作。

63.第一输入电路410可以使用反相器iv31和iv32、与门and31以及传输门t31和t32来实现。

64.当具有逻辑“高”电平的第一存储体激活地址信号bk_a<1>被输入到第一输入电路410时,第一输入电路410可以输出第一地址信号至第m地址信号作为第一输入地址信号至第m输入地址信号in_a<1:m>。

65.当具有逻辑“高”电平的刷新信号sr和具有逻辑“高”电平的第一存储体刷新地址信号bk_r<1>被输入到第一输入电路410时,第一输入电路410可以输出第一目标地址信号至第m目标地址信号rh_add<1:m>作为第一输入地址信号至第m输入地址信号in_a<1:m>。

66.另外,第二输入电路420至第四输入电路440中的每一个可以使用与第一输入电路410基本相同的电路(除了其输入/输出(i/o)信号之外)来实现。因此,在下文中将省略第二输入电路至第四输入电路420至440的详细描述。

67.参考图6,内部地址发生电路500可以包括脉冲发生电路510、控制信号发生电路520、地址解码器530、第一地址传输电路540、第二地址传输电路550、第三地址传输电路560和第四地址传输电路570。

68.当控制信号scon没有被输入时,脉冲发生电路510可以产生第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>,所述第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>包括从第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>或第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>产生的脉冲。当控制信号scon被输入时,脉冲发生电路510可以产生第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>,所述第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>不管第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>和第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>如何都被禁止。

69.控制信号发生电路520可以产生在输入复位信号rst时被禁止的控制信号scon。控制信号发生电路520可以产生由激活信号act和刷新信号sr使能的控制信号scon。控制信号

发生电路520可以产生控制信号scon,该控制信号scon在激活信号act被输入并且刷新信号sr的第一脉冲被禁止时被禁止。复位信号rst可以被设置为包括在半导体器件1的初始化操作期间产生的、具有逻辑“高”电平的脉冲的信号。

70.地址解码器530可以对第一锁存地址信号至第m锁存地址信号ladd<1:m>进行解码,以产生第一解码信号至第n解码信号dec<1:n>,它们中的一个被选择性地使能。地址解码器530可以使用接收“m”比特位信号以生成“n”比特位信号的通用解码器来实现。

71.当刷新信号sr被禁止时,第一地址传输电路540可以根据复位信号rst、第一命令脉冲信号cmdp<1>以及第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第一内部地址信号bk1_add<1:n>。当刷新信号sr被使能时,第一地址传输电路540可以基于控制信号scon、通过根据第一命令脉冲信号cmdp<1>和第一解码信号至第n解码信号dec<1:n>的逻辑电平而执行加法运算和减法运算来产生第一内部地址信号bk1_add<1:n>。第一地址传输电路540可以通过第一局部i/o线至第n局部i/o线lio<1:n>将第一内部地址信号bk1_add<1:n>输出到第一存储体600。

72.当刷新信号sr被禁止时,第二地址传输电路550可以根据复位信号rst、第二命令脉冲信号cmdp<2>以及第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第二内部地址信号bk2_add<1:n>。当刷新信号sr被使能时,第二地址传输电路550可以基于控制信号scon、通过根据第二命令脉冲信号cmdp<2>和第一解码信号至第n解码信号dec<1:n>的逻辑电平而执行加法运算和减法运算来产生第二内部地址信号bk2_add<1:n>。第二地址传输电路550可以通过第(n+1)局部i/o线至第2n局部i/o线lio<(n+1):2n>将第二内部地址信号bk2_add<1:n>输出到第二存储体700。

73.当刷新信号sr被禁止时,第三地址传输电路560可以根据复位信号rst、第三命令脉冲信号cmdp<3>以及第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第三内部地址信号bk3_add<1:n>。当刷新信号sr被使能时,第三地址传输电路560可以基于控制信号scon、通过根据第三命令脉冲信号cmdp<3>和第一解码信号至第n解码信号dec<1:n>的逻辑电平而执行加法运算和减法运算来产生第三内部地址信号bk3_add<1:n>。第三地址传输电路560可以通过第(2n+1)局部i/o线至第3n局部i/o线lio<(2n+1):3n>将第三内部地址信号bk3_add<1:n>输出到第三存储体800。

74.当刷新信号sr被禁止时,第四地址传输电路570可以根据复位信号rst、第四命令脉冲信号cmdp<4>以及第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第四内部地址信号bk4_add<1:n>。当刷新信号sr被使能时,第四地址传输电路570可以基于控制信号scon、通过根据第四命令脉冲信号cmdp<4>和第一解码信号至第n解码信号dec<1:n>的逻辑电平而执行加法运算和减法运算来产生第四内部地址信号bk4_add<1:n>。第四地址传输电路570可以通过第(3n+1)局部i/o线至第l局部i/o线lio<(3n+1):l>将第四内部地址信号bk4_add<1:n>输出到第四存储体800。

75.参照图7,脉冲发生电路510可以使用反相器iv41、iv42、iv43、iv44和iv45、或门or41和与非门nand41来实现。

76.在复位信号rst被使能成具有逻辑“高”电平的情况下,脉冲发生电路510可以产生第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>,所述第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>不管第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>以

及第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>如何都被禁止。

77.在控制信号scon被使能成具有逻辑“低”电平的情况下,脉冲发生电路510可以产生第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>,所述第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>包括在第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>或第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>被使能成具有逻辑“高”电平时创建的脉冲。

78.在控制信号scon被禁止为具有逻辑“高”电平的情况下,脉冲发生电路510可以产生第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>,所述第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>不管第一存储体激活地址信号至第四存储体激活地址信号bk_a<1:4>以及第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>如何都被禁止。

79.尽管图7示出了具有一个电路的脉冲发生电路510,但是根据第一命令脉冲信号至第四命令脉冲信号cmdp<1:4>中包括的比特位的数目,该脉冲发生电路510实际上可以使用四个电路来实现,该四个电路中的每个电路具有与图7所示的电路相同的配置。

80.参考图8,控制信号发生电路520可以包括传输控制信号发生电路521和信号传输电路522。

81.传输控制信号发生电路521可以使用与非门nand51和反相器iv51来实现。当激活信号act具有逻辑“高”电平并且刷新信号sr具有逻辑“高”电平时,传输控制信号发生电路521可以产生具有逻辑“高”电平的传输控制信号tcon。当激活信号act具有逻辑“高”电平并且刷新信号sr具有逻辑“低”电平时,传输控制信号发生电路521可以产生具有逻辑“低”电平的传输控制信号tcon。

82.信号传输电路522可以使用反相器iv52、iv53、iv54、iv55和iv56、或非门nor51、与非门nand51和传输门t51来实现。当具有逻辑“高”电平的复位信号rst被输入时,信号传输电路522可以产生被禁止为具有逻辑“高”电平的控制信号scon。当在传输控制信号tcon被使能之后禁止传输控制信号tcon时,信号传输电路522可以将由复位信号rst禁止的控制信号scon反相以产生被使能成具有逻辑“低”电平的控制信号scon。当传输控制信号tcon的逻辑电平从逻辑“高”电平改变为逻辑“低”电平时,信号传输电路522可以产生被使能成具有逻辑“低”电平的控制信号scon。

83.参考图9和图10,第一地址传输电路540可以包括第一算术电路541、第二算术电路542、第三算术电路543、

…

、和第n算术电路544。

84.第一算术电路541可以包括第一加法/减法信号发生电路5411和第一选择/传输电路5412。

85.第一加法/减法信号发生电路5411可以使用pmos晶体管p61、nmos晶体管n61和n62、反相器iv60、iv61、iv62和iv63以及与门and61和and62来实现。当复位信号rst被使能成具有逻辑“高”电平时,第一加法/减法信号发生电路5411可以产生具有逻辑“低”电平的第一预字线信号pwi<1>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第一解码信号dec<1>具有逻辑“高”电平时,第一加法/减法信号发生电路5411可以产生具有逻辑“高”电平的第一预字线信号pwi<1>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第一解码信号dec<1>具有逻辑“低”电平时,第一加法/减法信号发生电路5411可以产生具有逻辑“低”电平的第一预字线信号pwi<1>。当控制信号scon被禁止成具有逻辑

“

高”电平时,第一加法/减法信号发生电路5411可以反相缓冲第一预字线信号pwi<1>以产生第一减法信号mn<1>。当控制信号scon被禁止成具有逻辑“高”电平时,第一加法/减法信号发生电路5411可以缓冲第一预字线信号pwi<1>以产生第一加法信号mp<1>。

86.第一选择/传输电路5412可以使用反相器iv64、iv65、iv66、iv67和iv68以及传输门t61和t62来实现。当刷新信号sr被使能成具有逻辑“高”电平时,第一选择/传输电路5412可以缓冲第一预字线信号pwi<1>以产生第一内部地址信号bk1_add<1:n>的第一比特位信号bk1_add<1>。当刷新信号sr被禁止成具有逻辑“低”电平时,第一选择/传输电路5412可以反相缓冲第一预字线信号pwi<1>以产生第一内部地址信号bk1_add<1:n>的第一比特位信号bk1_add<1>。

87.第二算术电路542可以包括第二加法/减法信号发生电路5421和第二选择/传输电路5422。

88.第二加法/减法信号发生电路5421可以使用pmos晶体管p71、nmos晶体管n71和n72、反相器iv70、iv71和iv72以及与门and71和and72来实现。当复位信号rst被使能成具有逻辑“高”电平时,第二加法/减法信号发生电路5421可以产生具有逻辑“低”电平的第二预字线信号pwi<2>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第二解码信号dec<2>具有逻辑“高”电平时,第二加法/减法信号发生电路5421可以产生具有逻辑“高”电平的第二预字线信号pwi<2>。当第一命令脉冲信号cmdp<1>被使能成逻辑“高”电平且第二解码信号dec<2>具有逻辑“低”电平时,第二加法/减法信号发生电路5421可以产生具有逻辑“低”电平的第二预字线信号pwi<2>。当第一减法信号mn<1>被使能成具有逻辑“高”电平时,第二加法/减法信号发生电路5421可以缓冲第二预字线信号pwi<2>以产生第二减法信号mn<2>。当第一加法信号mp<1>被使能成具有逻辑“高”电平时,第二加法/减法信号发生电路5421可以缓冲第二预字线信号pwi<2>以产生第二加法信号mp<2>。

89.第二选择/传输电路5422可以使用反相器iv73、iv74、iv75、iv76、iv77和iv78、或门or71以及传输门t71、t72和t73来实现。当第二加法信号mp<2>被使能成具有逻辑“高”电平时,第二选择/传输电路5422可以反相缓冲由第三算术电路543产生的第三预字线信号pwi<3>,以产生第一内部地址信号bk1_add<1:n>的第二比特位信号bk1_add<2>。当第二减法信号mn<2>被使能成具有逻辑“高”电平时,第二选择/传输电路5422可以反相缓冲由第一算术电路541产生的第一预字线信号pwi<1>,以产生第一内部地址信号bk1_add<1:n>的第二比特位信号bk1_add<2>。当刷新信号sr和第二预字线信号pwi<2>中的一个被产生为具有逻辑“低”电平时,第二选择/传输电路5422可以反相缓冲第二预字线信号pwi<2>以产生第一内部地址信号bk1_add<1:n>的第二比特位信号bk1_add<2>。

90.第三算术电路543可以包括第三加法/减法信号发生电路5431和第三选择/传输电路5432。

91.第三加法/减法信号发生电路5431可以使用pmos晶体管p81、nmos晶体管n81和n82、反相器iv80、iv81和iv82以及与门and81和and82来实现。当复位信号rst被使能成具有逻辑“高”电平时,第三加法/减法信号发生电路5431可以产生具有逻辑“低”电平的第三预字线信号pwi<3>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第三解码信号dec<3>具有逻辑“高”电平时,第三加法/减法信号发生电路5431可以产生具有逻辑“高”电平的第三预字线信号pwi<3>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平

且第三解码信号dec<3>具有逻辑“低”电平时,第三加法/减法信号发生电路5431可以产生具有逻辑“低”电平的第三预字线信号pwi<3>。当第二减法信号mn<2>被使能成具有逻辑“高”电平时,第三加法/减法信号发生电路5431可以缓冲第三预字线信号pwi<3>以产生第三减法信号mn<3>。当第二加法信号mp<2>被使能成具有逻辑“高”电平时,第三加法/减法信号发生电路5431可以缓冲第三预字线信号pwi<3>以产生第三加法信号mp<3>。

92.第三选择/传输电路5432可以使用反相器iv83、iv84、iv85、iv86、iv87和iv88、或门or81以及传输门t81、t82和t83来实现。当第三加法信号mp<3>被使能成逻辑“高”电平时,第三选择/传输电路5432可以反相缓冲由第四运算电路(未示出)产生的第四预字线信号pwi<4>,以产生第一内部地址信号bk1_add<1:n>的第三比特位信号bk1_add<3>。当第三减法信号mn<3>被使能成具有逻辑“高”电平时,第三选择/传输电路5432可以反相缓冲由第二算术电路542产生的第二预字线信号pwi<2>,以产生第一内部地址信号bk1_add<1:n>的第三比特位信号bk1_add<3>。当刷新信号sr和第三预字线信号pwi<3>中的一个被产生为具有逻辑“低”电平时,第二选择/传输电路5432可以反相缓冲第三预字线信号pwi<3>以产生第一内部地址信号bk1_add<1:n>的第三比特位信号bk1_add<3>。

93.第n算术电路544可以包括第n加法/减法信号发生电路5441和第n选择/传输电路5442。

94.第n加法/减法信号发生电路5441可以使用pmos晶体管p91、nmos晶体管n91和n92、反相器iv90、iv91和iv92以及与门and91和and92来实现。当复位信号rst被使能成具有逻辑“高”电平时,第n加法/减法信号发生电路5441可以产生具有逻辑“低”电平的第n预字线信号pwi<n>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第n解码信号dec<n>具有逻辑“高”电平时,第n加法/减法信号发生电路5441可以产生具有逻辑“高”电平的第n预字线信号pwi<n>。当第一命令脉冲信号cmdp<1>被使能成具有逻辑“高”电平且第n解码信号dec<n>具有逻辑“低”电平时,第n加法/减法信号发生电路5441可以产生具有逻辑“低”电平的第n预字线信号pwi<n>。当第(n-1)减法信号mn<n-1>被使能成具有逻辑“高”电平时,第n加法/减法信号发生电路5441可以缓冲第n预字线信号pwi<n>以产生第n减法信号mn<n>。当第(n-1)加法信号mp<n-1>被使能成具有逻辑“高”电平时,第n加法/减法信号发生电路5441可以缓冲第n预字线信号pwi<n>以产生第n加法信号mp<n>。

95.第n选择/传输电路5442可以使用反相器iv93、iv94、iv95、iv96、iv97和iv98、或门or91以及传输门t91、t92和t93来实现。当第n加法信号mp<n>被使能成具有逻辑“高”电平时,第n选择/传输电路5442可以反相缓冲由第一算术电路541产生的第一预字线信号pwi<1>,以产生第一内部地址信号bk1_add<1:n>的第n比特位信号bk1_add<n>。当第n减法信号mn<n>被使能成具有逻辑“高”电平时,第n选择/传输电路5442可以反相缓冲由第(n-1)算术电路(未示出)产生的第(n-1)预字线信号pwi<n-1>,以产生第一内部地址信号bk1_add<1:n>的第n比特位信号bk1_add<n>。当刷新信号sr和第n预字线信号pwi<n>中的一个被产生为具有逻辑“低”电平时,第n选择/传输电路5442可以反相缓冲第n预字线信号pwi<n>以产生第一内部地址信号bk1_add<1:n>的第n比特位信号bk1_add<n>。

96.另外,图6中示出的第二地址传输电路至第四地址传输电路550、560和570中的每一个可以使用与图9和图10中示出的第一地址传输电路540基本相同的电路(除了其输入/输出(i/o)信号之外)来实现。因此,在下文中将省略第二地址传输电路至第四地址传输电

路550、560和570的详细描述。

97.在下文中,将参考图11描述针对半导体器件1中包括的第一存储体600的智能刷新操作。

98.在时间点“t1”处,命令解码器100可以对命令cmd进行解码以产生具有逻辑“高”电平的激活信号act。

99.在时间点“t2”处,命令解码器100可以命令cmd进行解码以产生包括具有逻辑“高”电平的第一脉冲的刷新信号sr。

100.存储体地址发生电路200可以接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>,以基于具有逻辑“高”电平的激活信号act和刷新信号sr来产生具有逻辑“高”电平的第一存储体刷新地址信号bk_r<1>。第一存储体刷新地址信号bk_r<1>可以通过第二全局i/o线gio<2>从存储体地址发生电路200输出。

101.目标地址发生电路300可以基于具有逻辑“高”电平的刷新信号sr来产生第一目标地址信号至第m目标地址信号rh_add<1:m>。

102.地址输入电路400可以接收第一目标地址信号至第m目标地址信号rh_add<1:m>,以基于刷新信号sr和第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>来产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。第一锁存地址信号至第m锁存地址信号ladd<1:m>可以通过第九全局i/o线至第k全局i/o线gio<9:k>从地址输入电路400输出。

103.内部地址发生电路500的第一地址传输电路540可以根据第一命令脉冲信号cmdp<1>和第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第一预字线信号至第n预字线信号pwi<1:n>,并且可以执行第一预字线信号至第n预字线信号pwi<1:n>的加法运算(wl+1)以产生第一内部地址信号bk1_add<1:n>。

104.第一存储体600中包括的第一字线至第n字线wl<1:n>中的一个可以通过第一内部地址信号bk1_add<1:n>而被激活。在这种情况下,被激活的字线指紧接在由第一目标地址信号至第m目标地址信号rh_add<1:m>激活的字线之后的字线(wl+1)。

105.在时间点“t3”处,因为激活信号act保持逻辑“高”电平并且刷新信号sr的第一脉冲被禁止成具有逻辑“低”电平,所以控制信号发生电路520可以产生被禁止成具有逻辑“高”电平的控制信号scon。

106.内部地址发生电路500的第一地址传输电路540可以根据第一命令脉冲信号cmdp<1>和第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第一预字线信号至第n预字线信号pwi<1:n>,并且可以执行第一预字线信号至第n预字线信号pwi<1:n>的减法运算(wl-1)以产生第一内部地址信号bk1_add<1:n>。

107.第一存储体600中包括的第一字线至第n字线wl<1:n>中的一个可以通过第一内部地址信号bk1_add<1:n>而被激活。在这种情况下,被激活的字线指在由第一目标地址信号至第m目标地址信号rh_add<1:m>激活的字线之前的字线(wl-1)。

108.根据具有前述配置的半导体器件1,在智能刷新操作期间,半导体器件1的外围电路可以从目标地址信号产生锁存地址信号,并且可以通过全局i/o线将锁存地址信号输出到半导体器件1的核心电路。半导体器件1的核心电路可以在智能刷新操作期间顺序地执行锁存地址信号的加法运算和减法运算。因此,不需要额外的全局i/o线来将用于执行加法运算和减法运算的锁存地址信号传送到核心电路。因此,能够减小半导体器件1的布局面积。

此外,由于在半导体器件1中不需要额外的全局i/o线,因此可以防止加法运算和减法运算的错误。因此,可以有效地执行智能刷新操作。

109.在下文中,将参照图12来描述针对半导体器件1中包括的第一存储体500的另一种智能刷新操作。

110.在时间点“t11”处,命令解码器100可以对命令cmd进行解码以产生具有逻辑“高”电平的激活信号act。

111.在时间点“t12”处,命令解码器100可以对命令cmd进行解码以产生包括具有逻辑“高”电平的第一脉冲的刷新信号sr。

112.存储体地址发生电路200可以接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>,以基于具有逻辑“高”电平的激活信号act和刷新信号sr来产生具有逻辑“高”电平的第一存储体刷新地址信号bk_r<1>。第一存储体刷新地址信号bk_r<1>可以通过第二全局i/o线gio<2>从存储体地址发生电路200输出。

113.目标地址发生电路300可以基于具有逻辑“高”电平的刷新信号sr来产生第一目标地址信号至第m目标地址信号rh_add<1:m>。

114.地址输入电路400可以接收第一目标地址信号至第m目标地址信号rh_add<1:m>,以基于刷新信号sr和第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>来产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。第一锁存地址信号至第m锁存地址信号ladd<1:m>可以通过第九全局i/o线至第k全局i/o线gio<9:k>从地址输入电路400输出。

115.内部地址发生电路500的第一地址传输电路540可以根据第一命令脉冲信号cmdp<1>和第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第一预字线信号至第n预字线信号pwi<1:n>,并且可以执行第一预字线信号至第n预字线信号pwi<1:n>的减法运算(wl-1)以产生第一内部地址信号bk1_add<1:n>。

116.第一存储体600中包括的第一字线至第n字线wl<1:n>中的一个可以通过第一内部地址信号bk1_add<1:n>而被激活。在这种情况下,被激活的字线指在由第一目标地址信号至第m目标地址信号rh_add<1:m>激活的字线之前的字线(wl-1)。

117.在时间点“t3”处,因为激活信号act保持逻辑“高”电平并且刷新信号sr的第一脉冲被禁止成具有逻辑“低”电平,所以控制信号发生电路520可以产生被禁止成具有逻辑“高”电平的控制信号scon。

118.内部地址发生电路500的第一地址传输电路540可以根据第一命令脉冲信号cmdp<1>和第一解码信号至第n解码信号dec<1:n>的逻辑电平来产生第一预字线信号至第n预字线信号pwi<1:n>,并且可以执行第一预字线信号至第n预字线信号pwi<1:n>的加法运算(wl+1)以产生第一内部地址信号bk1_add<1:n>。

119.第一存储体600中包括的第一字线至第n字线wl<1:n>中的一个可以通过第一内部地址信号bk1_add<1:n>而被激活。在这种情况下,被激活的字线指紧接在由第一目标地址信号至第m目标地址信号rh_add<1:m>激活的字线之后的字线(wl+1)。

120.根据具有前述配置的半导体器件1,在智能刷新操作期间,半导体器件1的外围电路可以从目标地址信号产生锁存地址信号,并且可以通过全局i/o线将锁存地址信号输出到半导体器件1的核心电路。半导体器件1的核心电路可以在智能刷新操作期间顺序地执行锁存地址信号的减法运算和加法运算。因此,不需要额外的全局i/o线来将用于执行加法运

算和减法运算的锁存地址信号传送到核心电路。因此,能够减小半导体器件1的布局面积。此外,由于在半导体器件1中不需要额外的全局i/o线,因此可以防止加法运算和减法运算的错误。因此,可以有效地执行智能刷新操作。

121.下文中将参考图13描述根据本公开的实施例的刷新方法。

122.命令解码器100可以对由外部设备提供的命令cmd进行解码以产生被使能以执行智能刷新操作的激活信号act,并且可以产生包括在智能刷新操作期间创建的第一脉冲的刷新信号sr以执行智能刷新操作进入步骤s1。

123.存储体地址发生电路200可以基于激活信号act和刷新信号sr的第一脉冲来接收第(m+1)地址信号和第(m+2)地址信号add<(m+1):(m+2)>,以执行用于产生第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>的存储体地址生成步骤s2。

124.目标地址发生电路300可以基于刷新信号sr的第一脉冲来产生第一目标地址信号至第m目标地址信号rh_add<1:m>。

125.地址输入电路400可以基于刷新信号sr的第一脉冲和第一存储体刷新地址信号至第四存储体刷新地址信号bk_r<1:4>来从第一目标地址信号至第m目标地址信号rh_add<1:m>产生第一锁存地址信号至第m锁存地址信号ladd<1:m>。

126.内部地址发生电路500可以执行锁存地址检测步骤s31,该锁存地址检测步骤s31基于激活信号act和刷新信号sr的第一脉冲来检测第一锁存地址信号至第m锁存地址信号ladd<1:m>的逻辑电平。

127.当由第一锁存地址信号至第m锁存地址信号ladd<1:m>产生的第一解码信号至第n解码信号dec<1:n>的比特位信号中的一个具有逻辑“高”电平时,内部地址发生电路500可以执行加法运算(参见步骤s32)。内部地址发生电路500可以执行加法运算步骤s32,以执行用于产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>、和bk4_add<1:n>的地址传输步骤s34。另外,当由第一锁存地址信号至第m锁存地址信号ladd<1:m>产生的第一解码信号至第n解码信号dec<1:n>的比特位信号中的一个具有逻辑“低”电平时,内部地址发生电路500可以执行减法运算(参见步骤s33)。

128.核心电路20可以基于由加法运算步骤s32产生的第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>来执行智能刷新操作执行步骤s35。可替代地,核心电路20可以基于由减法运算步骤s33产生的第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<1:n>来执行智能刷新操作执行步骤s35。

129.锁存地址检测步骤s31、加法运算步骤s32、减法运算步骤s33、地址传输步骤s34和智能刷新操作执行步骤s35可以构成内部地址生成步骤s3。

130.命令解码器100可以对由外部设备提供的命令cmd进行解码,以产生被使能的激活信号act和被禁止的刷新信号sr,以用于激活智能刷新模式。

131.内部地址发生电路500可以接收激活信号act和刷新信号sr以产生被禁止成具有逻辑“高”电平的控制信号scon。内部地址发生电路500可以通过基于被使能成具有逻辑“高”电平的控制信号scon来检测第一锁存地址信号至第m锁存地址信号ladd<1:m>的逻辑电平而再次执行地址传输步骤s34。内部地址发生电路500可以执行第一解码信号至第n解码信号dec<1:n>的减法运算s33。内部地址发生电路500可以执行减法运算s33以重新执行

用于产生第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>、和bk4_add<1:n>的地址传输步骤s34。当首先执行减法运算s33时,可以在执行减法运算s33之后执行加法运算s32。

132.核心电路20可以基于由减法运算步骤s33产生的第一内部地址信号至第四内部地址信号bk1_add<1:n>、bk2_add<1:n>、bk3_add<1:n>和bk4_add<:n>而再次执行智能刷新操作执行步骤s35。

133.根据具有前述配置的半导体器件1,在智能刷新操作期间,半导体器件1的外围电路可以从目标地址信号产生锁存地址信号,并且可以通过全局i/o线将锁存地址信号输出到半导体器件1的核心电路。半导体器件1的核心电路可以在智能刷新操作期间顺序地执行锁存地址信号的减法运算和加法运算。因此,不需要额外的全局i/o线来将用于执行加法运算和减法运算的锁存地址信号传送到核心电路。因此,能够减小半导体器件1的布局面积。此外,由于在半导体器件1中不需要额外的全局i/o线,因此可以防止加法运算和减法运算的错误。因此,可以有效地执行智能刷新操作。

134.参考图1至图12描述的半导体器件1可以被应用于包括存储系统、图形系统、计算系统、移动系统等的电子系统。例如,如图14所示,根据实施例的电子系统1000可以包括数据储存电路1001、存储器控制器1002、缓冲存储器1003和输入/输出(i/o)接口1004。

135.根据从存储器控制器1002产生的控制信号,数据储存电路1001可以储存从存储器控制器1002输出的数据,或者可以将所储存的数据读取并输出到存储器控制器1002。数据储存电路1001可以包括图1所示的半导体器件1。另外,数据储存电路1001可以包括即使在其电源被中断的情况下也可以保留其储存的数据的非易失性存储器。非易失性存储器可以是诸如nor型快闪存储器或nand型快闪存储器之类的快闪存储器、相变随机存取存储器(pram)、电阻式随机存取存储器(rram)、自旋转移转矩随机存取存储器(sttram)、磁性随机存取存储器(mram)等。

136.存储器控制器1002可以通过i/o接口1004接收从外部设备(例如,主机设备)输出的命令,并且可以对从主机设备输出的命令进行解码,以控制用于将数据输入到数据储存电路1001或缓冲存储器1003或者用于输出储存在数据储存电路1001或缓冲存储器1003中的数据的操作。尽管图14用单个框示出了存储器控制器1002,但是存储器控制器1002可以包括用于控制由非易失性存储器构成的数据储存电路1001的一个控制器和用于控制由易失性存储器构成的缓冲存储器1003的另一个控制器。

137.缓冲存储器1003可以暂时储存由存储器控制器1002处理的数据。也就是说,缓冲存储器1003可以暂时储存从数据储存电路1001输出或输入到数据储存电路1001的数据。缓冲存储器1003可以根据控制信号来储存从存储器控制器1002输出的数据。缓冲存储器1003可以读取所储存的数据并将其输出到存储器控制器1002。缓冲存储器1003可以包括易失性存储器,诸如动态随机存取存储器(dram)、移动dram或静态随机存取存储器(sram)。

138.i/o接口1004可以将存储器控制器1002物理地和电气地连接到外部设备(即,主机设备)。因此,存储器控制器1002可以通过i/o接口1004接收从外部设备(即,主机设备)提供的数据和控制信号,并且可以通过i/o接口1004将从存储器控制器1002产生成的数据输出到外部设备(即,主机设备)。也就是说,电子系统1000可以通过i/o接口1004与主机设备通信。i/o接口1004可以包括诸如以下各种接口协议中的任意一种:通用串行总线(usb)、多媒

体卡(mmc)、外围组件快速互连(pci-e)、串行附接的scsi(sas)、串行at附件(sata)、并行at附件(pata)、小型计算机系统接口(scsi)、增强型小型设备接口(esdi)和集成驱动电子设备(ide)。

139.电子系统1000可以被用作主机的辅助储存设备或外部储存设备。电子系统1000可以包括固态盘(ssd)、usb存储器、安全数字(sd)卡、迷你安全数字(msd)卡、微型安全数字(微型sd)卡、安全数字高容量(sdhc)卡、记忆棒卡、智能媒体(sm)卡、多媒体卡(mmc)、嵌入式多媒体卡(emmc)、紧凑型闪存(cf)卡等。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1